在高速 IC 設計過程中,信號完整性(SI)分析—特別是串擾噪聲與延遲分析—是確保電路高質量和可靠性不可或缺的步驟。

1、為什麼信號完整性分析如此關鍵?

信號完整性分析確保信號在芯片內部不遭失真、無誤傳播,直接影響 IC 的性能、功能與可靠性。串擾噪聲(crosstalk noise)和串擾延遲(crosstalk delay)是兩個主要挑戰:

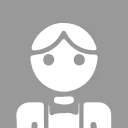

串擾噪聲:當“施加路徑”(aggressor)線路切換時,耦合會在相鄰“受害路徑”(victim)中引入干擾,可能導致邏輯錯誤或功能抖動。

串擾延遲:串擾效應不僅僅是噪聲,還會加快或放慢信號,造成時序違規,破壞時序閉合。

深入 SI 分析幫助我們精準定位問題、修復錯誤,為後續設計階段提供堅實基礎。

2、四大關鍵技術與工具詳解

I. 串擾噪聲分析(Crosstalk Noise Analysis)

Case Study

某半導體公司在 post-route 階段使用 Cadence CeltIC 工具分析串擾噪聲,檢測並修復因串擾導致的 glitch 與 delay 違規問題,並生成 buffer 插入、網間距調整等修復文件,顯著提升設計質量。

實現策略:

使用 CeltIC 等工具進行細粒度噪聲分析。

採用緩衝器插入、信號網隔離、屏蔽等修復策略減少串擾干擾。

II. 串擾延遲分析(Crosstalk Delay Analysis)

Case Study

某設計團隊採用 Synopsys PrimeTime-SI 工具,將其整合進靜態時序分析流程,以準確評估串擾引發的延遲變動,保證在模塊級及全芯片級都滿足時序要求。

實施建議:

在靜態時序分析中納入串擾延遲分析路徑。

使用 PrimeTime-SI 等工具,生成包含串擾影響的 SDF 文件進行閉環驗證。

III. 分層 SI 分析(Hierarchical SI Analysis)

實踐方式

大型 SoC 設計中,將 SI 分析任務按模塊—子模塊分層進行,在保證精度的同時大幅提升驗證效率。常見做法是利用工具生成每個 block 的抽象模型,再用於頂層 SI 驗證。

優勢:

支撐複雜系統級分析;

在早期獲得模塊性能反饋,降低整體驗證負擔。

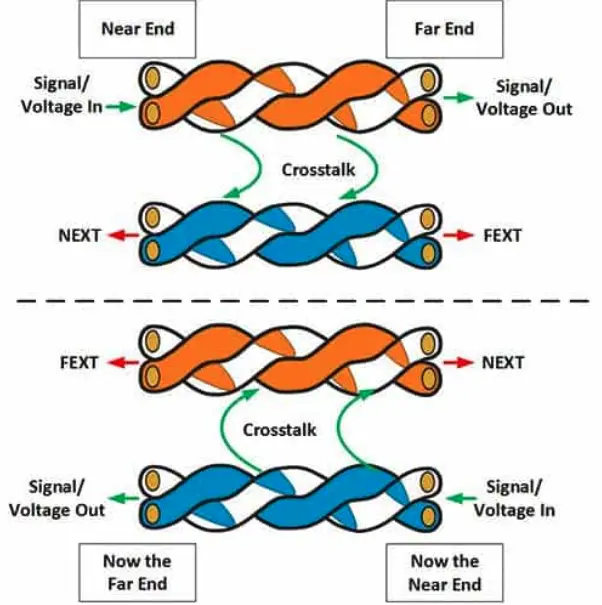

IV. 物理感知 SI 分析(Physically Aware SI Analysis)

特點

將物理布圖信息(placement/routing)納入 SI 分析,引入佈局耦合、走線密度等物理因素,顯著提升噪聲與延遲預測的準確性。

工具支持:

Synopsys Hercules 等工具支持將物理約束直接集成進 SI 分析流程,從而優化電源分配與信號清晰度。

3、戰略意義與核心優勢一覽

技術方向 優勢摘要

串擾噪聲分析 精確檢測 glitch / 毫伏級干擾,避免功能異常

串擾延遲分析 保證時序精度,防止時序違例

分層 SI 分析 提高複雜 SoC 驗證效率,模塊級反饋快

物理感知 SI 分析 更貼合物理實現,提升時序精度與整體性能保障

融合這些先進技術,幫助 IC 設計人員全方位提升信號完整性驗證能力,縮短開發週期,降低返工成本。

4、學習加速:EDA Academy 助你成為 SI 專業高手

若你希望系統掌握 SI 分析與優化前沿方法,EDA Academy(www.eda-academy.com) 是你的最佳選擇:

擁有 海量、專業、全面、最新 的網課,覆蓋串擾噪聲、延遲分析、分層方法與物理感知分析等主題;

註冊為導師,傳授你自己的經驗與知識,成為課程設計者;

用郵箱即可 免費訂閲其 newsletter,定期獲取最新熱點與乾貨;

加入 銷售聯盟計劃,推薦課程即可獲得 20%–50% 的佣金,讓學習更具收益價值。

5、從技術到平台,共築 SI 精英之路

從串擾噪聲、延遲分析,到分層與物理感知 SI 方法,再到 EDA Academy 的學習與成長通道,本文為你鋪就一條完整的專業進階路徑。掌握先進 SI 技術,將極助你成為高質量 IC 設計的可靠守護者;加入 EDA Academy,開啓你的職場“加速器”。