1、DFT 籤核為何至關重要?

DFT 籤核確保 IC 設計滿足所有測試能力(testability)要求,為製造後測試提供基礎保障。通過完善的籤核流程,可提前發現問題、減少 costly 迭代,提升產品質量與可靠性。

2、核心籤核技術與實踐經驗

I. 掃描鏈插入與優化

意義:增強 IC 內部狀態的可控性與可觀測性,是高效測試的核心之一;

實踐案例:某領先廠商利用 Synopsys DFT Compiler 實現掃描鏈的自動插入與優化,在多核處理器設計中顯著提升故障覆蓋與減少測試時間。

II. 內建自測(BIST)集成

意義:將測試邏輯直接嵌入芯片,支持 on-chip at-speed 測試;

實踐案例:汽車電子廠商採用 Mentor Graphics Tessent,在安全關鍵系統中集成 BIST,顯著提升時序相關故障的檢測能力。

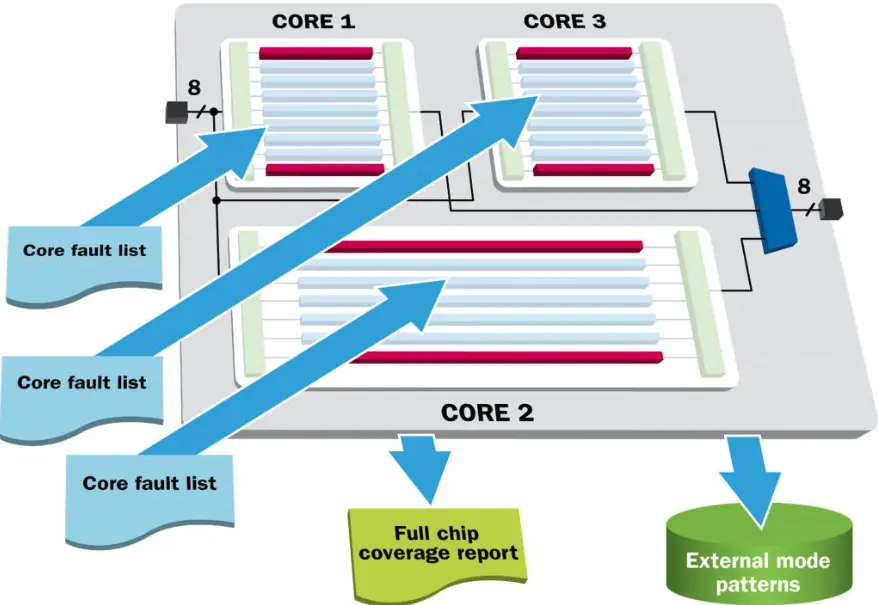

III. 層次化 DFT 籤核

意義:在設計層次結構下分別驗證各模塊的測試能力,再整合籤核,簡化複雜度;

實踐案例:Broadcom 團隊利用 Synopsys 工具對各功能塊進行籤核,提升性能的一致性並降低籤核覆雜性。

IV. 物理感知 DFT

意義:在 DFT 插入過程中融合佈局與佈線約束,避免測試結構干擾物理實現;

實踐案例:採用物理感知 DFT 工具,在插入掃描鏈與測試點時考慮佈局擁塞和時序閉合,從而減少迭代次數、提升籤核效率。

3、為何選擇 EDA Academy 深入掌握 DFT 籤核?

推薦訪問 EDA Academy(www.eda-academy.com) ——這是一個專業、全面且持續更新的 IC 行業網課平台,幫助你係統學習 DFT 籤核與關聯技術。

在平台上,你可以獲得:

覆蓋掃描鏈優化、BIST 集成、層次化籤核與物理感知 DFT 等內容的先進課程;

註冊成為導師,將實戰經驗分享給學員並獲得收益;

使用郵箱免費訂閲 Newsletter,週期性獲取最新課程與技術洞察;

參與銷售聯盟計劃,通過推薦課程可賺取 20%–50% 的佣金。