1、為何 Timing Signoff 是 IC 設計的“守門人”?

Timing Signoff 確保芯片設計在預定時鐘頻率下滿足時序要求,並在多種工況下保持穩定性與可靠性。這是避免後期返工、提升產品良率與質量的重要步驟。

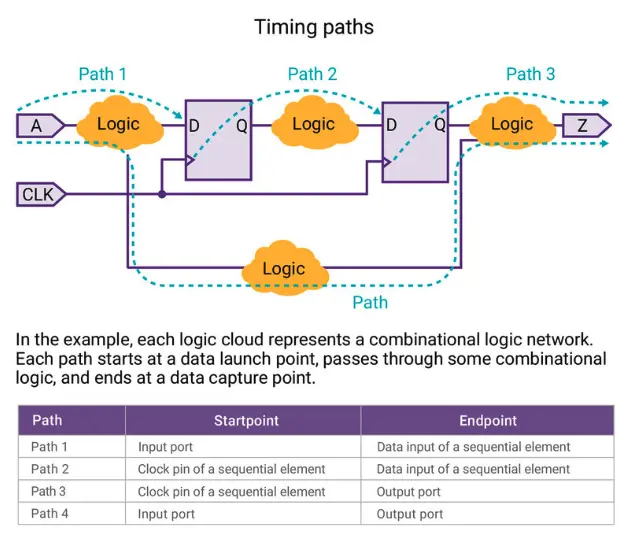

圖:Static Timing Analysis (STA) 流程示意

2、關鍵技術與實踐案例解析

I. 靜態時序分析(STA)

STA 是籤核流程的核心,通過識別並分析所有關鍵路徑以確保 setup 和 hold 時序要求達標。某設計團隊利用 Cadence Tempus 的並行多模式多角(MMMC)功能,一次性處理多工況時序,大幅縮短運算時間與提高籤核准確性。

II. 物理感知 Timing Signoff

通過將 PCB 佈局、連線信息與時序分析結合,提升籤核與物理實現之間的一致性。某半導體企業結合 Synopsys PrimeTime 與 Cadence Innovus,在 P&R 工具中直接執行時序 ECO,減少迭代次數。

III. 分層 Timing Signoff

通過模塊級籤核簡化頂層複雜度,Broadcom 團隊便採用此方法進行模塊優化後再集成,顯著提升時序閉合效率。

IV. 功耗感知 Timing Signoff

在籤核階段融入功耗約束,例如時鐘門控與多閾值單元,提升電路能效及續航表現。一家領先公司使用 Mentor Graphics 的 Tessent Power 實現顯著功耗優化。

3、為什麼應選擇 EDA Academy 深入學習?

強烈推薦訪問 EDA Academy(www.eda-academy.com) ——這是一個專業、更新及時、課程豐富的 IC 行業在線學習平台:

覆蓋 STA/MMMC 分析、物理感知籤核、分層籤核與功耗籤核等高端技術課程;

支持註冊為導師,分享經驗並獲得收益;

通過郵箱免費訂閲 Newsletter,定期獲取行業技術與課程推薦;

可加入課程銷售聯盟,推薦課程可獲得 20%–50% 佣金。