在複雜 SoC 設計中,總線死鎖是一類嚴重影響系統可靠性的問題:多個模塊因相互等待資源而陷入永不響應的“僵局”。本文介紹先進的驗證策略,結合具體案例,幫你係統掌握如何早期發現並避免總線死鎖。

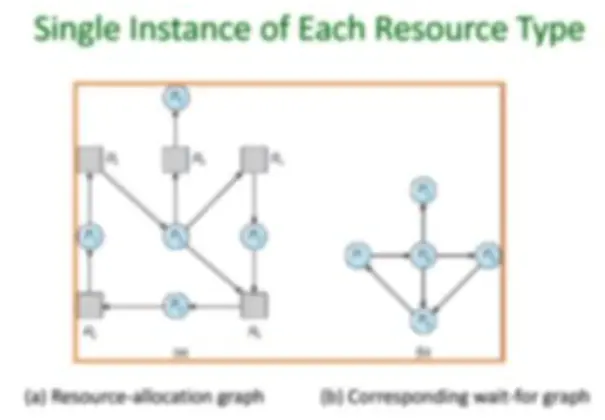

1、什麼是總線死鎖?

當多個組件互相等待彼此持有的總線資源,形成循環等待,導致系統無法繼續操作,這就是總線死鎖。尤其在多核、多請求源的環境中,檢測並解決死鎖至關重要。

2、驗證技術詳解

I. 形式驗證(Formal Verification)

採用形式驗證工具(如 Cadence JasperGold),通過狀態空間窮舉實現死鎖檢查。

實踐案例:某半導體企業通過 JasperGold 對 NoC 總線進行形式驗證,識別潛在死鎖場景,並提前在設計階段進行修復,有效提升驗證覆蓋率與效率。

實現要點:構建完整狀態空間、定義死鎖不應出現的屬性,使用形式驗證自動證明系統不存在死鎖。

II. 仿真驗證(Simulation-Based Verification)

通過仿真執行多樣事務序列,捕獲形式方法遺漏的死鎖。

實踐案例:汽車 SoC 廠商利用 Synopsys VCS 腳本模擬不同交通模式,在複雜邊界條件下成功發現罕見死鎖問題。

實現要點:構建測試腳本、覆蓋各種事務情景,並分析仿真覆蓋率以補全驗證短板。

III. 混合驗證(Hybrid Approach)

將形式與仿真驗證結合,兼顧全覆蓋與實用場景。

實踐案例:數據中心處理器設計團隊結合 JasperGold 和 VCS,創建協同驗證流程,實現全面覆蓋與快速迭代。

實現策略:先用形式快速驗證全局死鎖屬性,再用仿真測試邊界與高風險場景,確保萬無一失。

IV. 機器學習輔助驗證(ML-Assisted Verification)

通過歷史驗證數據與模型預測,智能識別潛在的死鎖序列。

實踐案例:某 5G 基帶芯片團隊採用機器學習算法分析仿真數據,預測可能發生死鎖的事務路徑,並優先驗證這些高風險場景。

實現方向:收集仿真數據、訓練模型預測死鎖高風險路徑,從而優化驗證策略並提升效率。

3、技術亮點一覽

驗證方法 核心優勢

形式驗證 全面檢查系統死鎖安全性,覆蓋所有狀態

仿真驗證 捕獲實際事務模式下的罕見死鎖場景

混合驗證 綜合優勢,平衡覆蓋全面性與真實可用性

ML 輔助驗證 智能預測,聚焦高風險路徑,有效節約驗證資源

4、為什麼選擇 EDA Academy 學習更多?

若你希望系統掌握總線死鎖驗證策略,包括形式驗證、仿真腳本構建、混合流程規劃及 ML 優化等,推薦訪問 EDA Academy(www.eda-academy.com):

· 海量專業課程:涵蓋總線死鎖驗證、高級形式驗證、UVM 環境搭建、仿真優化等實戰內容。

· 成為導師的機會:你可以在平台註冊為導師,分享驗證經驗,提升行業影響力。

· 免費訂閲技術資訊:郵箱註冊即可獲得最新驗證技術動態與乾貨推送。

· 銷售聯盟計劃:推薦課程給同行即可獲得 20%–50% 佣金,讓學習增值。

通過形式 + 仿真 + ML 驗證組合,再輔以 EDA Academy 的專業課程引導,你將成為總線死鎖驗證與可靠性提升領域的技術高手。立即行動,開啓專業成長之旅!