“物理驗證是通往 tape-out 的最後一關。”

當工藝推進至 7 nm、5 nm 乃至更先進節點,設計規則變得愈發複雜、模塊層級更多、混合信號/3D 封裝挑戰加劇。此時, DRC (Design Rule Check) 與 LVS (Layout Versus Schematic) 這兩項物理驗證工作不僅是良率保障,更是與 foundry 簽入流程中不可繞開的一環。選對工具,能讓你少走彎路、快下 mask。

- 工具一覽

Siemens Calibre

Calibre 長期以來在 DRC/LVS 領域享有“行業標準”之稱。其工具套件包括 nmDRC、nmLVS 等,被大量 foundry 用作籤核平台。

優點在於:籤核 rule-deck 一般首先在 Calibre 上成熟、foundry 對 Calibre 的 支持最早且最廣。這縮短了“為什麼同樣規則在不同工具表現不一致”的調試循環。

適用場景:你在領先節點(如 5 nm/3 nm)設計、且 foundry 驗核 deck 基於 Calibre。

需要注意:如果你設計流程偏向“在 P&R 內部就想早驗早修”,但只用 Calibre 做傳統批量籤核,可能會錯過“在設計進行中實時反饋”的機會。

Synopsys IC Validator (ICV)

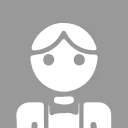

IC Validator 是 Synopsys 專注於物理驗證的解決方案,其特色為與 Synopsys 的 P&R 工具(如 ICC2/Fusion)緊密集成。

優勢在於:能在設計/實現階段就進行實時或近實時的 DRC 檢查(例如 Live DRC inside ICC2),避免等到最後才發現問題而返工。

適用場景:你主要用 Synopsys 的 P&R 套件,且希望將 DRC/LVS 反饋週期前置。

注意事項:若 foundry 驗核 deck 本身在 Calibre 上更成熟,仍需確認規則一致性。

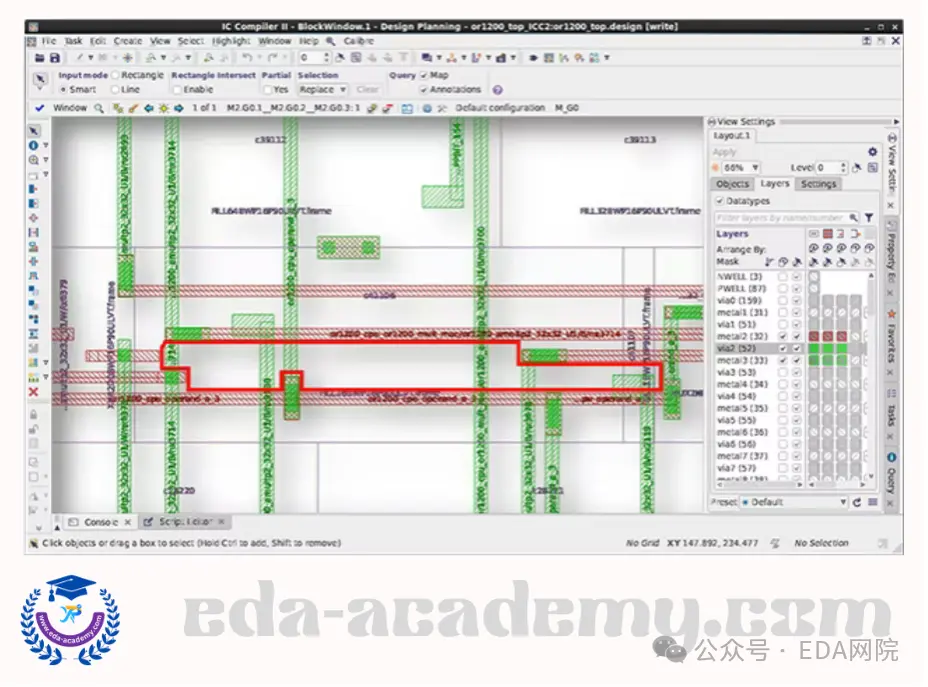

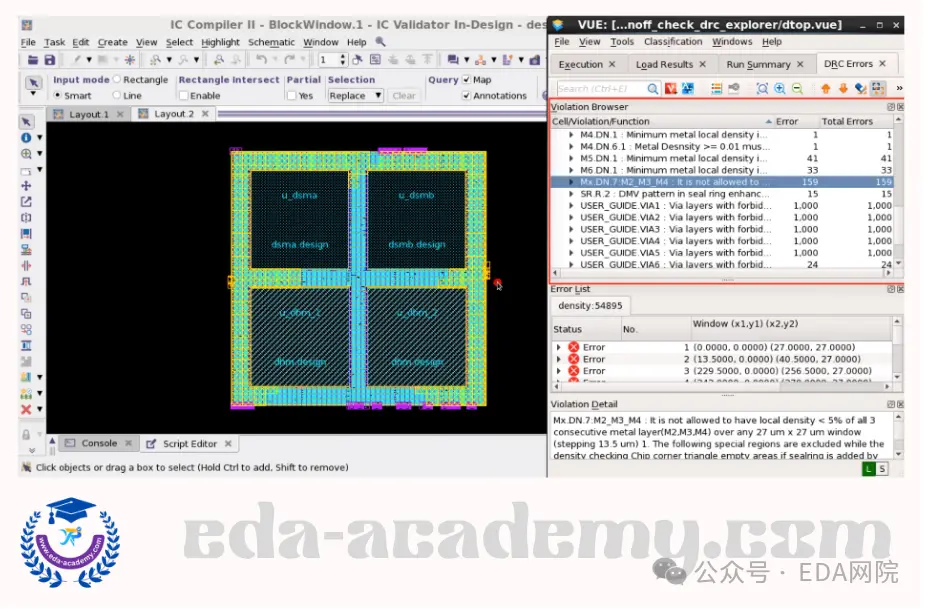

Cadence Pegasus Verification System (/ PVS)

Pegasus 是 Cadence 針對大規模 DRC 籤核、高吞吐、雲/並行處理優化的方案。其官方稱可實現“up to 10×”對比傳統工具的 DRC 加速。

優勢在於:如果你的挑戰是“跑滿一整片 GDS 或 3D 封裝設計,常常卡在 DRC 排隊/跑滿一夜”的情況,Pegasus 的彈性並行特性就尤為吸引。適用場景:大型 SoC、3D IC、封裝設計或多片 - 拼 場景,且你能調用雲/大規模 CPU 資源。注意事項:仍需確認 deck 兼容性、現場經驗與 foundry 籤核流程。 - 選擇標準 & 決策因素

Deck 成熟度與歸屬

工具並不是孤立存在,最關鍵的是 rule-deck(檢驗規則集)是誰寫、誰維護、在哪裏首先生效。

如果 foundry 本身提供基於 Calibre 的 籤核 deck,那麼即便你流程用別的工具,也可能因為 deck 不成熟而坑很多。

最快的 debug 循環

在設計階段就做 DRC/LVS(如 ICV)可以顯著減少後階段返工。

在籤核階段再做(如 Calibre 或 PVS)意味着你可能已積累大量問題。

因此你需要問:我更看重“早期乾淨”還是“最後籤核通關”?

吞吐能力 & 隊列痛點

當你趕 tape-out、跑的是整片 GDS 、要在短時間內完成驗證:

Pegasus 強項是大規模並行、雲/爆發計算能力。

ICV 也有強分佈式能力(例如支持數千 CPU 核)

Calibre 雖也有大規模選項,但在“爆發式並行+雲”場景上可能略遜。

所以,若你的現實環境是“工具隊列長”“跑一次要等待一天以上”,就要優先考慮並行能力。

3D/封裝 & 混合信號邊界

現代設計越來越不是純數字 2D 芯片:3D IC、封裝結構、混合信號塊、芯片-片間互連,都讓驗證工具必須覆蓋這些邊界。

因此要確認:你的 工具是否被用來驗證 die + interposer + package + BGA/LGA 等場景。 - 實戰分享要點

跑哪一節點/哪個 foundry?節點越先進、規則越複雜,工具選型越重要。

運行時間最長的原因是什麼?是密度(density)、層級(hierarchy)、天線效應(antenna)、奇偶數循環(odd-cycle)?

調試/查看界面哪些幫助你省下了時間?強大的 viewer/debug UX 可以讓你少卡一小時、甚至一天。

這些實際問題往往決定“選哪個工具”的最終答案。 -

總結建議

如果你在領先節點,且 foundry deck 已在 Calibre 上成熟:優先選 Calibre。

如果你整個流程以 Synopsys 生態為主,想把驗證提前到設計實現階段:選 IC Validator。

如果你追求極致 DRC 吞吐、暴力並行、大片驗證,尤其是 3D/封裝場景:考慮 Pegasus。

最好結合你的 IT 資源(有無雲/大規模 CPU farm)、團隊經驗、流程契合度,再做決定。END《EDA網院》出品 · 與全球工程師一起探索芯片的世界