“觸發器決定了數字電路的“節奏與記憶”。”

在數字系統中,觸發器(Flip-Flop)是構建時序邏輯電路的核心元件。它能夠存儲一個二進制狀態,並在時鐘或控制信號的作用下改變輸出。不同類型的觸發器在功能和用途上略有差異:有的僅在特定時鐘沿觸發狀態變化,有的支持置位、復位或翻轉操作。理解各種觸發器的特性,是掌握寄存器設計、計數器實現以及有限狀態機建模的基礎。

1、觸發器的基本概念觸發器是一種雙穩態電路,即電路具有兩個穩定輸出狀態,通常用 Q 表示當前狀態,用 Q’ 表示其反相。時序邏輯的關鍵特性在於:輸出不僅取決於當前輸入,還取決於歷史狀態。

在實際設計中,觸發器用於存儲單個位數據,並根據時鐘信號控制其更新。它們是寄存器、計數器、狀態機等複雜邏輯的核心組成部分。

2、D觸發器(D Flip-Flop)D觸發器是最常見的一種類型,名稱中的“D”代表“Data”。它在時鐘上升沿時將輸入D的值鎖存為輸出Q的下一狀態(Q+)。在時鐘信號未觸發時,輸出保持不變。

邏輯關係:Q⁺ = D

這意味着在時鐘沿到來時,輸出等於當時輸入的值。D觸發器非常適合在同步系統中用作數據寄存器,因為它能確保數據只在時鐘信號變化的瞬間更新,從而避免毛刺與競爭風險。

D觸發器的設計簡單、行為穩定,是大多數同步邏輯系統的首選基礎單元。

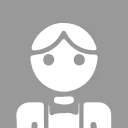

3、J-K觸發器(J-K Flip-Flop)J-K觸發器功能更靈活,可實現置位(Set)、復位(Reset)與翻轉(Toggle)操作。它的輸入端為J和K,輸出為Q。其狀態轉移規則如下:

這種設計解決了早期S-R觸發器存在的“無效狀態”問題,並且在時鐘觸發下能靈活切換狀態。由於其具備多種功能,J-K觸發器常用於計數器和狀態機中。

其核心優勢在於:只需通過不同的輸入組合,即可實現存儲、清零與狀態反轉,大幅提高邏輯利用率。

4、T觸發器(T Flip-Flop)T觸發器可看作J-K觸發器的簡化形式,當J與K輸入相同且命名為T時,即形成T型觸發器。其工作規則極為簡潔:當T = 1時,輸出Q翻轉(0變1,1變0);當T = 0時,輸出保持不變。

邏輯關係:Q⁺ = T ⊕ Q

這種觸發器特別適合用於計數器設計,例如二進制遞增計數器。多個T觸發器級聯,可以實現二進制序列的自動遞增。由於結構簡單、響應明確,T觸發器是實現時鐘分頻、脈衝計數等應用的關鍵元件。

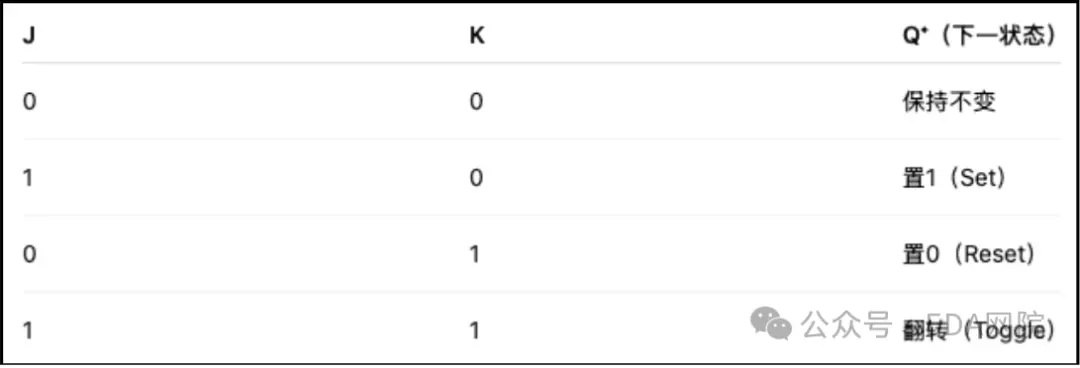

5、S-R觸發器(S-R Flip-Flop / Latch)S-R觸發器是最早的觸發器形式,由兩個NOR門交叉連接構成。S表示“Set”(置位),R表示“Reset”(復位)。

其工作規則如下:

當S和R同時為1時,兩個輸出端都為0,這種狀態是不允許的,因此該組合在實際設計中應避免。S-R觸發器不依賴時鐘信號,是一種電平敏感鎖存器(Latch),適合實現簡單的控制邏輯或暫存功能。

6、D鎖存器(D Latch)D鎖存器是基於S-R鎖存器的改進版本,也稱為透明鎖存器(Transparent D Latch)。它的輸入端為D,控制端為G(或稱為Enable)。當G=1時,輸出Q緊跟輸入D變化;當G=0時,Q保持上一次的值。

邏輯關係:當G=1時,Q = D;當G=0時,Q保持不變。

D鎖存器常用於需要在某段時間內保持輸入值的電路中,例如暫存寄存器。由於它是電平敏感的,不具備嚴格的時鐘同步特性,因此常與D觸發器配合使用以構建安全的時序邏輯。

7、不同觸發器的比較

通過合理選擇觸發器類型,設計者可以在不同場景下平衡邏輯複雜度、功耗和速度。例如,D觸發器適合同步寄存;T觸發器適用於低功耗計數;而J-K觸發器適合多模式控制電路。

觸發器是數字系統記憶的核心。從最早的S-R結構到現代同步D觸發器,它們共同構建了邏輯電路的“時間維度”。理解各種觸發器的差異與用途,能幫助設計者更精準地控制數據流與時序,實現更高效、更可靠的硬件設計。

《EDA網院》出品 · 與全球工程師一起探索芯片的世界