“芯片背後,是一個龐大且脆弱的生態系統。”

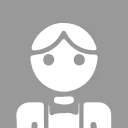

今天我們從高處俯瞰芯片產業:從藍圖誕生,到晶圓生產,再到包裝測試,貫穿設計、材料、工具、IP。每一個環節都有關鍵角色參與。認識這七層,你才能真正理解“芯片為何如此珍貴、為何生產一斷就慌亂”的背後邏輯。

下面按照七層結構,一層一層地展開解讀。

✤ 1 ✤ 晶圓代工廠

在這一級,典型代表包括 TSMC、Samsung、UMC、SMIC。這些廠商負責將芯片設計藍圖 (通常為電路圖、佈局、掩膜等)轉化為物理的硅晶圓,利用納米級光刻、離子注入、薄膜沉積等工藝。

晶圓代工的難度極高:潔淨室環境、蠅頭大小的缺陷都可能讓一整片晶圓報廢。此層被視為“製造核心”,但也正因其高度集中與複雜,使得整條鏈條容易產生瓶頸。

✤ 2 ✤ 整合器件製造商

這一層代表是像 Intel、Micron、SK Hynix 這樣的公司,它們既設計芯片又自己製造。相比只設計或只代工的公司,IDM 擁有從前端設計到後端封裝測試的完整能力。優點:供應鏈可控性強、技術積累深。缺點:投資門檻極高、靈活度較低。IDM 在產業鏈中起的是“全方位角色”,但並非所有芯片公司都能走這條路。

✤ 3 ✤ 無廠房公司

代表包括 Apple、AMD、NVIDIA、Qualcomm。這些公司專注於芯片的設計與邏輯架構,而將製造委託給晶圓代工廠。這種模式的優勢在於:資本投入相對較低、設計靈活性高;但也意味着對代工層極度依賴。若代工廠產能受限或設備升級延遲,fabless 型公司就容易陷入“等待晶圓”的窘境。在當前芯片缺貨、產能瓶頸頻出的環境下,無廠房公司的挑戰被放大。

✤ 4 ✤ 晶圓製造設備

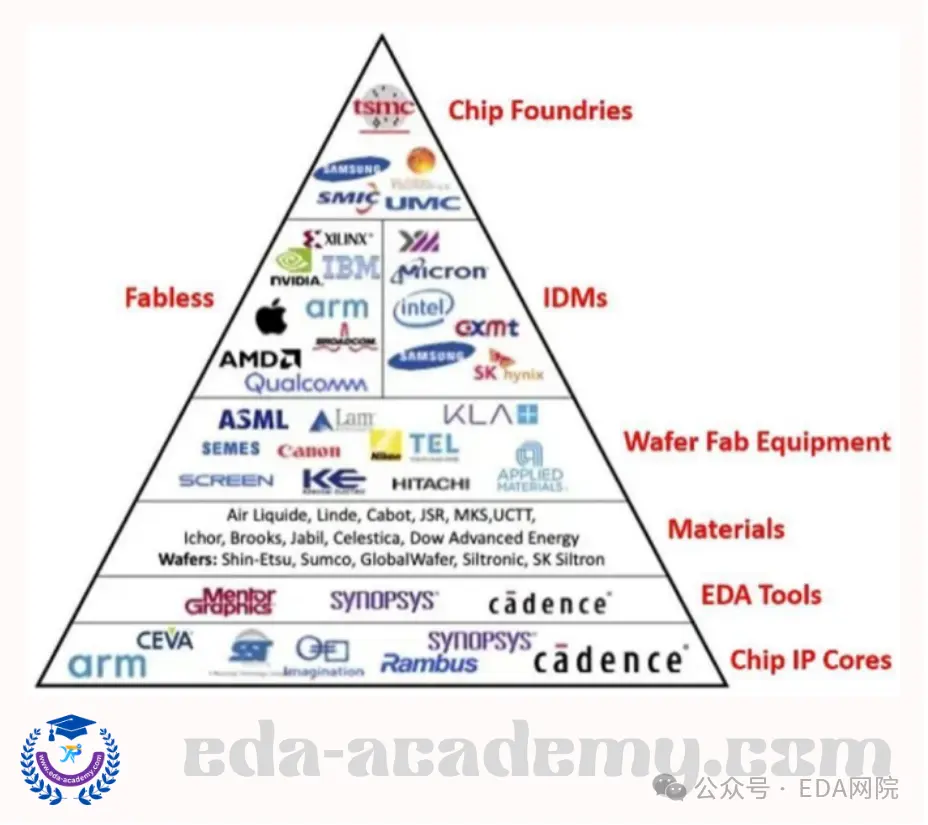

這一級別包括諸如 ASML、Lam Research、KLA 這類製造晶圓所必需的設備廠商。他們生產極其昂貴、技術最尖端的機器,比如用於紫外光刻(EUV,極紫外線光刻)、沉積、刻蝕、離子注入等。

沒有這些設備,就沒有先進節點芯片。也正因為設備高門檻、研發週期長、產業集中,該層也成為全球地緣政治、技術封鎖的重要戰場。

✤ 5 ✤ 材料與晶圓

在這一層出現的角色包括氣體供應商(如 Linde)、硅晶圓廠商(如 Shin‑Etsu、Sumco)等。材料是芯片製造的“物質基礎”——如果原料純度、夾雜物、晶圓平整度出問題,那麼後面的光刻、刻蝕、金屬互連都可能失敗。常被忽視,卻極其關鍵。比如某些稀有氣體流量受限、晶圓廠商供應緊張,就可能引發整個芯片製造節點延遲。

✤ 6 ✤ EDA 工具

這一級指的是用於芯片設計的軟件工具廠商,比如 Synopsys、Cadence、Mentor Graphics(現為西門子一部分)、TestFlow。這些工具負責從 RTL (寄存器轉移級)設計、版圖佈局、後仿驗證、到硅後驗證。沒有這些工具,設計團隊無法將想法變為可製造的晶圓藍圖。軟件層面雖然是“隱形”但卻是芯片成功的前提。

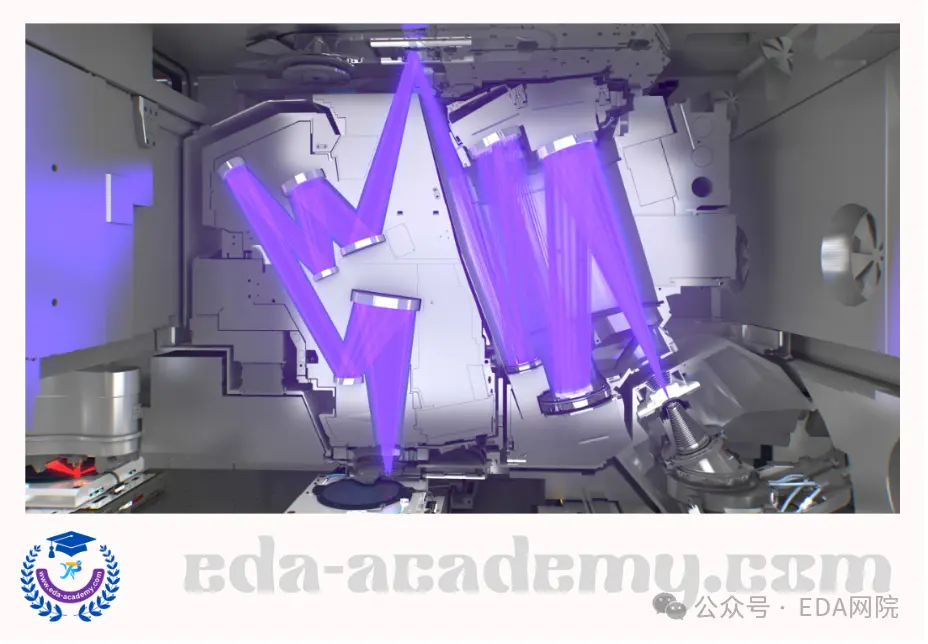

✤ 7 ✤ 芯片 IP 核

最後一層,是像 ARM、CEVA、Rambus 這樣的公司提供可複用的邏輯模塊(如處理器核心、DSP、接口控制器)。它們像樂高積木一樣,被設計公司嵌入自家芯片中,從而節省設計時間、降低成本、提高複用率。

因為幾乎每個現代芯片(手機、汽車、服務器)都內含這些 IP 核,故這一級看似“隱蔽”,但其廣泛性與不可替代性極高。

全鏈條的關鍵啓示

協作性極強:任一層出問題(如設備延遲、材料短缺、設計衝突)都可能影響整條鏈。

集中度高、壁壘高:許多層由少數幾家公司主導,使得產業風險集中。

地緣+技術風險疊加:技術升級快、投資大,且全球分佈複雜,容易受到政策、疫情、物流的衝擊。

透明度低但價值鏈長:外界往往只看見“芯片”這個最終產品,但背後的七層機制、幾千家公司、全球協作,是隱藏的巨型工程。

瞭解這七層,就是洞察現代芯片世界的鑰匙。無論你是技術從業者、產業觀察者,還是對電子產品背後邏輯好奇的讀者,都能借此認識:每一塊“二極管+電容+金屬互聯”的芯片,其實承載了世界級的產業編排。讓我們一起在技術的迷宮中,多看一層、多想一環。

✺ END ✺《EDA網院》出品 · 與全球工程師一起探索芯片的世界