“硬件描述語言是連接邏輯與電路、抽象與實現的關鍵設計語言。”

在數字電路設計的世界裏,硬件描述語言(HDL, Hardware Description Language) 是一類非常特殊的編程語言。與傳統的軟件編程語言不同,HDL 不僅能描述功能邏輯,還能建模電路的並行性與時間特性,因此它被廣泛應用於芯片設計與驗證。

- HDL 的獨特之處

普通編程語言關注的是指令順序和數據處理,而 HDL 更像是為電路量身定製的“語言”。它不僅能表達電路的運算邏輯,還能捕捉電路在真實硬件中並行工作的特徵。例如:

串行行為:一個功能模塊的輸出作為下一個模塊的輸入,類似傳統軟件的執行順序。並行行為:一個模塊的輸出可以同時驅動多個模塊,在同一時刻並行發生多個事件,這是 HDL 的核心優勢之一。

- 從行為到結構的建模

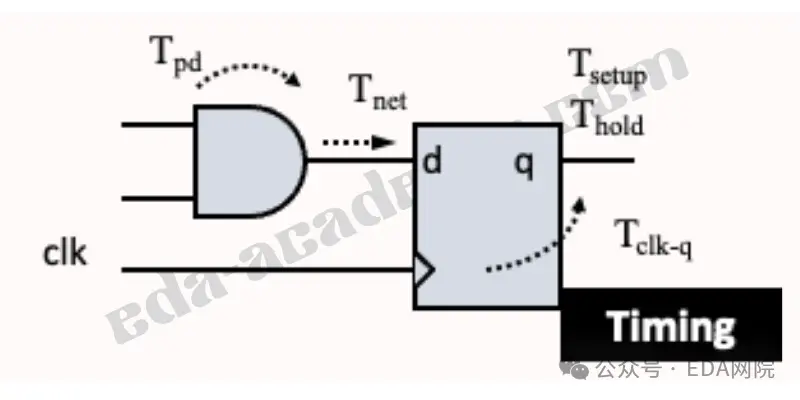

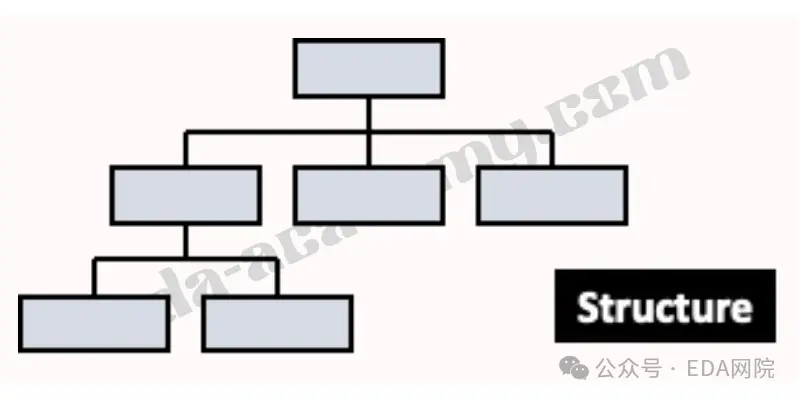

HDL 不只停留在描述邏輯行為,還支持對電路結構進行精細建模:

行為建模:從高層次描述電路的邏輯功能,可以是抽象的算法級,也可以細化到可綜合的邏輯級。結構建模:通過層級化的方式描述系統,如電路模塊圖、組件連接表,甚至是函數和子程序結構。這種方式使得工程師可以有效地管理和構建大型、複雜的數字系統。 - 時間維度的引入

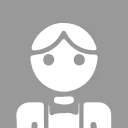

傳統的軟件編程語言幾乎沒有“時間”的概念,但電路設計卻離不開時鐘、延時與同步。HDL 天然支持以下時間特性:

傳播延遲:信號從一個模塊傳播到另一個模塊所需的時間。時鐘週期:電路運行的基本節奏。時序檢查:確保設計滿足建立時間、保持時間等約束條件。

正因為引入了時間維度,HDL 才能在仿真環境中準確反映設計的動態行為,為後續的綜合與流片提供可靠依據。

-

多層抽象的支持

HDL 的強大之處在於它能覆蓋多種抽象層次:高層行為描述:快速驗證設計思路和功能正確性。邏輯綜合層次:為綜合工具生成門級電路提供足夠細節。網表級描述:精確到晶體管或預定義組件,確保能映射到實際硬件。

這種靈活的抽象能力,使 HDL 成為數字系統設計從構想到實現不可或缺的工具。

硬件描述語言的價值在於,它不僅僅是一種“代碼”,更是數字電路世界的橋樑。通過 HDL,設計者可以在抽象與細節、邏輯與結構、時間與行為之間自由切換,從而高效地完成從設計到實現的全過程。

對於初學者而言,理解 HDL 不只是學習一門語言,而是掌握了進入芯片設計核心的鑰匙。END《EDA網院》出品 · 與全球工程師一起探索芯片的世界