在 VLSI、數字 IC、驗證或物理設計的世界裏,工程師的日常語言幾乎被縮寫“統治”——有些耳熟能詳,有些晦澀神秘,還有些讓新人望而生畏。本系列將從 A 到 Z,把這些高頻縮寫逐一拆解成“真正能聽懂的工程語言”,幫助你係統補齊基礎概念。

✦ 01 從 A 到 I:九個最常遇到、卻最容易用錯的縮寫

• ATPG:自動生成測試向量,決定芯片能否“抓住缺陷”。

• BIST:讓芯片能自測,不依賴昂貴測試儀。

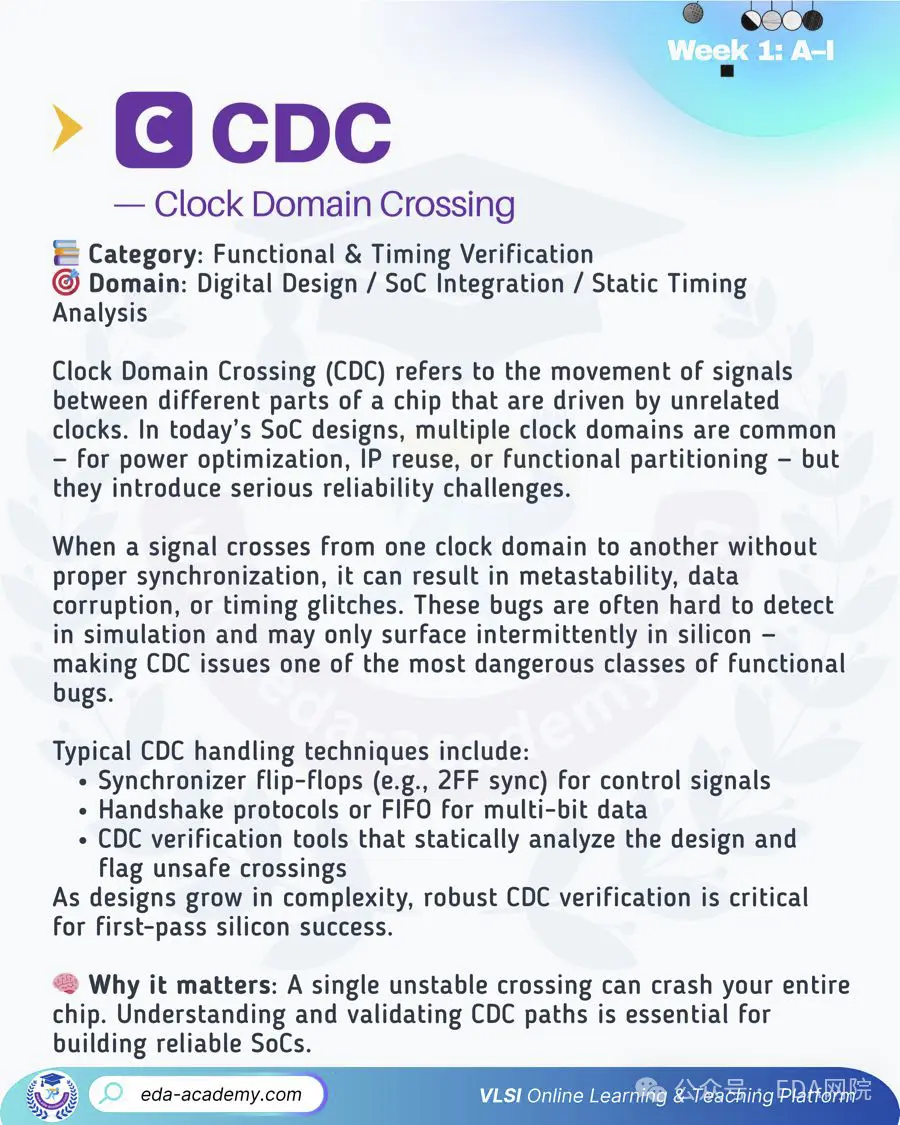

• CDC:時鐘不同步時的所有潛在災難。

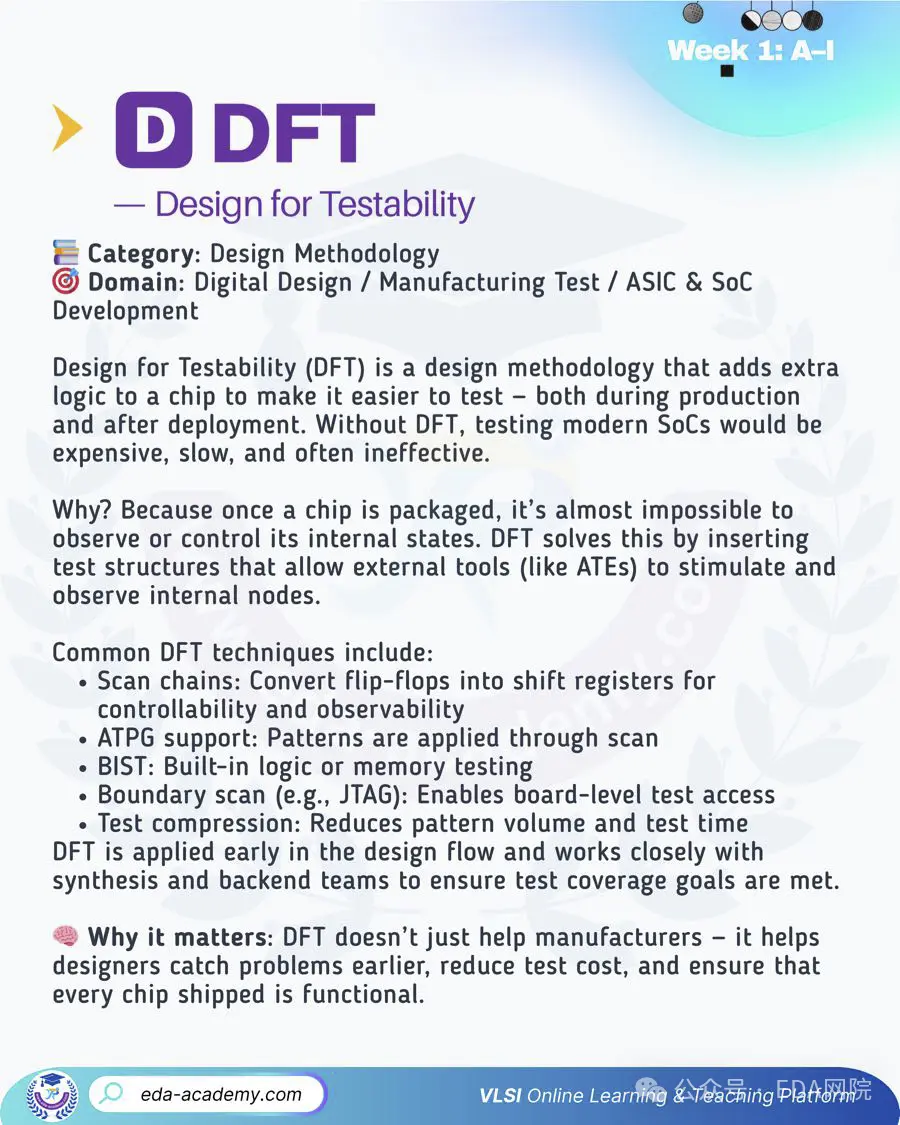

• DFT:為了讓芯片可測而在設計階段鋪好的“伏筆”。

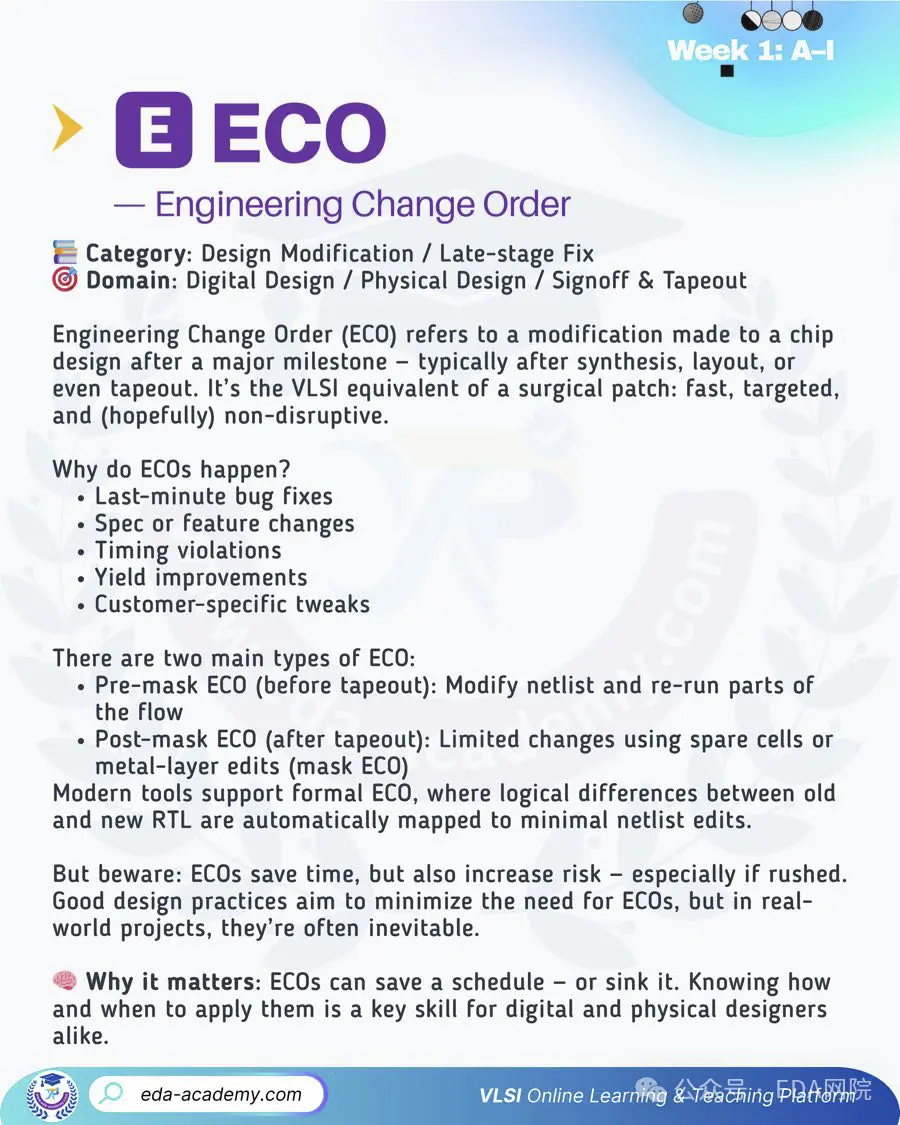

• ECO:挽救(或毀掉)流片的最後補丁。

• FSM:控制邏輯的靈魂,也是面試常客。

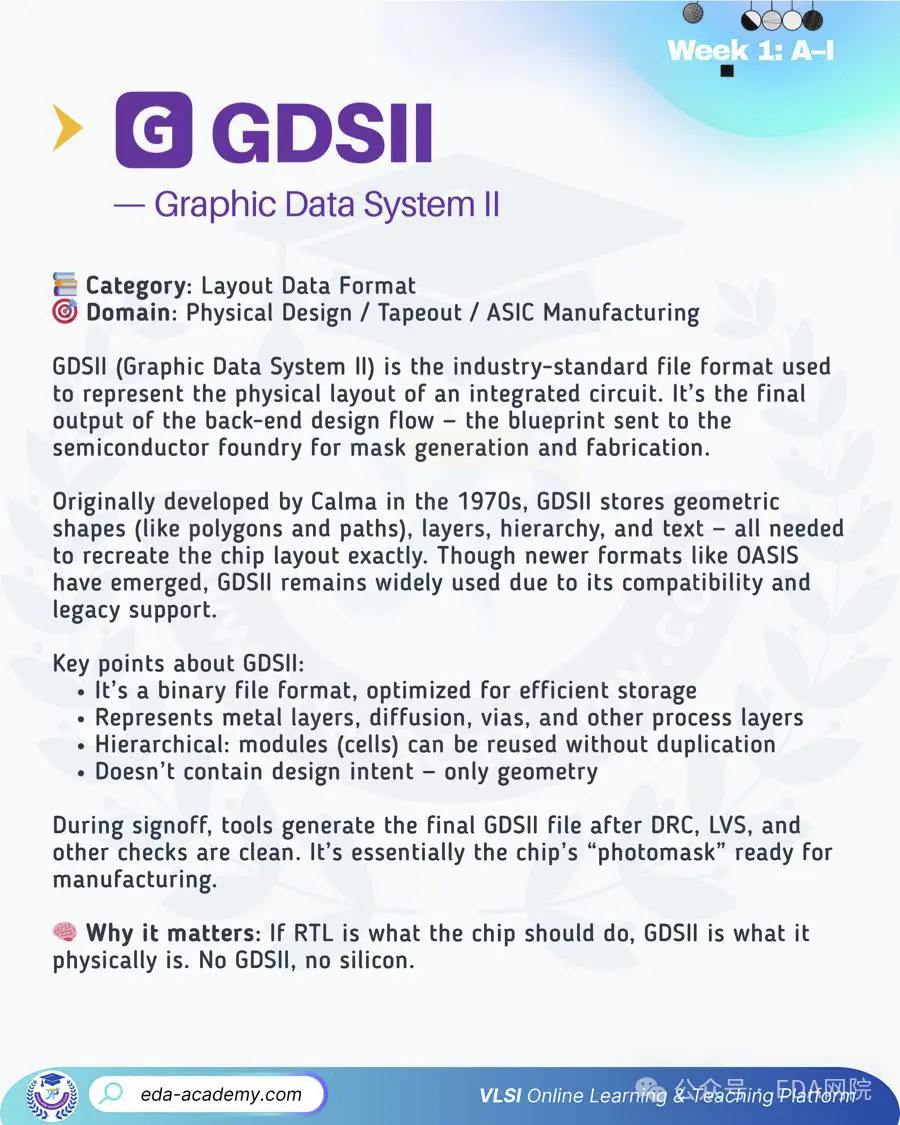

• GDSII:讓你的設計真正走向硅片的關鍵文件。

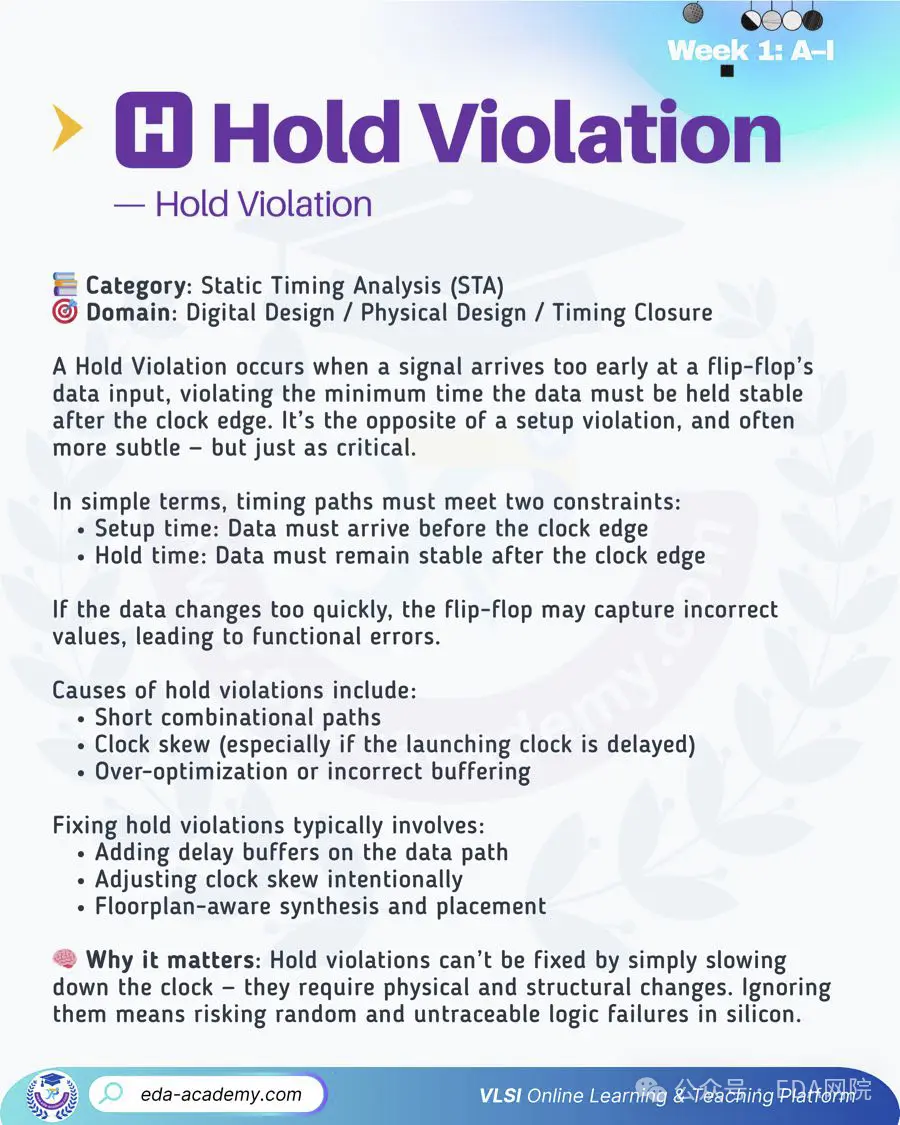

• Hold Violation:信號“太快”也會出事。

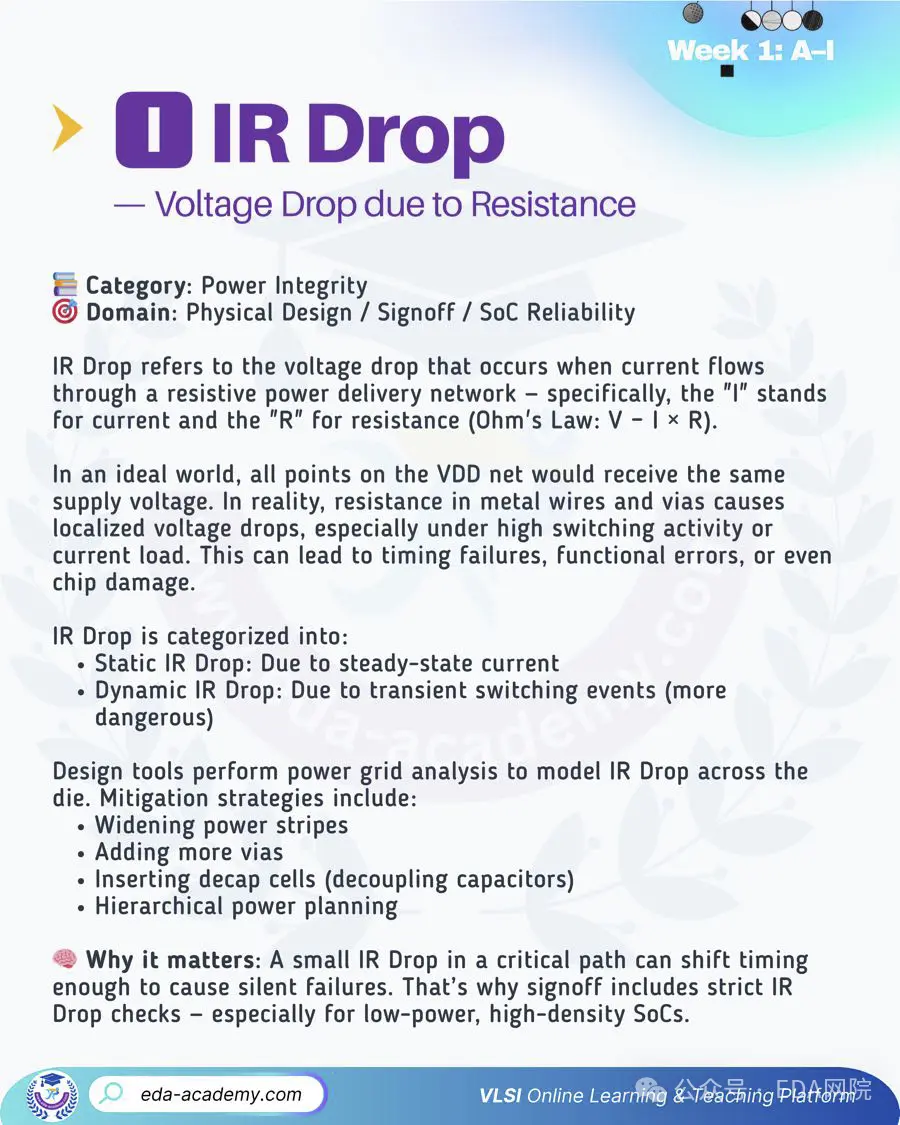

• IR Drop:電壓掉得比你想象得更快,時序也跟着崩。

✦ 02 場景化理解,讓縮寫真正“用得上”

這些縮寫不僅是概念,更是日常工程判斷的基礎:調試仿真、做時序、讀版圖、寫 RTL、追 coverage,都離不開它們。

✦ 03 適用人羣廣泛

無論你是準備面試、團隊新人培訓,還是想系統補課 EDA 基礎,這套從 A–Z 的系列內容都能帶你快速建立完整認知。

學習縮寫,其實是在學習整個 IC 設計的底層邏輯。