EDA 縮寫從來不是“字母遊戲”,而是 IC 設計各個環節的專業語言。本週來到系列收官篇,從仿真到籤核、從時序到良率,這些 S–Z 開頭的縮寫幾乎貫穿整個芯片開發流程。理解它們,就等於掌握工程師日常溝通的底層“詞典”。

✦ 01 本週關鍵詞:八個必須熟練掌握的核心縮寫

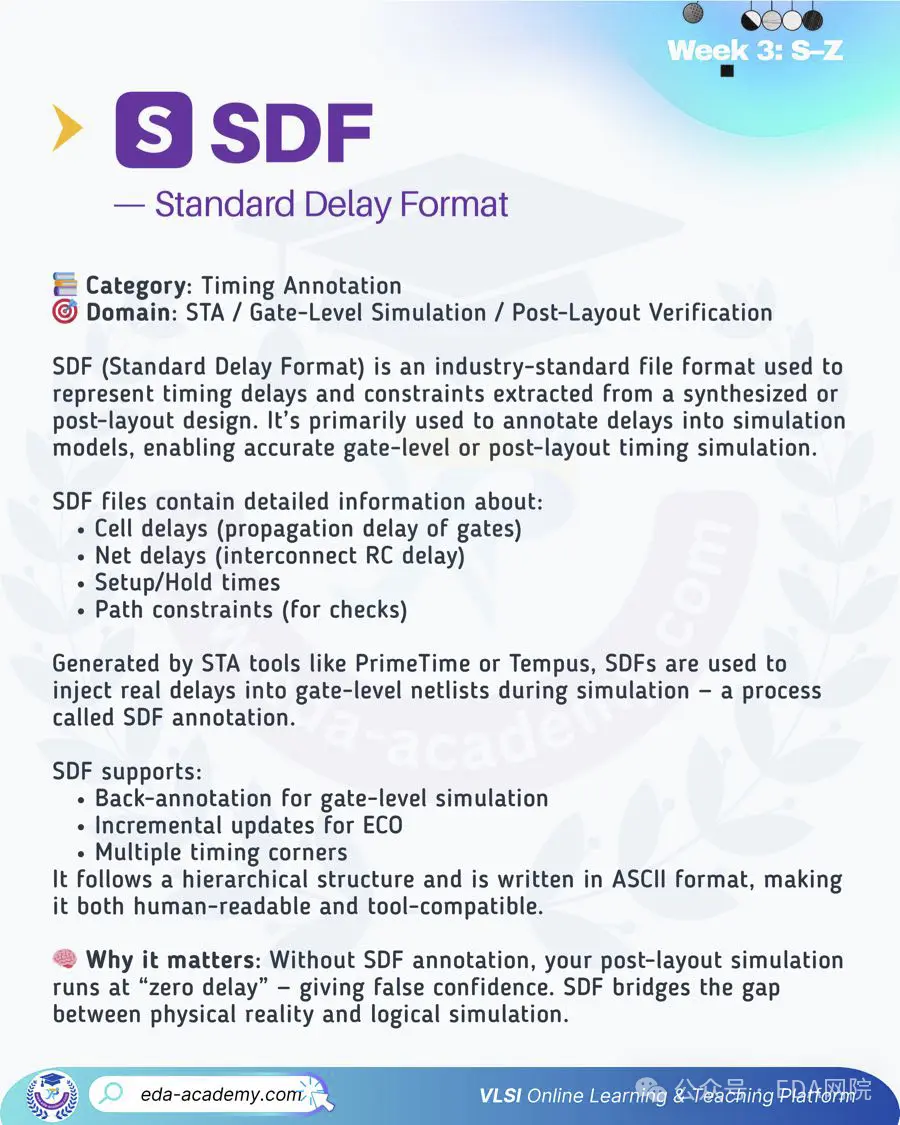

• SDF:在仿真中加入真實延遲,讓模型更接近硅上表現。

• TNS:總負裕量,衡量你“時序差多少”的全局指標。

• UVM:現代驗證環境的標配框架,團隊協作的基礎。

• VCD:每一次深夜波形調試,幾乎都離不開它。

• WNS:最差負裕量,決定你需要優先修的那條路徑。

• X-Propagation:X 擴散常常暴露隱藏 bug,是仿真不容忽視的信號。

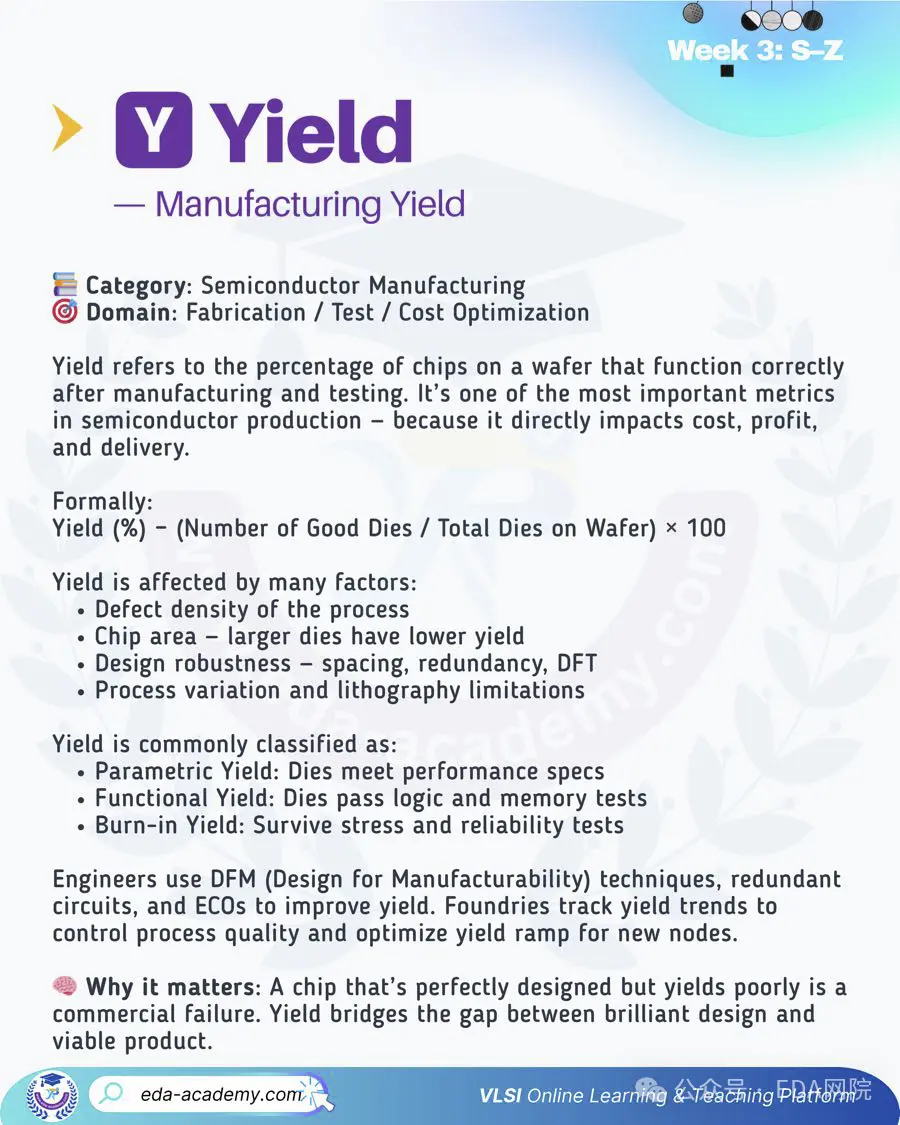

• Yield(良率):決定一個芯片是否能成為“產品”的關鍵數字。

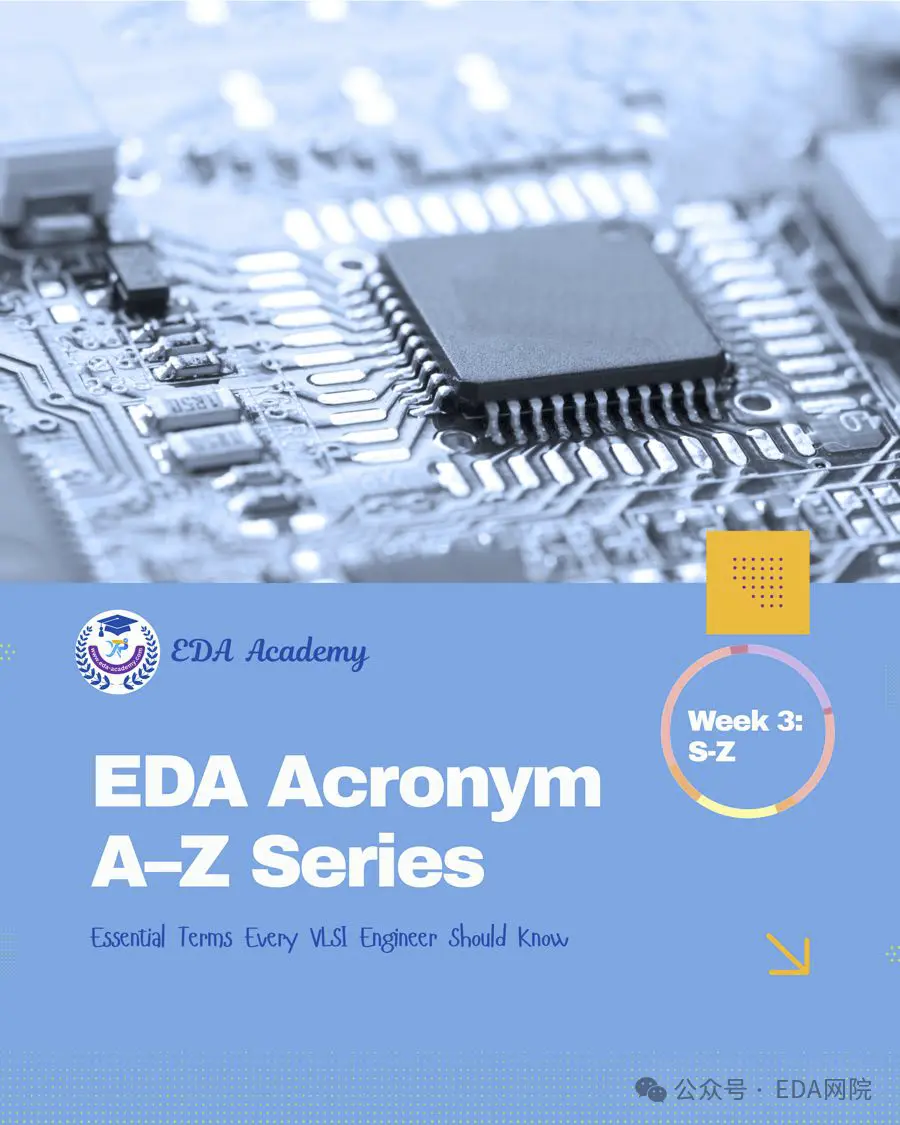

• Zero Delay:零延遲仿真雖快,但它只適合“想象中的芯片”。

✦ 02 理解縮寫,就是理解 IC 設計的本質

從 RTL 到佈局佈線、從仿真到時序籤核,這些縮寫不只是術語,而是每個工程判斷背後的思維框架。越理解它們,你在項目中的判斷就越準確。

✦ 03 A–Z 系列完結,但基礎永遠值得複習

無論你是準備面試、強化基礎,還是想提升團隊整體認知,這套從 A 到 Z 的縮寫系列都能成為你的長期參考。

EDA 不是黑話,而是一門語言。掌握語言,就能更好地理解芯片世界。