無論你是 IC 設計新手,還是資深 RTL Synthesis 工程師,深入掌握設計可測試性(DFT)關鍵技術,是提升芯片可靠性的必經之路。

1、為什麼 DFT 在現代 IC 中變得不可或缺

提升可控性與可觀測性:通過在設計中嵌入測試結構,內部節點的狀態能被有效控制與觀察,從而支持故障定位與調試。

縮短測試時間、降低成本:採用 scan chain、大規模並行測試、BIST 和 MBIST 等先進技術,能顯著縮短測試流程並減少昂貴 ATE 的依賴。

2、關鍵 DFT 技術一覽

I. Scan Chain(掃描鏈)

將所有寄存器(Flip-Flop)串聯成可切換的掃描鏈,支持在測試模式下 shift-in test vectors、shift-out 結果,從而提升測試覆蓋率與測試效率。

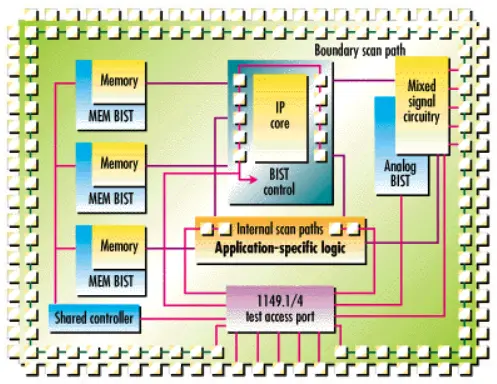

II. Built-In Self-Test(BIST)

將測試生成與響應解析邏輯內建於芯片內部,實現自動CPU級別測試,尤其擅長 at-speed 測試,適用於邏輯與控制器的自檢。

III. Memory BIST(MBIST)

專門針對片上嵌入式存儲器的測試機制,通過在設計階段插入自動化測試結構,大幅提升內存測試覆蓋與開發效率。

IV. 分層 DFT(Hierarchical DFT)

將複雜 SoC 設計劃分為多個 DFT 可控模塊,各模塊獨立測試、最後集成,有助於提升測試效能並縮短集成測試時間。

V. 低功耗下的 DFT(Low-Power DFT)

在測試中考慮功耗限制,採用動態功率管理策略,避免測試過程中過高功耗導致電源壓力,同時捕獲電源相關故障。

3、EDA Academy · 提升你的 DFT 能力

在 EDA Academy(網址:www.eda-academy.com),你能找到:

· 大量專業網課:覆蓋從 scan chain 到 BIST、MBIST、分層與低功耗 DFT 的最新課程。

· 成為導師機會:優秀專業人士可在此註冊成為課程導師,將知識轉化為收益。

· 免費訂閲 Newsletter:只需提供郵箱,即可定期收到最新技術洞察與課程推薦。

· 銷售聯盟計劃:通過推薦課程給他人,可獲得 20%–50% 的佣金回報。

4、讓 IC 更可靠,更易測

通過整合 scan chain、BIST、MBIST、分層 DFT 等方法,你的 IC 設計不僅更易測試、更可靠,還能大幅降低開發和測試成本。深入學習這些技術的最佳路徑是加入 EDA Academy,掌握行業頂端知識,打造質量領先的芯片產品。