macros.rs

macro_rules! write_csr {

($csr_number:literal) => {

/// Writes the CSR

#[inline]

#[allow(unused_variables)]

unsafe fn _write(bits: usize) {

match () {

#[cfg(riscv)]

() => core::arch::asm!(concat!("csrrw x0, ", stringify!($csr_number), ", {0}"), in(reg) bits),

#[cfg(not(riscv))]

() => unimplemented!(),

}

}

};

}

stvec.rs

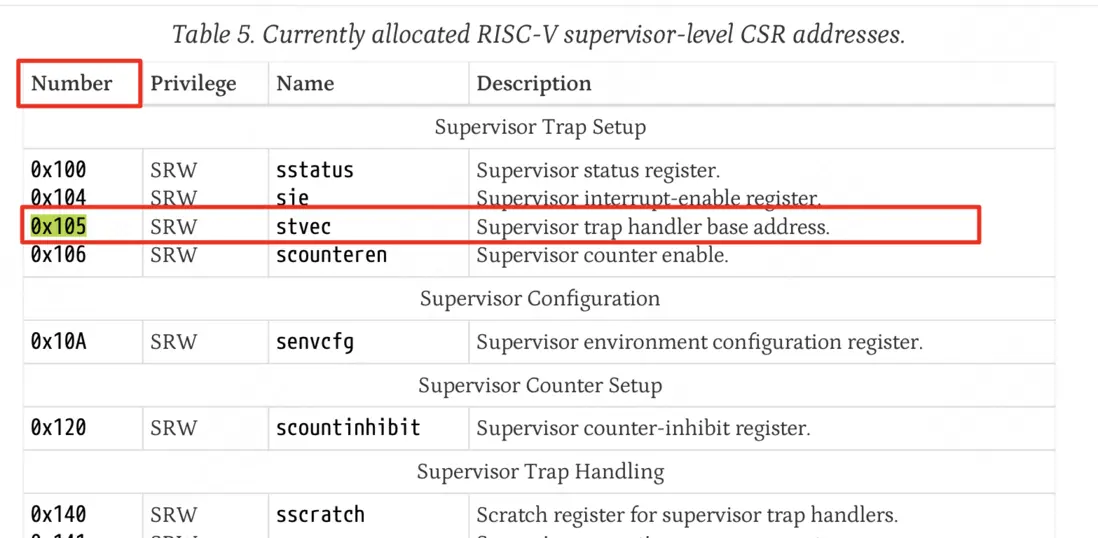

read_csr_as!(Stvec, 0x105);

write_csr!(0x105);

/// Writes the CSR

#[inline]

pub unsafe fn write(addr: usize, mode: TrapMode) {

_write(addr + mode as usize);

}//write_csr 這個宏通過使用Rust的宏機制生成一個內聯、允許未使用變量並且不安全的函數 _write。這個函數將執行一個RISC-V特權指令,將某個值寫入指定的CSR寄存器。

為什麼要相加?

在RISC-V架構中,stvec寄存器的低2位用於存儲陷阱模式(Trap Mode),其餘位用於存儲入口地址。因此,當我們設置stvec寄存器時,需要將處理函數地址與陷阱模式組合在一起:

入口地址:高位(去掉低2位)部分保存處理函數地址。

陷阱模式:低2位保存陷阱模式。