最近小編客户研發的一款產品在調試語音與上位機通訊總是出現個別產品功能異常,請啓英泰倫協助分析解決。小編分析發現異常原因為語音芯片和上位機芯片均存在頻偏,兩者頻偏相加後導致串口通訊波特率偏差較大,串口通訊失敗。小編根據啓英泰倫AI平台提供的方法在語音芯片加上了串口波特率自適應後解決了客户的問題。因此小編希望通過本篇文章幫助用户提前規劃好晶振方案、規避後期調試問題。小編就由淺入深來和大家一起探討一下啓英泰倫語音識別芯片的晶振方案選型和應用注意事項。

1. 內置晶振和外置晶振介紹

內部晶振集成於芯片內,成本低、功耗小、節省空間(比如啓英泰倫CI13082V、CI13162),適合對時鐘精度要求不高的場景(如簡單控制、消費電子)。外部晶振基於石英晶體(比如啓英泰倫CI1302、CI13242),精度高(±1\~50ppm)、温漂小,為高速通信(USB、Wi-Fi)、工業控制及汽車電子提供穩定時序基準,是複雜環境和可靠性系統的核心。二者互補,平衡成本與性能,共同保障電子系統的高效運行,兩者特點如下

1.1 內部晶振:

- 實現方式:通過芯片內部集成的RC(電阻-電容)振盪電路或LC振盪電路生成時鐘信號。

- 典型頻率範圍:通常為低頻(如1MHz\~48MHz),部分高端芯片可達100MHz。

- 依賴因素:精度受工藝、温度、電壓影響顯著,需依賴芯片內置校準功能。

1.2 外部晶振:

1. 實現方式:

- 無源晶體(Crystal):需依賴外部負載電容和芯片內部的振盪電路驅動。

- 有源晶振(Oscillator):獨立封裝,內置振盪電路,直接輸出方波信號。

- 典型頻率範圍:覆蓋更廣(kHz\~GHz級),適合高頻需求。

- 穩定性:基於石英晶體的壓電效應,物理特性穩定。

1.3 關鍵參數對比

| 參數 | 內部晶振(RC/LC) | 外部無源晶體 | 外部有源晶振 |

|---|---|---|---|

| 精度 | ±1%~±5%(未校準) | ±10~±100ppm(受温度影響) | ±1~±50ppm(含温補型) |

| 温度穩定性 | 差(隨温度漂移明顯) | 較好(-40°C~85°C) | 極佳(部分支持-55°C~125°C) |

| 啓動時間 | 短(μs級) | 較長(ms級,依賴負載電容) | 短(直接輸出穩定信號) |

| 功耗 | 低(無需驅動外部負載) | 中等(需芯片驅動) | 較高(獨立供電) |

| 成本 | 免費(集成在芯片內) | 低(晶體+電容成本) | 高(集成振盪器) |

| 抗干擾能力 | 強(芯片內部路徑短) | 弱(易受PCB佈局和噪聲影響) | 中等(需屏蔽設計) |

| 佔板面積 | 無需外部元件 | 需晶體+2個負載電容 | 需晶振+電源濾波電容 |

2. RC振盪器原理

2.1 核心結構與類型

RC振盪器由放大電路、RC選頻網絡、正反饋迴路及穩幅環節四部分組成。其本質是利用電阻(R)和電容(C)的充放電特性構建選頻網絡,替代傳統LC振盪器中的電感元件,適用於1Hz--20MHz低頻範圍的信號生成。

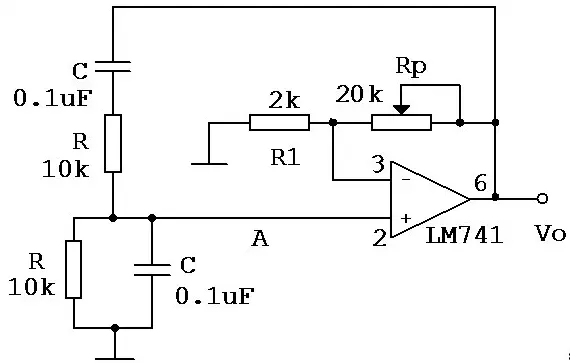

文氏橋振盪器:採用RC串並聯結構,振盪頻率公式為:f0=1/2πRC 通過調節R或C值可精確調頻,文氏橋振盪器結構如下圖:

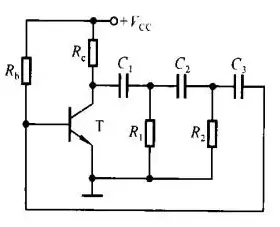

相移振盪器:通過多級RC網絡(如3級)實現90°相移,總相移達360°以滿足相位條件,但調頻靈活性較差,結構原理如下圖:

雙T網絡振盪器:基於雙T型RC濾波,選頻特性尖鋭,適合固定頻率場景

工作原理與振盪條件:

起振階段:電源接通瞬間,電路噪聲包含寬頻譜信號,經RC選頻網絡過濾後,特定頻率分量(滿足相位條件)被放大並反饋至輸入端,形成正反饋循環,信號幅值逐步增大。

穩幅機制:當振幅增長至臨界點,非線性元件(如熱敏電阻、反向並聯二極管)自動降低環路增益,使振幅穩定。例如文氏橋振盪器通過負反饋支路(Rf與R1)實現增益控制。

振盪的數學條件

幅度條件:環路增益 ≥ 1(即∣Aβ∣≥1,A為放大倍數,β為反饋係數)。

相位條件:總相移為360°的整數倍(即正反饋)。

示例:文氏橋在f0=1/2πRC時,相移為0°且反饋係數β=1/3,需放大倍數A≥3方可起振。

2.2 關鍵性能參數與影響因素

1、頻率穩定性差

核心原因:RC 選頻網絡的參數(R、C)受温度、濕度、振動等環境因素影響較大(如電阻的温度係數、電容的老化或温漂),導致振盪頻率容易漂移。

表現:長期工作或環境變化時,輸出頻率偏差可能超過 1%(甚至更大),難以滿足高精度設備(如通信系統、精密測量儀器)的要求。

2、頻率調節精度有限

傳統 RC 振盪器通過手動調節可變電阻或電容改變頻率,但機械調節方式精度低(尤其是微調時),且調節過程中頻率易產生跳變,難以實現連續、精確的頻率控制。

3、輸出波形失真可能較大

部分 RC 振盪器(如文氏橋振盪器)依賴放大電路的非線性特性穩幅,若穩幅電路設計不當(如反饋量控制不佳),易導致輸出波形(如正弦波)出現失真(如削波、畸變)。

4、高頻性能受限

當需要高頻輸出時,需減小 R 或 C 的數值。但過小的 R 會增加電路功耗,過小的 C 則易受分佈電容(如線路間寄生電容)影響,導致頻率不穩定,因此 RC 振盪器通常適用於 1MHz 以下的中低頻場景,高頻性能不如 LC 振盪器或晶體振盪器。

2.3 針對性解決方案

提升頻率穩定性

採用高精度元件:選用低温漂電阻(如金屬膜電阻,温度係數≤50ppm/℃)和穩定性好的電容(如聚丙烯電容、雲母電容,温漂小且老化率低),減少環境因素對 R、C 參數的影響。

加入温度補償電路:在電路中串聯或並聯具有負温度係數的元件(如熱敏電阻),當環境温度變化導致 R、C 參數偏移時,補償電路可反向調節,抵消頻率漂移。

引入鎖相環(PLL)技術:將 RC 振盪器的輸出頻率與高精度參考源(如晶體振盪器)通過鎖相環同步,利用 PLL 的反饋調節能力,將 RC 振盪器的頻率穩定在參考源的精度水平(可達 ppm 級甚至 ppb 級)。

提高頻率調節精度,採用數字電位器或數字電容:通過單片機控制數字電位器(如 X9C103)或可編程電容陣列,實現電阻、電容的電子調節,調節精度可達 1% 甚至 0.1%,且支持連續微調,避免機械調節的誤差。

分段調節 + 細調結合:將頻率範圍劃分為多個頻段,通過切換固定電阻 / 電容實現粗調,再用數字微調元件進行精細調節,兼顧寬範圍調節和高精度控制。

改善輸出波形失真,優化穩幅電路:文氏橋振盪器中,採用具有負温度係數的熱敏電阻(如在正反饋支路串聯)或場效應管(FET)構成自動增益控制(AGC)電路,實時調節放大電路增益,使輸出幅度穩定在非線性失真最小的範圍內。

增加濾波網絡:在振盪器輸出端加入 RC 低通濾波或 LC 帶通濾波電路,濾除高頻諧波分量,改善波形的正弦度。

拓展高頻應用範圍,採用高頻 RC 結構:選用高頻特性好的運算放大器(如帶寬≥10MHz 的高速運放)作為放大核心,減小分佈電容影響(如縮短佈線、使用屏蔽外殼),使 RC 振盪器可工作在 1-10MHz 範圍。

與其他振盪器結合:在高頻場景下,可採用 "RC 振盪器 + 倍頻電路" 方案,先用 RC 振盪器產生中低頻信號,再通過鎖相環倍頻至高頻,兼顧 RC 的寬調節範圍和高頻輸出需求。

3. 應用場景與選型建議

1. 使用內部晶振的場景

• 低成本的消費類電子(玩具、遙控器、電子秤)。

• 啓英泰倫語音芯片作為主控且無需通訊的產品應用(燈具、風扇)

• 對時鐘精度不敏感的功能、簡單邏輯控制(如LED閃爍、電機啓停)。

• 低速通信(UART、I2C在短距離且無嚴格同步要求時)。

2. 必須使用外部晶振的場景

• 高速通信接口(USB 2.0/3.0、Ethernet、CAN FD)。

• 無線協議(Wi-Fi、藍牙、LoRa需精確的射頻載波)。

• 音頻處理(I2S接口的48kHz/96kHz採樣率)。

• 工業自動化(PLC、伺服電機控制)。

• 汽車電子(ECU需通過AEC-Q100認證)。

• 寬温環境(-40°C\~125°C的工控場景)。

• 分佈式系統(多MCU、FPGA需共享同一時鐘源)。

在必須使用外部晶振的場景下錯誤的選擇了內部晶振可能導致的問題有:通訊時好時無,無線通訊頻繁掉線,高温環境功能異常,因此一點要根據產品的功能和使用環境綜合選擇。更多產品和方案請登錄【啓英泰倫官網】:

https://www.chipintelli.com。啓英泰倫平台通過靈活的時鐘架構和智能軟件方案,為客户提供了從低成本到高可靠性的全系列選擇。

4. 設計注意事項

4.1. 內部晶振的注意事項:

1、芯片內置的RC振盪器會隨環境温度變化產生一定的温漂。該時鐘温漂可能對需要高精度時鐘的應用,或者與上位機串口通信的準確率帶來影響。芯片在環境温度為-10 to 70°C時,RC的最大頻偏可以達到±2.5%,這時如果與之通訊的上位機MCU也採用內部RC,則雙方時鐘偏差疊加可能導致通信失敗。建議在這種情況下,使用上位機MCU的外部晶振以提高時鐘精度,或選擇啓英泰倫支持外部晶振輸入的芯片型號。此外,在設計PCB佈局時應注意將RC振盪器相關的電路遠離發熱元件,以減少温度變化對頻率穩定性的影響。

2、芯片在迴流焊接過程會產生頻偏,因為迴流焊接温度可達260度,這個温度對芯片的RC元件有一定影響,因此對於需要串口通訊的芯片需要加上串口波特率自適應算法保障通訊良好。

3、應用方案採用內部RC振盪器作為時鐘源,串口通信波特率必須小於或等於115200bps,推薦工作環境温度為-10到70℃,同時與上位機串口波特率之間總偏差不得超過4%,以保證良好通信。工作環境温度為-10到70℃的,配合的上位機串口波特率偏差在該温區須不超過±1.5%。

當上位機為免晶振設計時,需要儘量減小通訊誤差。啓英泰倫可提供串口波特率自適應方案,該方案需要在串口協議中增加一個握手指令,並且上位機保證在收到該握手指令的50ms內會按照協議要求回覆。增加該自適應方案後,產品可以用於工作環境温度為-20到85℃的場景。具體應用方法可以登錄啓【英泰倫語音AI平台】:https://aiplatform.chipintelli.com,AI平台在開發固件時可以選擇是啓用內部晶振還是外部晶振,啓用內部晶振的時候會提醒是否打開波特率自適應。

4.2. 外部晶振的注意事項:

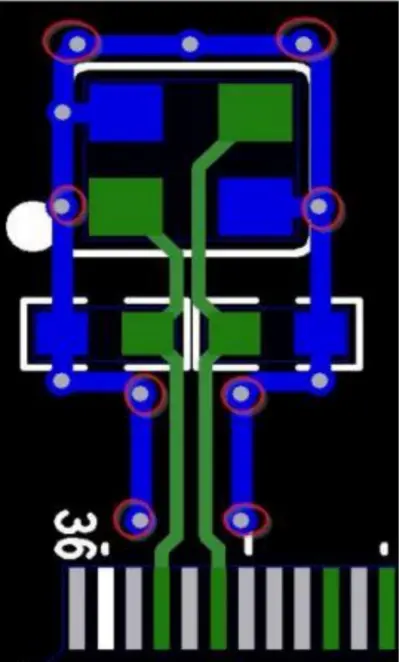

1. 晶體儘量靠近芯片引腳,走線對稱且避免平行高速信號線。參考如下圖:

2. 負載電容(CL)需根據晶體規格書計算、通用一般為22pf。

3. EMI抑制:外部晶體下方禁止走線,必要時鋪地屏蔽。有源晶振的電源需添加π型濾波器。

4. 故障排查:若外部晶振不起振,檢查負載電容值、PCB虛焊或ESD損壞。

使用示波器測量時需注意探頭電容對振盪的影響(建議使用1:1探頭)。

5. 結語

在精度與成本之間,尋求設計的平衡點

每一次產品故障的背後,都隱藏着對基礎原理的深刻考驗。本文從一次常見的通信故障入手,層層剖析,揭示了“時鐘精度” 這一在設計中容易被忽視,卻又舉足輕重的關鍵要素。

無論是集成在片內的RC振盪,還是外置的石英晶體,其本質都是在性能、成本與可靠性之間做出的智慧取捨。沒有絕對的“最優解”,只有最適合特定應用場景的“平衡點”。啓英泰倫平台提供的,正是這種從芯片到算法的全方位靈活性,讓您既能利用內部晶振實現極致的成本控制,也能借助外部晶振和智能算法(如波特率自適應)滿足嚴苛的性能要求。

希望本文能成為您產品設計路上的一份實用指南,幫助您在項目伊始就構築起對時鐘風險的“免疫力”。讓穩定可靠的通信,成為您產品值得信賴的底色。