第二章 初識ESP32-P4

在本章中,我們將深入探索ESP32-P4這款備受矚目的微控制器。我們將詳細闡述其定義、核心資源、功能應用,以及如何選擇適合您項目的ESP32-P4型號。通過本章的學習,您將全面瞭解ESP32-P4,為您的物聯網項目選擇合適的硬件平台奠定堅實基礎。

本章分為如下幾個小節:

2.1 ESP32-P4概述

2.2 ESP32-P4資源概述

2.3 ESP32-P4 命名規則

2.4 ESP32-P4 功能概述

2.5 ESP32-P4 啓動流程

2.1 ESP32-P4概述

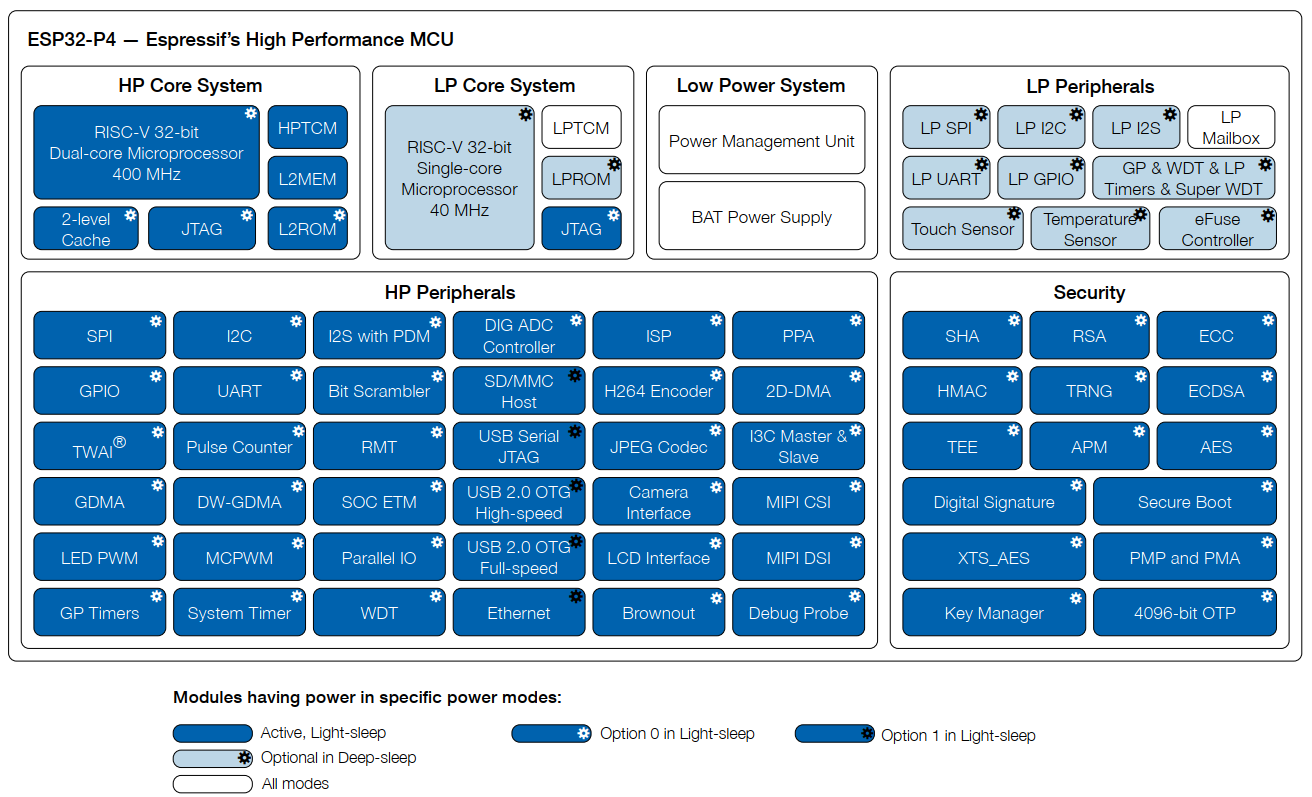

ESP32-P4是一款高性能MCU,支持超大片上內存,具有強大的圖像和語音處理能力。該款MCU包含一個高性能(HP)系統和一個低功耗(LP)系統。其中HP系統由RISC-V雙核處理器驅動,包含豐富的外設;LP系統由RISC-V單核處理器驅動,其外設針對低功耗應用進行了優化。下圖為ESP32-P4芯片的功能框圖。

圖2.1.1 ESP32-P4功能框圖

這裏,筆者結合《ESP32-P4數據手冊》中的“Product Overview”章節和上圖的內容,簡單歸納為5個部分。

1,架構和性能:ESP32-P4採用RISC-V 32位雙核處理器(HP系統,400 MHz)和單核處理器(LP系統,40 MHz),具有高效的處理能力和性能。

2,存儲:HP系統配備128 KB ROM和768 KB L2MEM,LP系統配備16 KB ROM和32 KB SRAM,支持8 KB的系統緊密耦合內存(TCM)和多個外部存儲器接口。

3,外設:提供55個可編程GPIO和多個高級外設接口,包括JPEG解碼器、視頻編碼器和多種數字接口與模擬接口,增強系統的靈活性和擴展性。

4,通信:同時支持多種通信協議,如USB、以太網、SPI、UART等,適用於物聯網設備在智能家居和工業自動化等領域的廣泛應用。

5,安全機制:具備安全啓動、一次性寫入安全性(eFuse OTP)和加密硬件加速器,確保數據和系統的安全性。

ESP32-P4是一款功能強大、性能豐富的物聯網芯片,適用於各種物聯網和音視頻等應用場景。以上信息僅供參考,如需瞭解更多信息,請訪問樂鑫公司官網查詢相關資料。

2.2 ESP32-P4資源概述

ESP32-P4芯片為開發者提供了豐富的硬件資源和高靈活度的管腳功能,以適應多種物聯網應用需求。本章節將介紹芯片的管腳佈局以及各個IO管腳的功能,幫助開發者更好地理解如何高效利用這些資源。

2.2.1 管腳佈局概覽

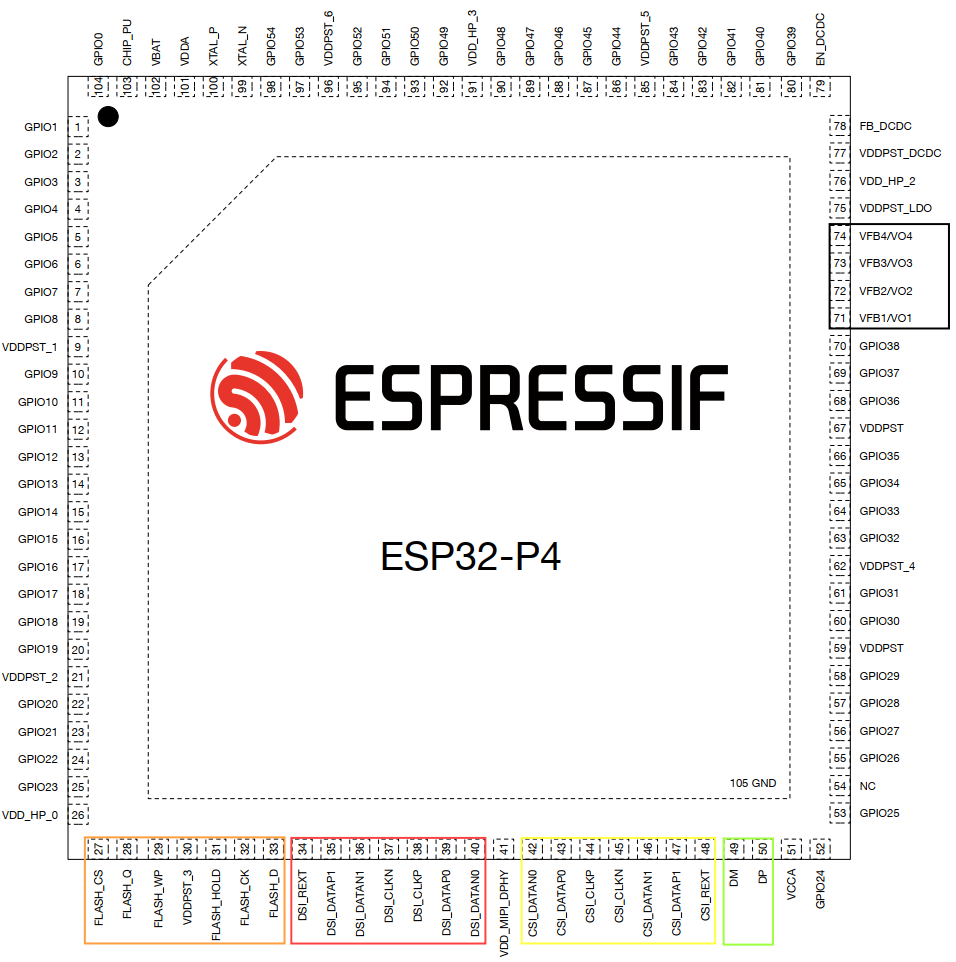

下圖為ESP32-P4管腳分佈圖。

圖2.2.1.1 ESP32-P4管腳佈局(俯視圖)

上圖中,ESP32-P4芯片總共有104個管腳,這些管腳可分為以下幾類:

1,IO管腳:上圖中的GPIO0~GPIO54,這些IO具有以下預設功能:

1)所有IO管腳均預設了HP IO MUX功能。

2)部分IO管腳預設了LP IO MUX功能。

3)部分IO管腳預設了模擬功能。

關於HP IO MUX、LP IO MUX和模擬功能的詳細信息,將在後面的2.4.3小節中進行講解。

2,專用數字管腳:僅可用於特定外設,如Flash、MIPI DSI、MIPI CSI等。這些管腳在上圖中用橙色、紅色、黃色和綠色框框標識。

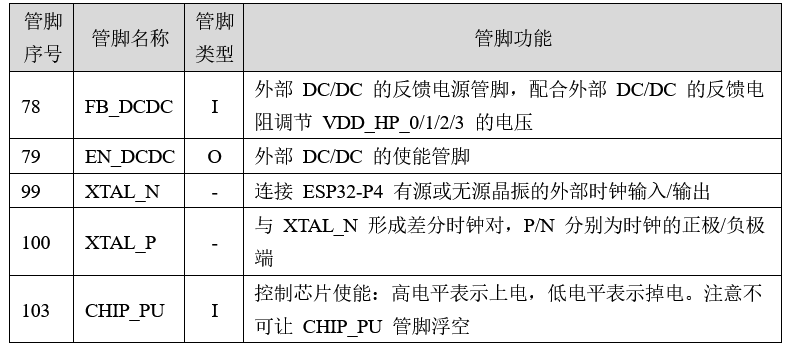

3,特殊模擬管腳:專用於特殊模擬功能。上圖78、79、99、100、103號管腳為特殊模擬管腳,這些特殊模擬管腳描述如下表所示。

圖2.2.1.1 模擬管腳

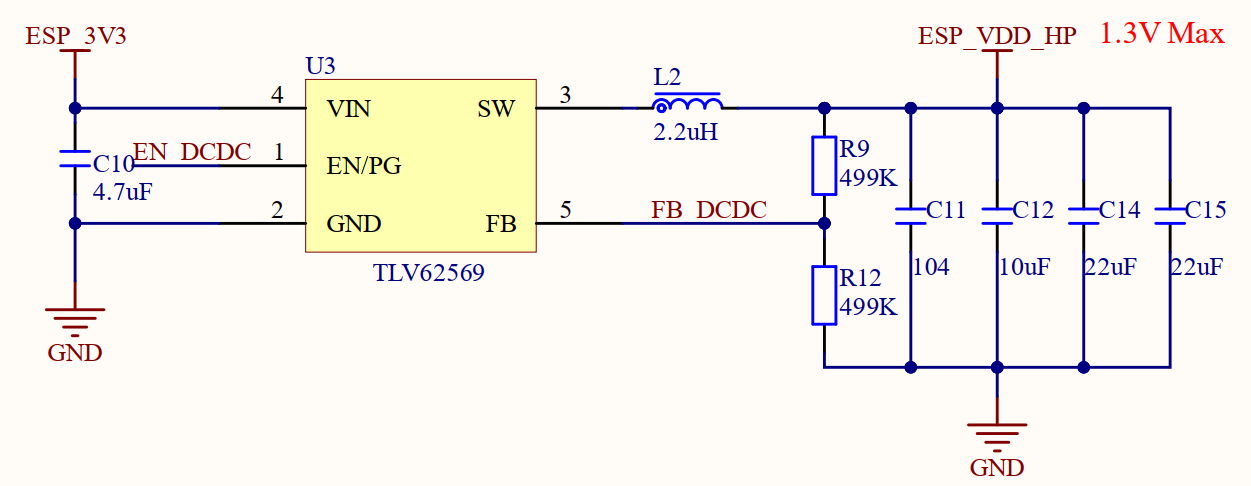

上表展示了ESP32-P4芯片提供的一些特殊模擬管腳,用於特定的電源管理和時鐘功能。其中,XTAL_N和XTAL_P需要連接一個40MHz晶振,以啓動ESP32-P4芯片。CHIP_PU管腳用於芯片的使能控制,必須進行上拉才能啓動芯片。EN_DCDC管腳用於控制同步降壓DC-DC轉換器。FB_DCDC管腳與內部參考電壓進行比較,使控制器能夠調整EN_DCDC管腳的佔空比,以穩定輸出電壓。下圖為DNESP32P4開發板中的同步降壓DC-DC轉換原理圖。

圖2.2.1.2 同步降壓DC-DC轉換

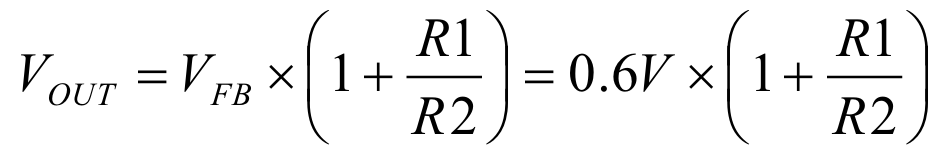

用户可以在其他平台上找到TLV62569 DC-DC電源芯片的數據手冊。在手冊的第9頁中,有一個相關的轉換公式,如下圖所示。

圖2.2.1.3 TLV62569 DC-DC電源芯片轉換公式

在上圖中,R1和R2分別對應原理圖中的R9和R12。根據該公式計算,得出Vout為1.2V,從而為HP系統的內核提供所需電壓。

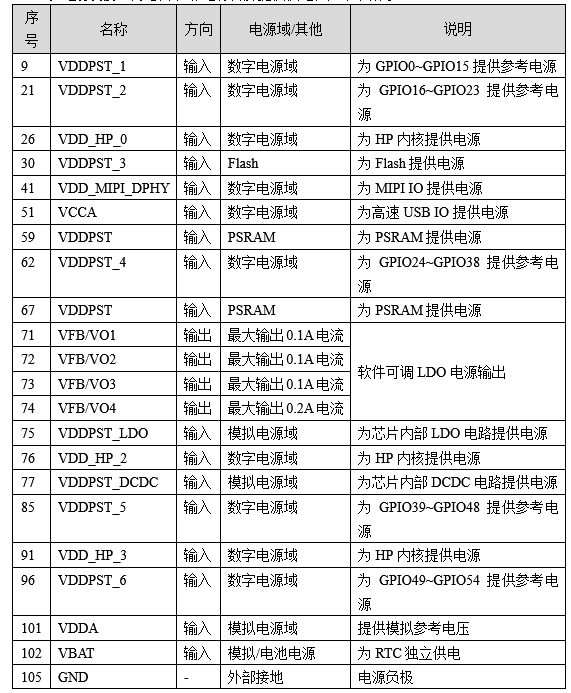

4,電源管腳:為芯片和非電源管腳提供供電,如下表所示。

表2.2.1.2 電源管腳

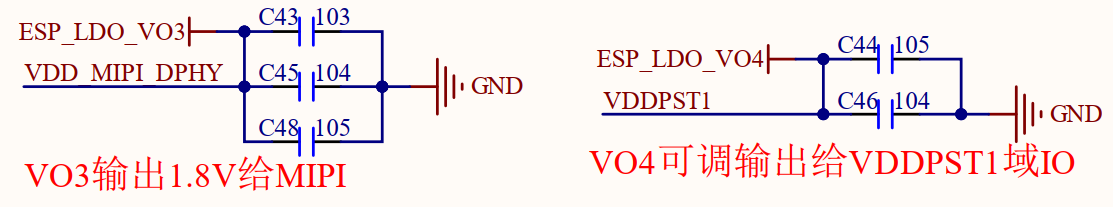

通過控制VDDPST_1至VDDPST_6管腳,用户可以靈活調整各IO管腳的輸出電壓,以滿足不同外設的電壓需求。此外,VFB/VO1至VFB/VO4(圖2.2.1.1中用黑色框框標識)管腳可以通過程序調節內部LDO的輸出電壓。通常情況下,我們將VFB/VO1至VFB/VO4連接到VDDPST_1至VDDPST_6的IO管理電源域,這樣可以通過程序控制特定IO管腳的輸出電壓。為了讓讀者更好地理解這一功能,我們在DNESP32P4開發板上將VFB/VO3和連接至VDD_MIPI_DPHY以及將VFB/VO4和連接至VDDPST_1,這樣便可以通過程序靈活控制MIPI和VDDPST_1電源域中IO的電壓了。下圖為可調LDO控制電源域原理圖。

圖2.2.1.4 通過VO3來控制MIPI電源域的IO

有些讀者可能會有疑問?為什麼需要這個功能呢?。其實很多器件不一定用到3.3V電壓啓動的,就比如我們正點原子的MIPI顯示屏,驅動的IO電平必須是1.8V,所以我們可以通過可調LDO來控制這些不同電壓驅動IO器件。

2.2.2 IO管腳功能説明

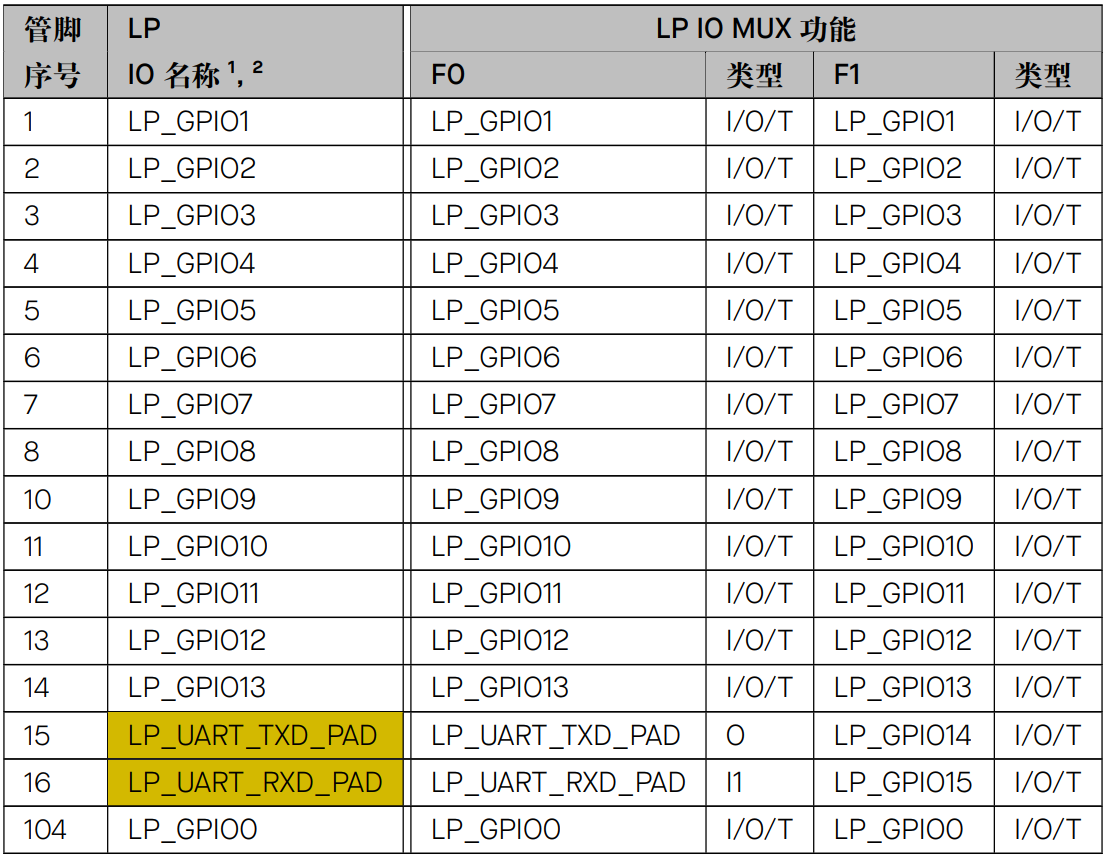

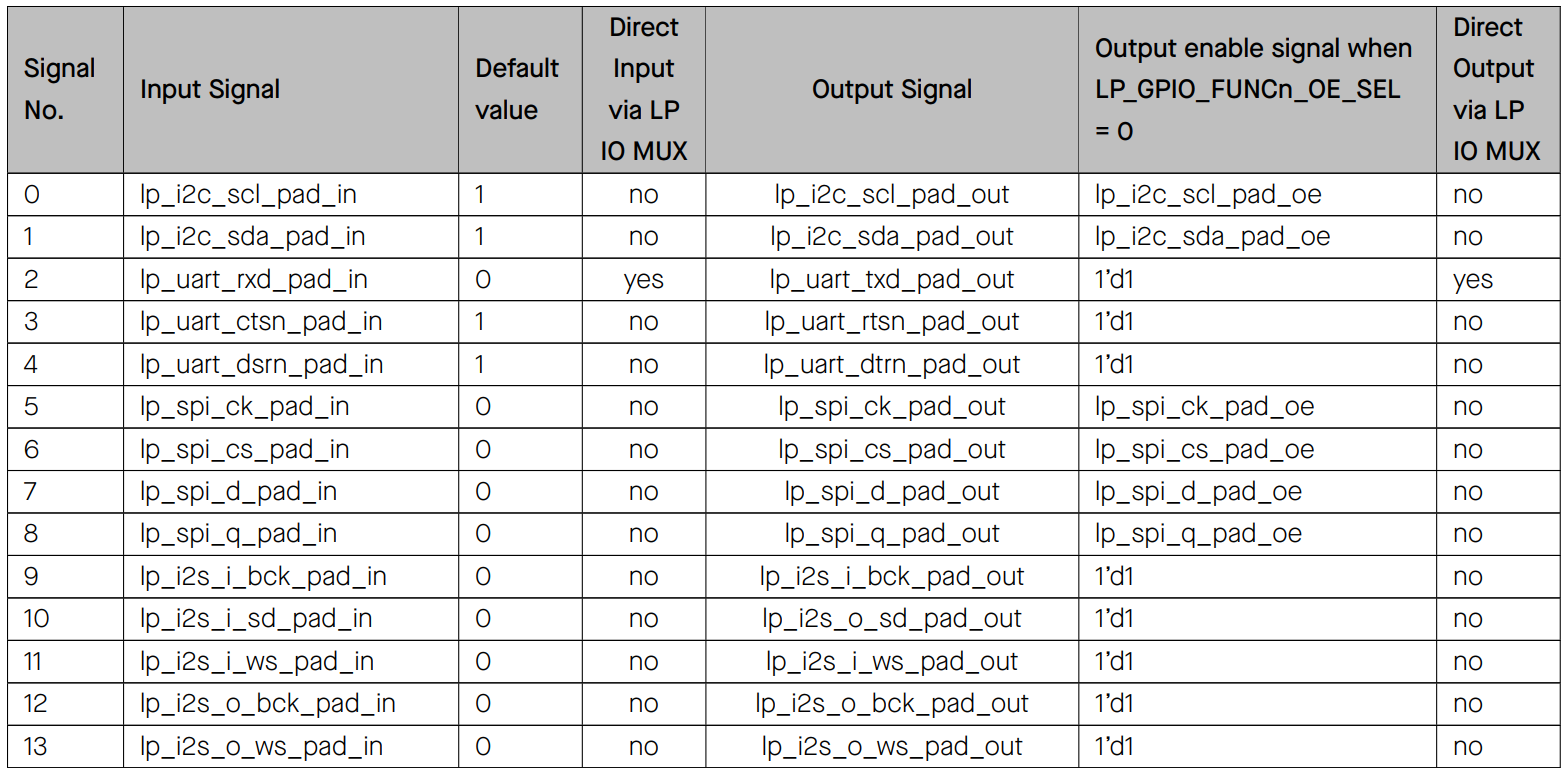

在上小節中,我們瞭解到ESP32-P4具有55個可編程IO管腳(GPIO0~GPIO54)。這些IO管腳具有三種預設功能,分別為全部IO管腳的IO MUX功能、部分IO管腳的LP IO MUX功能和部分IO管腳的模擬功能。如下表所示。

表2.2.2.1 部分外設管腳分配

從上表可知,ESP32-P4的IO MUX功能使得所有GPIO管腳能夠靈活配置為多種數字信號接口,例如UART、I2S、I2C等,利用ESP32-P4的55個任意IO實現相關通信信號;與此同時,部分IO管腳的LP IO MUX功能專為低功耗應用設計,允許某些管腳在待機狀態下保持活躍,以支持LP I2C和LP I2S等通信方式,從而有效節省能耗(如下圖為LP系統管理的IO);此外,部分GPIO管腳具備模擬功能(如表中的ADC和TOUCH管腳,其他IO則不具備此功能),能夠處理連續信號,直接與傳感器和音頻設備交互,拓展了ESP32-P4在多樣化應用場景中的適用性。

圖2.2.2.1 LP系統管理的IO

如果LP系統啓動時,我們可以利用上圖的IO管腳實現I2C、I2S等多種通信,因為這些信號可以靈活地映射到任意的IO管腳上。這種靈活性使得我們能夠根據具體需求驅動相應的器件,從而更好地適應不同的應用場景和設計要求。

值得注意的是,某些外設必須使用特定的管腳實現,例如具有調試功能的JTAG、USB串口/JTAG、全速USB 2.0和EMAC等。如果在開發時未使用這些外設,我們可以利用IO MUX功能對特定通信接口進行映射。然而,這些映射可能會影響傳輸速率,因此筆者建議開發者首先採用ESP32-P4默認的複用功能IO設計原理圖,然後再考慮其他IO映射功能,以確保系統性能的穩定性和可靠性。

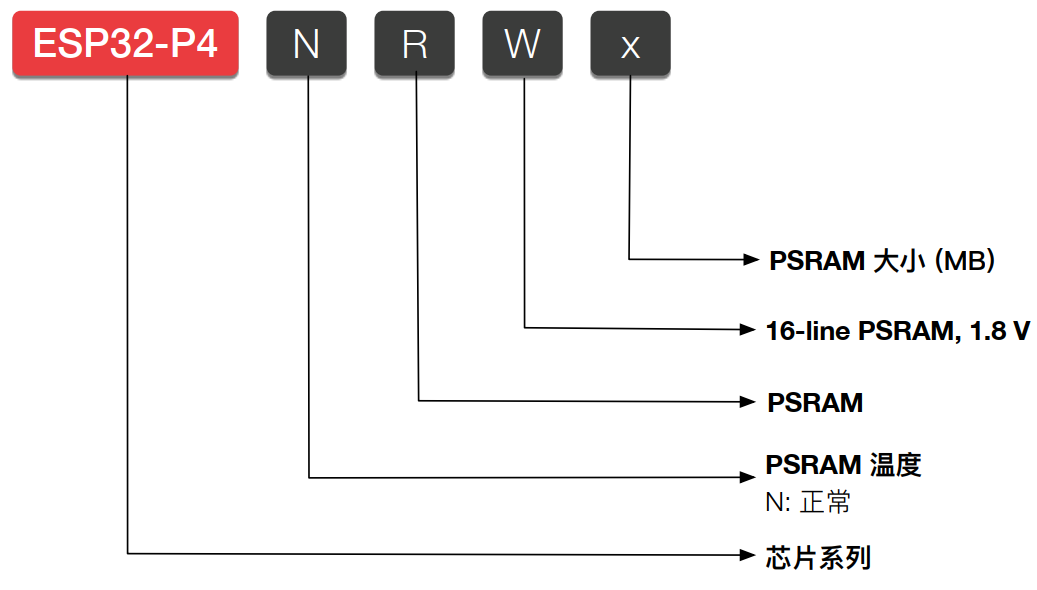

2.3 ESP32-P4 命名規則

樂鑫P4系列包含兩款芯片:ESP32-P4NRW16和ESP32-P4NRW32,它們之間的唯一差異在於PSRAM容量。以下是這兩款芯片的命名規則圖示。

圖2.3.1 ESP32-P4 系列芯片命名規則

從上圖可以看到, H/N表示FLASH温度(H:高温,N:常温);R表示內置PSRAM;W表示僅持1.8v 16-line PSRAM;x表示內置PSRAM大小(MB);。

2.4 ESP32-P4 功能概述

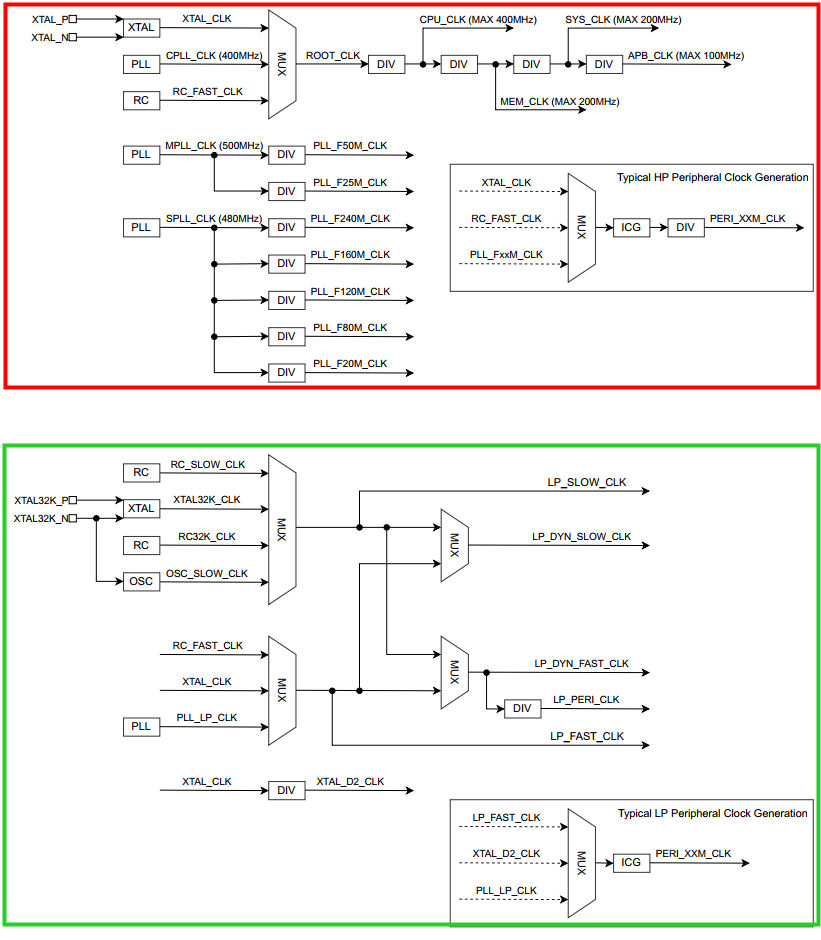

2.4.1 時鐘樹

ESP32-P4的時鐘主要來源於振盪器(oscillator,OSC)、 RC振盪電路和PLL時鐘生成電路。上述時鐘源產生的時鐘經時鐘分頻器或時鐘選擇器等時鐘模塊的處理,使得大部分功能模塊可以根據不同功耗和性能需求來獲取及選擇對應頻率的工作時鐘。下圖為ESP32-P4系統時鐘結構。

圖2.4.1.1 HP和LP系統時鐘樹

在上圖中,十多路時鐘源通過分頻器或直接連接的方式供給各個外設。這樣,各模塊可根據功耗和性能需求,選擇和獲取相應的工作時鐘頻率。

接下來,筆者根據HP系統和LP系統的應用不同,劃分為兩個類型的時鐘。

1,高速時鐘

1)CPLL_CLK:內部400MHz時鐘,CPU主頻可由該時鐘提供。

2)MPPL_CLK:內部500MHz時鐘,PSRAM_CLK可由該時鐘提供。

3)SPLL_CLK:內部480MHz時鐘,FLASH_CLK/PSRAM_CLK可由該時鐘提供。

2,慢速時鐘

1)XTAL32K_CLK:外部32KHz石英晶振時鐘。

2)RC_SLOW_CLK:內部慢速RC振盪器,頻率可調,默認150KHz。

3)RC32K_CLK:內部32KHz RC振盪器。

4)XTAL_CLK:40MHz外部石英晶振時鐘。

5)RC_FAST_CLK:內部快速RC振盪器,頻率可調,默認20MHz。

6)PLL_LP_CLK:內部PLL時鐘,默認為8MHz。

其中,高速時鐘用於HP系統及其數字/模擬外設,而慢速時鐘則用於LP系統以及某些低功耗模式下的外設。由此可見,我們可以將上圖2.4.1.1劃分為兩個部分:上部分(紅色區域)為HP系統所需的時鐘,下部分(綠色區域)為LP系統所需的時鐘。

前面我們已經瞭解到,ESP32-P4芯片集成了高性能(HP)系統和低功耗(LP)系統。其中,HP系統的主頻最高可達400MHz,而LP系統的主頻最高則為40MHz。那麼,如何配置這兩個系統以達到其最高主頻呢?接下來,筆者將結合《ESP32-P4技術參考手冊》,詳細講解這兩個系統的主頻配置方法。

1,HP系統時鐘配置

由上圖紅色區域可知,CPU_CLK是HP系統的主頻時鐘,由XTAL_CLK、CPLL_CLK和RC_FAST_CLK這三個時鐘源提供(LP_CLKRST_HP_CLK_CTRL_REG寄存器中的第0~1位(即LP_CLKRST_LP_CLK_SEL字段)來選擇時鐘源)。若要將HP系統的主頻配置為400MHz,則必須選擇CPLL_CLK作為時鐘源,並將其頻率設置為400MHz。此時,分頻器(DIV)不進行分頻(即1分頻,意味着直接傳遞原頻率),從而確保CPU_CLK的頻率為400MHz。

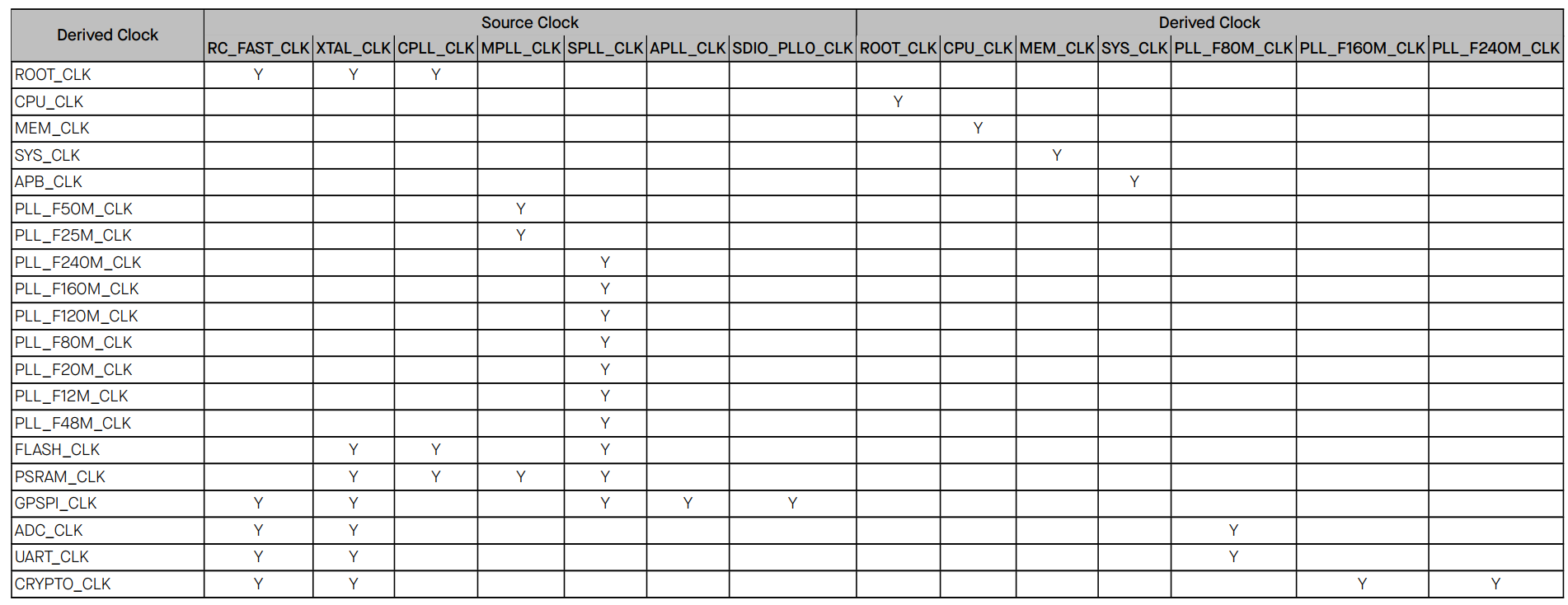

MEM_CLK、SYS_CLK和APB_CLK時鐘則是由CPU_CLK時鐘經過分頻得到的。另外,MPLL_CLK和SPLL_CLK也會經過分頻器(DIV)進行分頻,以產生不同頻率的時鐘信號。這些時鐘信號被提供給HP系統的各個模塊,各模塊根據自身的功耗和性能需求來選擇相應的時鐘頻率。下圖是派生的HP時鐘源。

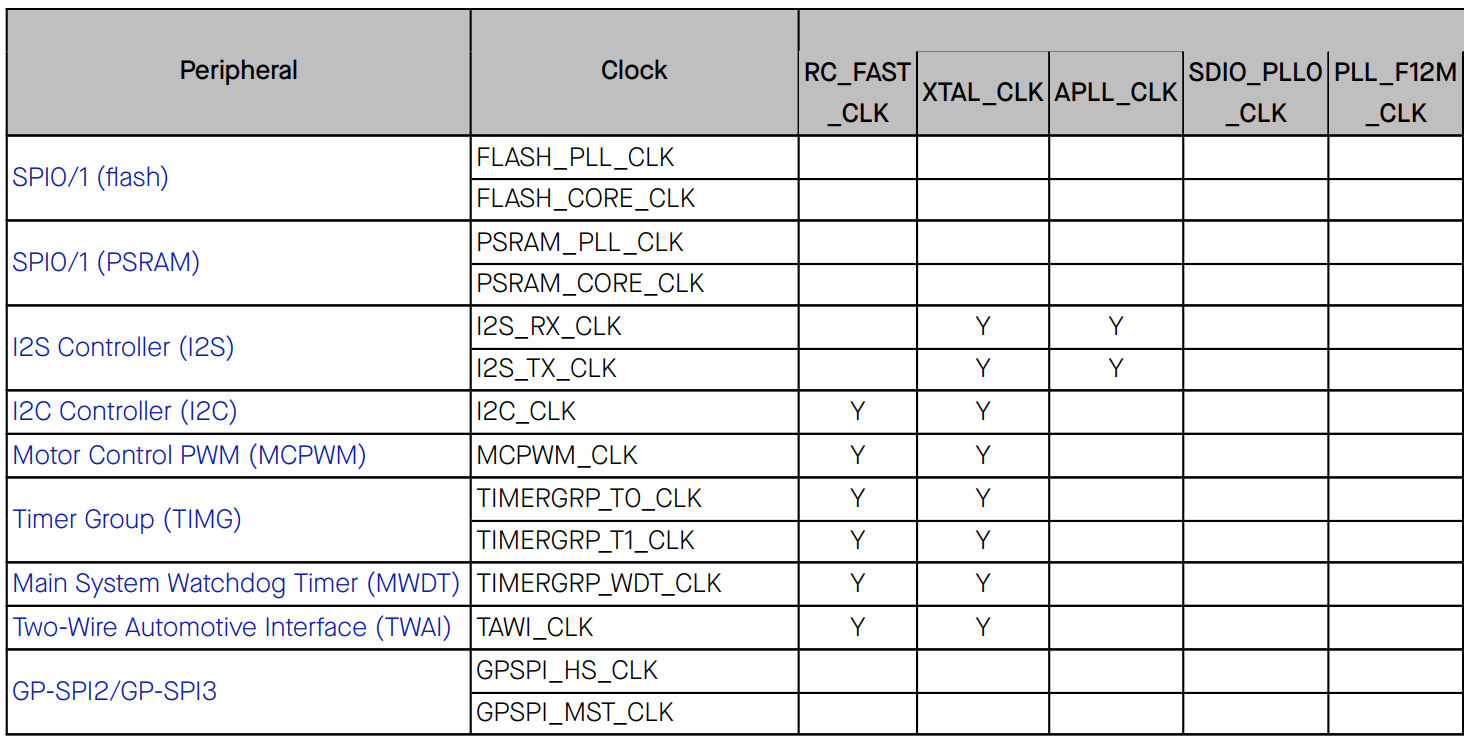

圖2.4.1.2 派生的HP時鐘源

上圖中,左邊“Source Clock”為原始時鐘源,右邊“Derived Clock”為派生時鐘源(由原始時鐘源經過分頻得到)。下圖為HP系統外設時鐘源選擇。

圖2.4.1.2 HP系統外設時鐘源選擇(部分截圖)

關於ESP32-P4的HP系統外設時鐘源選擇,可以參考《ESP32-P4技術參考手冊》中的453頁8.2-4和8.2-5表格。

2,LP系統時鐘配置

由上圖綠色區域可知,在“active”模式下,LP_FAST_CLK是LP系統(低功耗系統)的主頻時鐘,它由XTAL_CLK、RC_FAST_CLK和PLL_LP_CLK這三個時鐘源提供。我們可以通過操作LP_CLKRST_LP_CLK_CONF_REG寄存器中的第0~1位(即LP_CLKRST_LP_CLK_SEL字段)來選擇時鐘源。若要將LP系統的主頻配置為40MHz,則必須選擇XTAL_CLK作為時鐘源,並將其頻率設置為40MHz。

在‘Light-sleep’或‘Deep-sleep’模式下,一般選擇LP_SLOW_CLK作為時鐘源,該時鐘由RC_SLOW_CLK、XTAL32K_CLK、RC32K_CLK和OSC_SLOW_CLK這四個低頻時鐘源提供。我們可操作LP_CLKRST_LP_CLK_CONF_REG寄存器中的第0~1位(即LP_CLKRST_SLOW_CLK_SEL字段)來選擇時鐘源。下圖是派生的LP時鐘源。

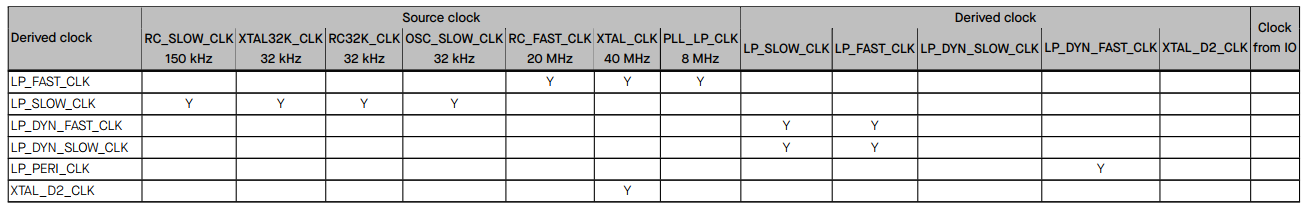

圖2.4.1.3 派生的LP時鐘源

上圖中,左邊“Source Clock”為原始時鐘源,右邊“Derived Clock”為派生時鐘源(由原始時鐘源經過分頻得到)。下圖為LP系統外設時鐘源選擇。

圖2.4.1.4 LP系統外設時鐘源選擇

關於ESP32-P4的LP系統外設時鐘源選擇,可以參考《eESP32-P4技術參考手冊》中的455頁8.2-7表格。

2.4.2 系統與內存

在ESP32-P4芯片中,系統架構設計和內存佈局為高效處理和多任務併發提供了基礎。前面講解過,該芯片集成了高性能(HP)和低功耗(LP)兩種RISC-V處理器,配合多級內存結構與豐富的外設支持,適用於各種物聯網和嵌入式應用場景。

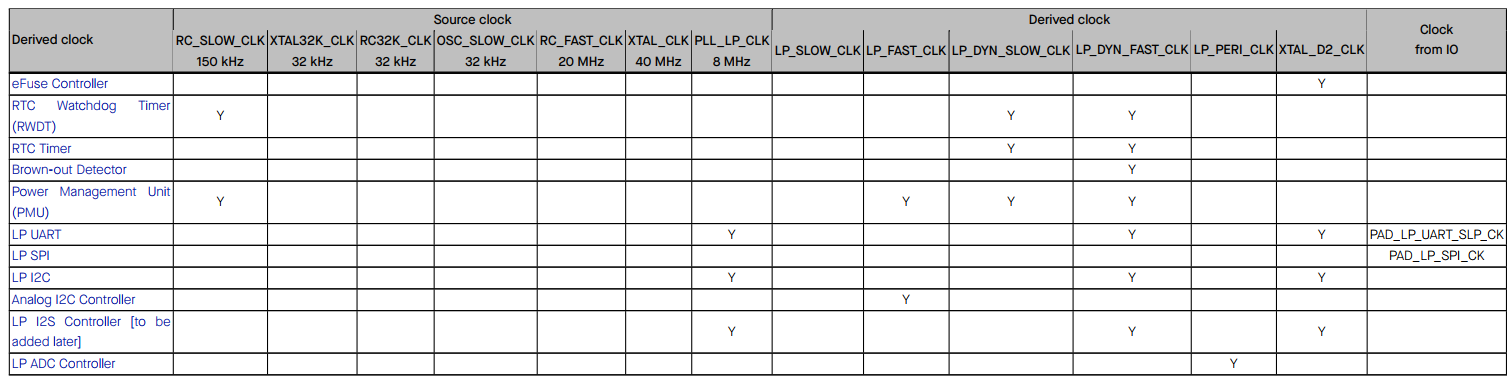

下圖展示了ESP32-P4的系統結構和地址映射。ESP32-P4的指令總線和數據總線共享同一地址空間,這意味着所有非保留的地址都可以通過這兩條總線進行訪問。這種設計提高了系統在執行指令和訪問數據時的靈活性。在分析下圖之前,我們需要先了解兩個關鍵概念:總線結構與端序,以及數據訪問對齊。

1,總線結構與端序

在ESP32-P4中,HP CPU和LP CPU的指令總線和數據總線均採用小端序(little-endian)。其中,HP CPU的數據總線(DBUS)具有128位的數據寬度,而其他總線的數據寬度為32位。

2,數據訪問對齊

1)HP CPU:通過數據總線訪問數據時,支持單字節(1字節)、雙字節(2字節)和4字節對齊。此外,在執行AI指令時,HP CPU的數據對齊需求最高可達16字節,這為高效的AI計算提供了支持。

2)LP CPU:支持單字節、雙字節和4字節對齊的數據訪問。

這種對齊方式的設計,尤其是HP CPU的多字節對齊支持,使得ESP32-P4在高性能計算和數據處理任務中能夠更有效地利用內存帶寬和系統資源。

圖2.4.2.1 ESP32-P4 系統結構與地址映射

上圖展示了ESP32-P4的系統結構和地址映射。以下是對該圖所示系統結構和地址映射的逐步解剖。

1,處理器結構

ESP32-P4芯片包含以下兩種處理器:

1)高性能(HP)CPU:32位RISC-V雙核處理器,主頻高達400 MHz,採用五級流水線結構。HP CPU適用於計算密集型任務,支持對高速緩存和大容量外部存儲的快速訪問。

2)低功耗(LP)CPU:32位RISC-V單核處理器,主頻40 MHz,採用兩級流水線結構。LP CPU功耗較低,適合執行低速率、低功耗任務,通常用於待機或低頻應用。

這種雙處理器架構允許系統在功耗和性能之間靈活切換,為任務分配和資源管理提供了更高的靈活性。

2,內存結構

ESP32-P4的內存結構由多層次的內部存儲器和可外擴的存儲器組成,允許高效的數據處理和存儲訪問。

1)HP CPU內存訪問:

HP TCM(緊耦合內存):8 KB,地址範圍為0x30100000~0x30101FFF,供HP CPU快速訪問,適合存儲時間敏感的數據或指令。

①:HP ROM(只讀存儲器):128 KB,分為兩種訪問方式,一種是緩存訪問地址,通過Cache進行緩存訪問(0x4FC000000x4FC1FFFF),另一種是直接訪問地址(0x8FC000000x8FC1FFFF)。HP ROM存儲區是用於系統啓動代碼和初始化程序。

②:HP L2MEM(二級緩存內存):768 KB,分為兩種訪問方式,一種是緩存訪問地址(0x4FF000000x4FFBFFFF),另一種是直接訪問地址(0x8FF000000x8FFBFFFF)。

③:外部存儲器:

外部Flash(External flash):最大64 MB,供程序代碼和非易失性數據存儲,地址範圍為:

緩存訪問地址:0x40000000~0x43FFFFFF。

直接訪問地址:0x80000000~0x83FFFFFF。

外部RAM(External RAM):最大64 MB,適合存儲大量數據或臨時緩存,地址範圍為:

緩存訪問地址:0x48000000~0x4BFFFFFF。

直接訪問地址:0x88000000~0x8BFFFFFF。

2)LP CPU內存訪問:

①:LP ROM:16 KB,地址範圍為0x50100000~0x50103FFF,存儲啓動代碼和初始化程序。

②:LP SRAM:32 KB,地址範圍為0x50108000~0x5010FFFF,為LP CPU提供的低功耗快速訪問存儲。

③:共享訪問:LP CPU還可以訪問HP ROM、HP L2MEM和外部存儲器(地址與HP CPU相同),從而增強數據共享和協同處理能力。

3,外設地址映射

ESP32-P4芯片的外設模塊具有獨立的地址空間,為處理器和外設間的通信提供了便利。

1)HP CPU外設:地址範圍為0x3FF00000~0x3FF1FFFF。

2)HP外設:地址範圍為0x50000000~0x500FFFFF。

3)LP外設:地址範圍為0x50110000~0x5012FFFF。

通過這種獨立的地址劃分,ESP32-P4的處理器能夠高效管理多個外設,減少總線衝突,並優化訪問延遲。關於外設地址映射的詳細信息,請參考《ESP32-P4技術參考手冊》第5章《System and Memory》中的5.3.5小節《Modules/Peripherals Address Mapping》,該小節已詳細講解了各個外設的映射地址。

4,地址配置

ESP32-P4內存的地址空間可以通過不同方式進行訪問,其中緩存訪問和直接訪問的分佈設計可以滿足不同任務的需求:

1)緩存訪問:地址以0x4xxx_xxxx開頭的區域可以配置為緩存訪問,通過處理器的PMU(性能監控單元)進行管理,以提高訪問速度。

2)直接訪問:地址以0x8xxx_xxxx開頭的區域提供直接訪問,通常用於調試或需要低延遲訪問的場景。

通過這種靈活的訪問配置,ESP32-P4芯片支持在不同存儲設備和數據類型之間快速切換,提升了數據的讀取和寫入效率。

至此,ESP32-P4的系統與內存相關知識講解完畢。如需深入瞭解更多系統與內存的細節,請參考《ESP32-P4技術參考手冊》中的第5章《System and Memory》。

2.4.3 IO MUX和GPIO交換矩陣

GPIO(通用輸入輸出)引腳作為芯片與外部設備交互的關鍵接口,為了支持多種外設和應用需求,GPIO引腳需要靈活地連接到不同的外設信號上。ESP32-P4芯片通過高功率(HP)和低功率(LP)兩種GPIO矩陣和IO MUX(輸入輸出複用器)系統,實現了對GPIO引腳的靈活配置,使其可以與多達數百個外設信號相互連接,並且可以支持信號同步、濾波、直連等多種功能。瞭解IO MUX和GPIO矩陣的架構和功能,有助於開發者靈活配置ESP32-P4的引腳資源,滿足不同應用場景的需求。

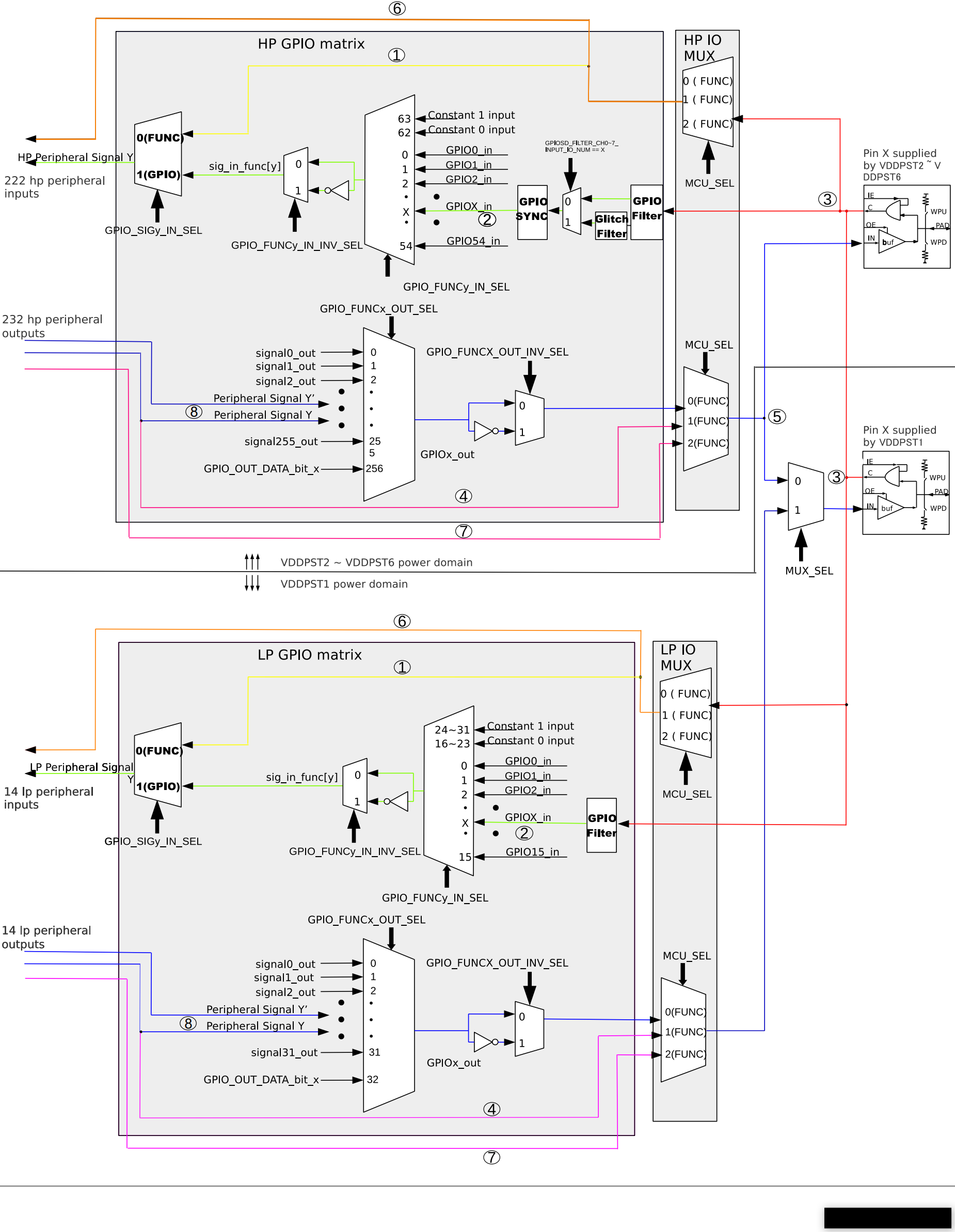

本章節將詳細介紹ESP32-P4中的HP和LP GPIO矩陣以及對應的IO MUX的工作原理、架構以及信號的路由方式,並對其主要特性進行分析。下圖為ESP32-P4的IO MUX和GPIO交換矩陣整體框架。

圖2.4.3.1 IO MUX和GPIO交換矩陣整體框架

上圖是ESP32-P4的HP GPIO矩陣、HP IO MUX、LP GPIO矩陣和LP IO MUX的結構,詳細描述了信號從引腳到外設以及從外設到引腳的路由方式。下面我們先了解比較重要的模塊相關特性,然後再去了解信號從引腳到外設和外設到引腳的路由方式。

1,HP GPIO Matrix特性

圖2.4.3.1中的HP GPIO矩陣是用於將HP外設信號與GPIO引腳連接,它具有以下特點:

1)全交換矩陣:支持HP外設信號與GPIO引腳之間的全交換配置,靈活處理輸入輸出。

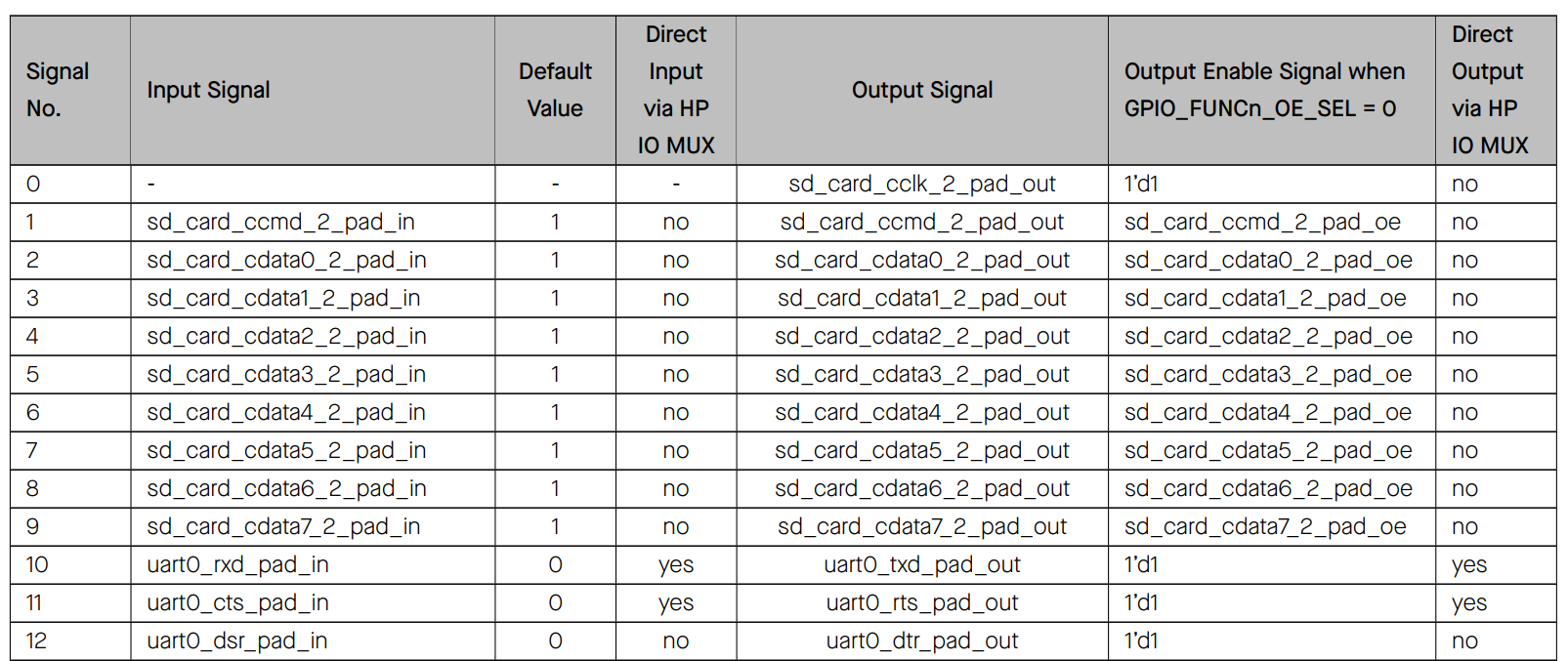

2)HP外設輸入:可支持222個HP外設輸入信號,靈活路由到任意GPIO引腳。這222個HP外設輸入信號可查看《ESP32-P4技術參考手冊》中的7.12 HP Peripheral Signal List小節內容,如下圖所示。

圖2.4.3.2 HP外設信號列表

上圖中,左側為HP系統的外設輸入信號,而右側為HP系統的輸出信號,這些外設輸入輸出可使用任意IO來實現。

3)HP外設輸出:支持232個HP外設輸出信號,能夠路由到任意GPIO引腳(請看上圖右側信號)。

4)信號同步:通過同步處理確保輸入信號與HP IO MUX的工作時鐘一致,穩定性高。

5)輸入信號濾波:配有GPIO濾波器進行二次過濾,有效提升信號抗干擾能力。

6)簡單輸入輸出:提供基礎的GPIO輸入輸出功能,支持常規數字輸入輸出。

2,HP IO MUX特性

圖2.4.3.1中的HP IO MUX是負責HP GPIO引腳的配置與管理,主要功能包括:

1)引腳控制:管理55個GPIO引腳(GPIO0 ~ GPIO54),用於HP外設的連接和控制。

2)配置寄存器:每個GPIO引腳配有配置寄存器(IO_MUX_GPIOn_REG),可控制引腳的輸入輸出模式、上拉/下拉、電流驅動強度及功能選擇。

3)高頻信號直連:對於高頻信號(如SPI、EMAC),可直接通過HP IO MUX連接外設,優化高頻性能。

這兩部分功能緊密配合,為ESP32-P4提供了靈活的外設信號處理和GPIO管理能力。

3,LP GPIO Matrix特性

圖2.4.3.1中的LP GPIO矩陣是用於LP外設信號提供了靈活的信號路由,適用於低功耗場景,具有以下功能:

1)全交換矩陣:支持LP外設輸入輸出信號與LP GPIO引腳之間的全交換矩陣配置。

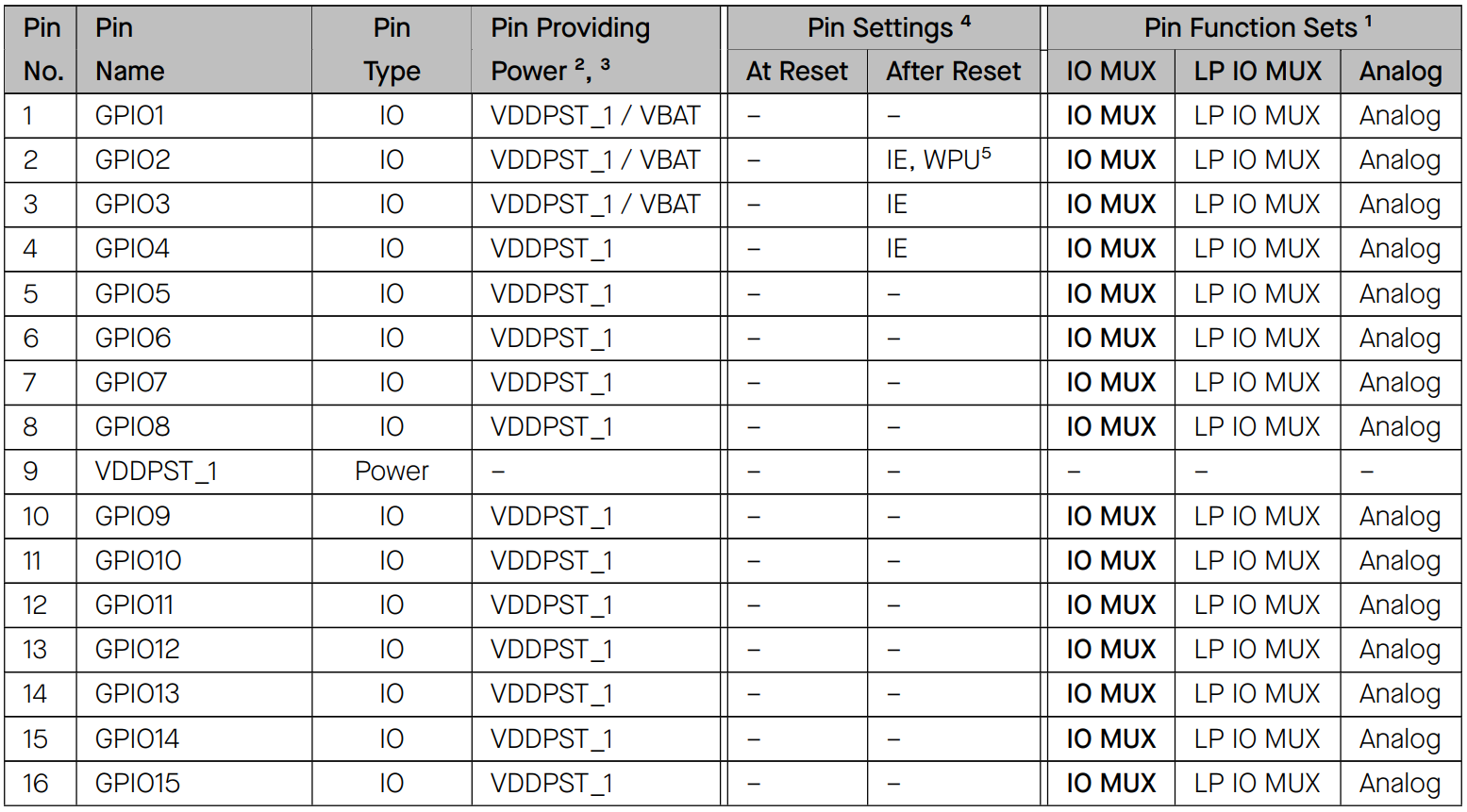

2)LP外設輸入:支持14個LP外設輸入信號,可以通過LP GPIO矩陣路由到任意LP GPIO引腳,這些外設輸入信號請看《ESP32-P4技術參考手冊》中的7.13 LP Peripheral Signal List小節內容,如下圖所示。

圖2.4.3.3 LP系統的外設信號列表

上圖中,左側為LP系統的外設輸入信號,而右側為LP系統的輸出信號,這些外設輸入輸出可使用任意IO來實現。

3)LP外設輸出:支持14個LP外設輸出信號,可以路由至任意LP GPIO引腳輸出(請看上圖右側信號)。

4)輸入信號濾波:配備GPIO濾波器,用於對輸入信號進行簡單的濾波處理,提高信號的穩定性。

5)簡單輸入輸出:支持基本的GPIO輸入輸出功能,滿足低功耗設備的輸入輸出需求。

4,LP IO MUX特性

圖2.4.3.1中的LP IO MUX是負責LP GPIO引腳的配置與管理,它的功能包括:

1)引腳控制:管理16個LP GPIO引腳(GPIO0 ~ GPIO15),用於LP外設的連接和控制。

2)配置寄存器:每個LP GPIO引腳配有配置寄存器(LP_IOMUX_PADn_REG),可用於控制引腳的輸入輸出模式、上拉/下拉、電流驅動強度、功能選擇和IO MUX選擇。

5,管腳PAD類型

在圖2.4.3.1中,ESP32-P4芯片的PAD管腳類型分為兩類電源域:VDDPST1和VDDPST2VDDPST6。VDDPST1電源域負責管理GPIO0GPIO15號管腳的電源,而VDDPST2VDDPST6電源域則負責管理GPIO16GPIO54號管腳的電源。之所以將管腳分為兩類電源域,是因為ESP32-P4在不同工作模式下對電源管理有不同的需求。在低功耗(LP)模式下,芯片只能使用由VDDPST1電源域管理的GPIO0GPIO15管腳,以最大限度減少功耗。而在高性能(HP)模式下,芯片可以使用VDDPST1到VDDPST6電源域管理的管腳,即可使用GPIO0GPIO54的全部55個可編程I/O管腳,滿足更復雜的I/O需求。這種電源域的劃分使得ESP32-P4能夠根據不同的工作狀態靈活地管理功耗,同時提供豐富的I/O資源來支持多種應用。下面為VDDPST1到VDDPST6電源域管理的管腳範圍,如下圖所示。

圖2.4.3.4 電源域管理的GPIO(部分截圖)

上圖的列表摘自《ESP32-P4數據手冊》中的2.2 Pin Overview小節,表格詳細闡述了各個電源域管理的GPIO管腳。通過控制這些電源域的電壓,我們可以相應地控制它們所管理的GPIO的輸入輸出電壓。具體來説,VDDPST1電源域管理的GPIO(GPIO0GPIO15)和VDDPST2VDDPST6電源域管理的GPIO(GPIO16~GPIO54)在工作時可根據不同電源域的電壓調節來控制相應管腳的電平狀態,從而實現精確的電壓控制與信號處理。

至此,我們已瞭解了ESP32-P4的IO MUX和GPIO交換矩陣各個模塊的功能與特性,接下來我們將介紹如何配置GPIO管腳為輸入或輸出,並將其分別與輸入信號和輸出信號進行綁定。

6,管腳的輸入輸出配置

從上述內容可以看出,配置ESP32-P4的55個可編程I/O管腳的輸入輸出模式,需要通過配置IO_MUX_GPIOx_REG和LP_IOMUX_PADx_REG寄存器來實現。其中,IO_MUX_GPIOx_REG寄存器用於配置HP系統中所有55個可編程I/O管腳的電氣特性,而LP_IOMUX_PADx_REG寄存器僅能用於配置GPIO0~GPIO15號管腳的I/O功能,適用於低功耗模式下的配置。接下來,筆者將以HP系統為例,介紹如何配置這些管腳。

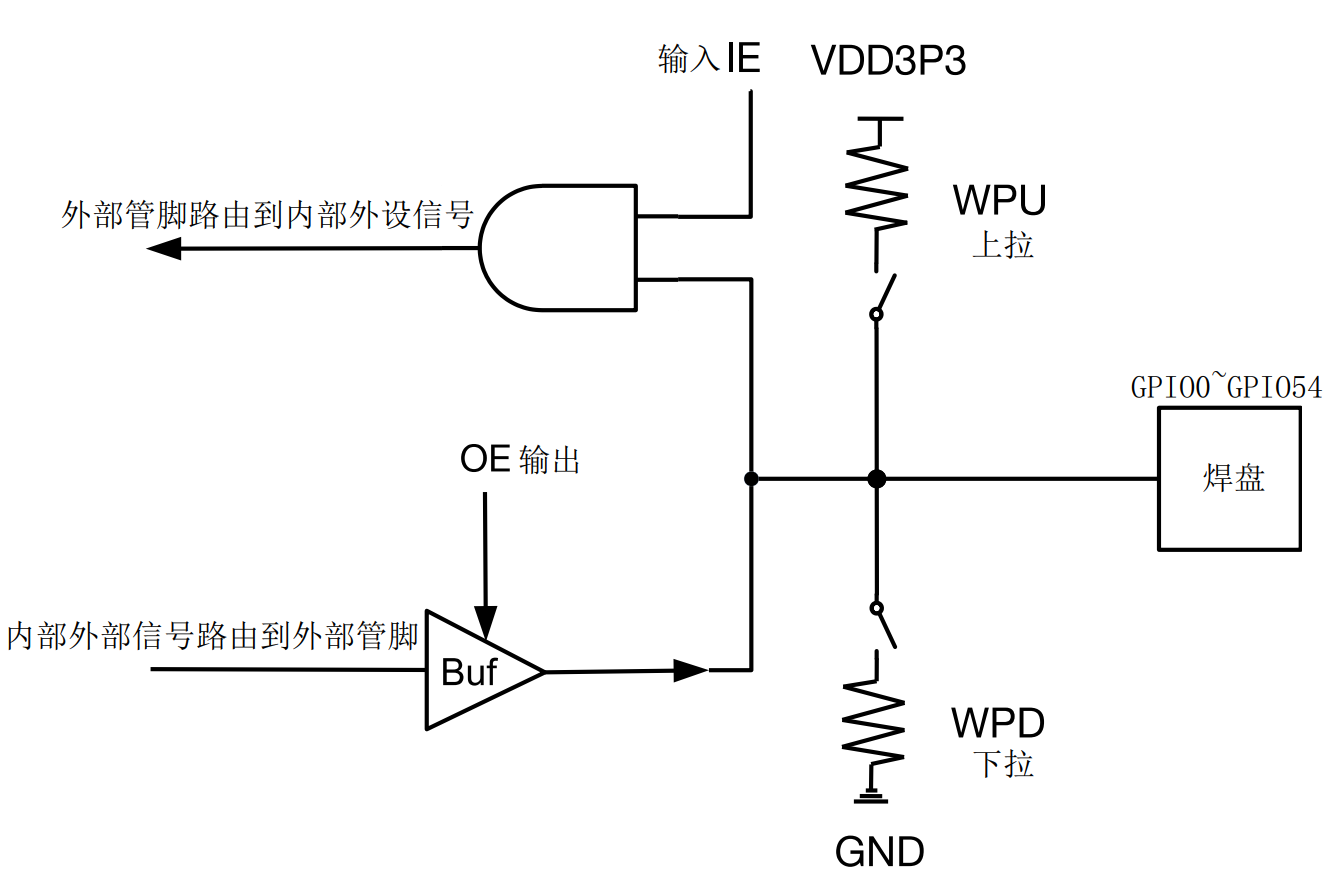

下圖為管腳PAD內部結構,如下圖所示。

圖2.4.3.4 GPIO0~GPIO54的PAD內部結構

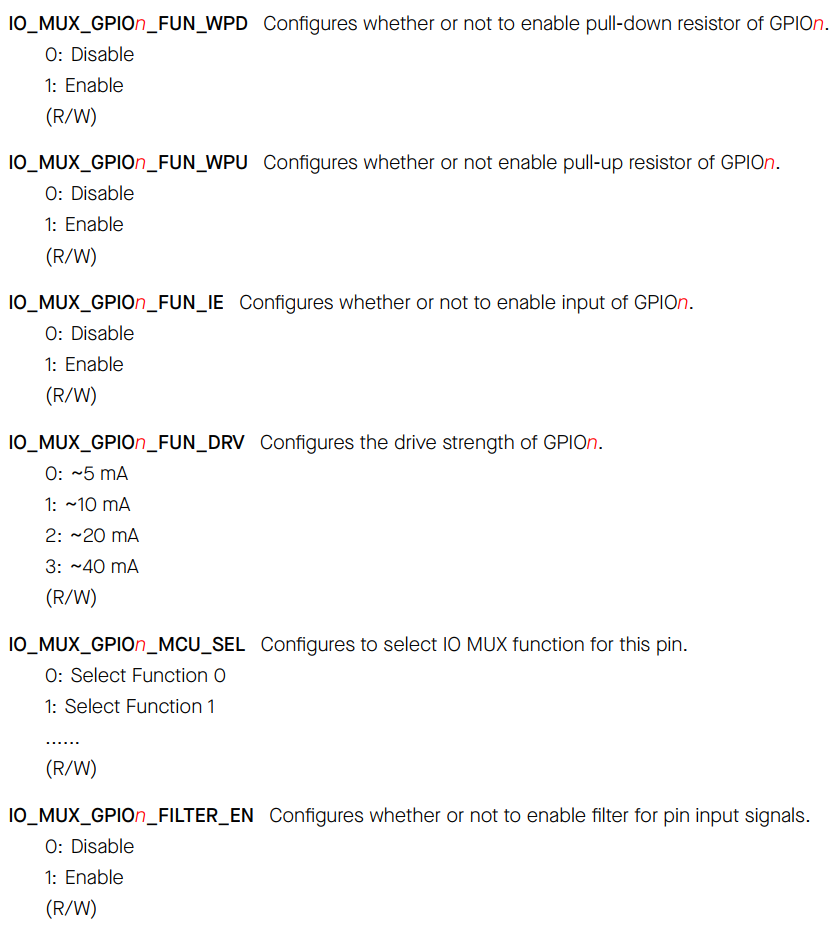

上圖展示了PAD焊盤內部結構的輸入/輸出、上拉/下拉等配置,這些配置可以通過IO_MUX_GPIOx_REG(x:0~54)寄存器來實現。該寄存器用於設置與GPIO相關的電氣屬性,如輸入輸出模式、上拉或下拉電阻等。具體的寄存器描述和配置細節如下圖所示。

圖2.4.3.5 配置GPIO輸入配置

上圖中,WPD和WPU字段用於配置GPIO的上下拉使能;IE和DRV字段用於配置GPIO的輸入使能與驅動能力;SEL和EN字段用於配置GPIO功能和是否啓動濾波器。輸出配置是由GPIO_ENABLE_REG寄存器配置的,大家可參看《ESP32-P4技術參考手冊》中的7.12 HP Peripheral Signal List小節內容。

7,管腳路由至內部外設信號

從圖2.4.3.1中可以看出,若GPIO由VDDPST2~VDDPST6電源域管理,則該GPIO的輸入信號會流經兩個方向:一條是HP IO MUX,另一條是HP GPIO matrix交換矩陣。而若GPIO由VDDPST1電源域管理,則該GPIO的輸入信號可流經四個方向:首先是HP IO MUX,其次是HP GPIO matrix交換矩陣,另外在系統處於低功耗模式(即LP系統)時,信號還將流入LP IO MUX和LP GPIO matrix交換矩陣。這些信號流向的方向可參考圖2.4.3.1中的紅色(③)箭頭。

接下來,筆者以VDDPST2~VDDPST6電源域管理的GPIO為例進行説明。

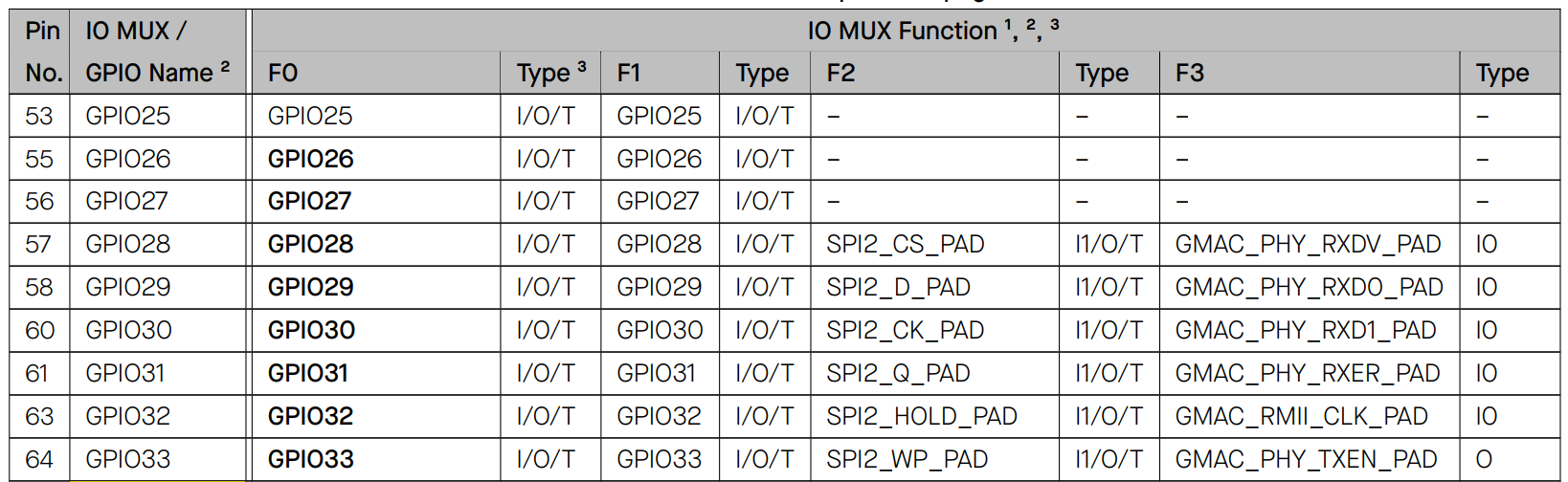

1)若輸入信號被選擇輸入到HP IO MUX,則必須首先選擇該GPIO的功能,並將其直接連接至CPU內部外設信號。下圖展示了可供選擇的GPIO功能,這些功能可以通過配置IO_MUX_GPIOn_REG寄存器來實現。

圖2.4.3.6 IO MUX的GPIO選擇功能(部分截圖)

上圖摘自《ESP32-P4數據手冊》中的2.3.1 IO MUX Functions小節內容。上圖中,若我們把GPIO28號管腳配置為Function3功能,則該GPIO通過IO MUX直接連接至SPI2_CS_PAD內部外設信號(請看圖2.4.3.1中的⑥和①)。

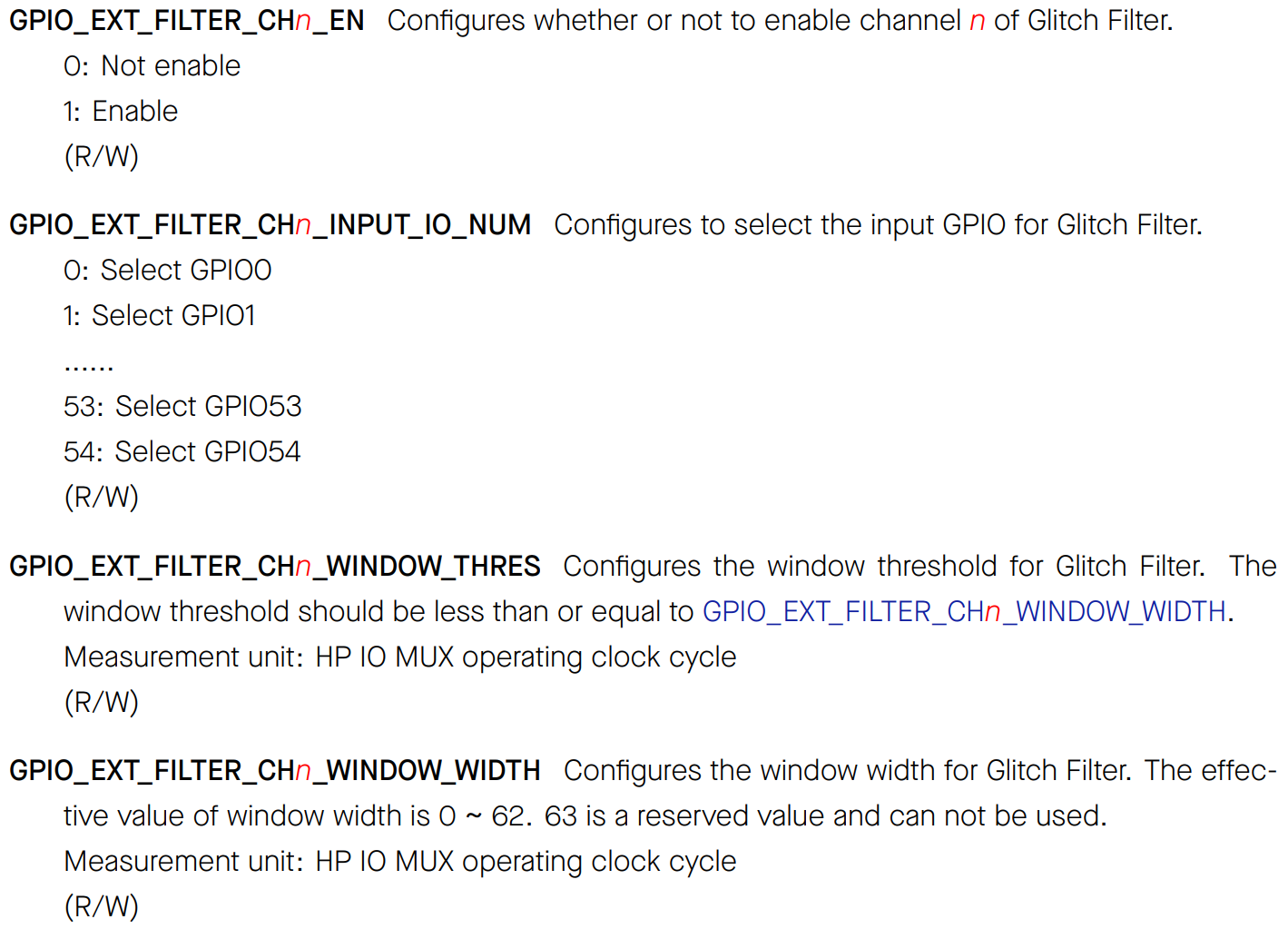

2)當輸入信號被選擇進入高性能(HP)GPIO矩陣時,該信號會依次經過信號濾波和毛刺濾波處理,然後通過GPIO_EXT_GLITCH_FILTER_CHn_REG寄存器配置特定的GPIO輸入。此寄存器用於選擇對哪個GPIO信號應用毛刺濾波,以去除可能存在的短時噪聲信號或毛刺信號,從而提升信號的穩定性和可靠性。經過濾波處理的信號還會進行時鐘同步(GPIO SYNC),確保信號與系統時鐘保持一致性,減少由於時鐘不匹配可能引入的延遲或不穩定因素。同步處理完成後,信號將進入內部信號綁定模塊,用於後續的邏輯控制或輸出。如下圖所示,通過GPIO_EXT_GLITCH_FILTER_CHn_REG(n:0~7)寄存器配置哪個GPIO輸入字段描述。

圖2.4.3.7 配置哪個GPIO輸入信號

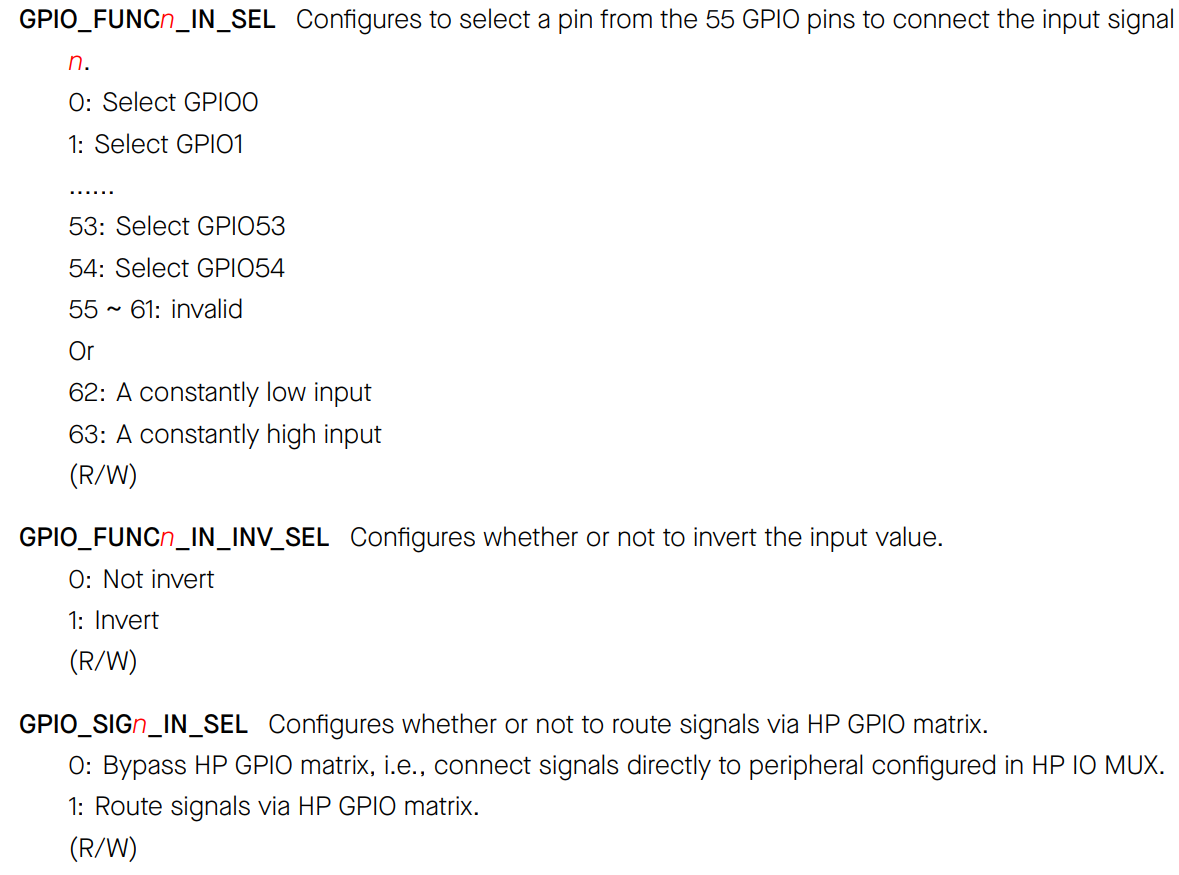

3)通過GPIO_FUNCn_IN_SEL配置輸入信號時,可參考圖2.4.3.1中的步驟②。例如,若要將UART0的RXD輸入信號(信號索引為10)連接到GPIO7,請按以下步驟配置。

設置GPIO_FUNC10_IN_SEL_CFG_REG寄存器(n表示圖2.4.3.2中的索引號,對應uart0_rxd_pad_in輸入信號)中的GPIO_SIG10_IN_SEL位,以通過HP GPIO矩陣啓用外設輸入。這樣可以通過矩陣將信號索引10(即UART0的RXD輸入)路由到一個GPIO上。然後在GPIO_FUNC10_IN_SEL_CFG_REG寄存器中,將GPIO_FUNC10_IN_SEL字段設置為7,指定GPIO7作為UART0 RXD信號的輸入源,最後配置IO_MUX_GPIO7_REG寄存器中的IO_MUX_GPIO7_FUN_IE位(具體描述見圖2.4.3.5中左則的外部信號),以啓用GPIO7的引腳輸入。此設置允許引腳從HP GPIO矩陣接收輸入信號。上述用到的寄存器的字段描述如下所示。

圖2.4.3.8 配置GPIO映射到內部輸入信號

至此,GPIO路由至內部輸入信號的流程已講解完成。對於LP系統,流程與HP系統類似,只是配置的寄存器不同。

8,內部外設信號路由至管腳

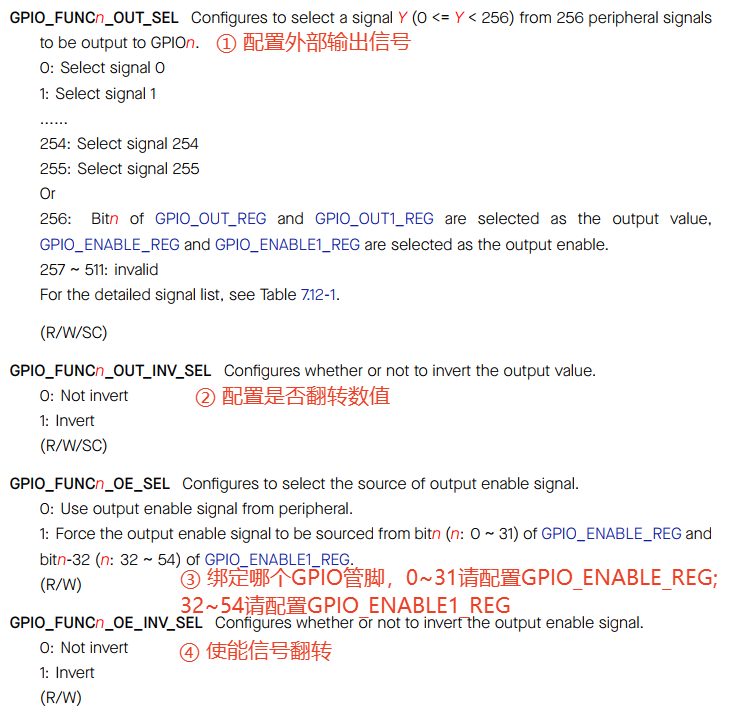

接下來,筆者將以HP系統的內部外設信號輸出為例進行説明。如圖2.4.3.1所示,HP系統中的232個外設信號可以通過HP GPIO matrix 和HP IO MUX輸出。如果選擇通過HP GPIO matrix輸出外設信號(請看圖2.4.3.1中的⑧),則必須配置對應的寄存器,即GPIO_FUNCn_OUT_SEL_CFG_REG寄存器,其中n表示圖2.4.3.2右側列出的外部信號編號,共有232個外部輸出信號。以下是GPIO_FUNCn_OUT_SEL_CFG_REG寄存器的字段描述。

圖2.4.3.9 內部外設輸出信號綁定GPIO

如果選擇直接輸出外設信號,則信號會通過HP IO MUX的直接映射功能輸出。這些映射功能我們已經在圖2.4.3.6中進行了詳細説明。要實現直接輸出的配置,只需設置對應的IO_MUX_GPIOn_REG寄存器,即可完成信號的輸出。

至此,內部輸出信號路由至GPIO的流程已講解完成。對於LP系統,流程與HP系統類似,也 是配置的寄存器不同。

2.4.4 芯片Boot控制

芯片在上電或硬件復位時,會通過某些管腳的上下拉(Strapping Pins)和eFuse bits(是一種可編程電子保險絲,是一種用於存儲信息和保護芯片的非易失性存儲器件)來確定其啓動過程和一些功能,無需微處理器的參與。這些設置可以決定以下功能:

1)芯片啓動模式:確定芯片以何種模式啓動。

2)ROM消息打印的啓動和禁用:決定是否在啓動時打印ROM中的消息。

3)JTAG信號源:決定JTAG信號的來源。

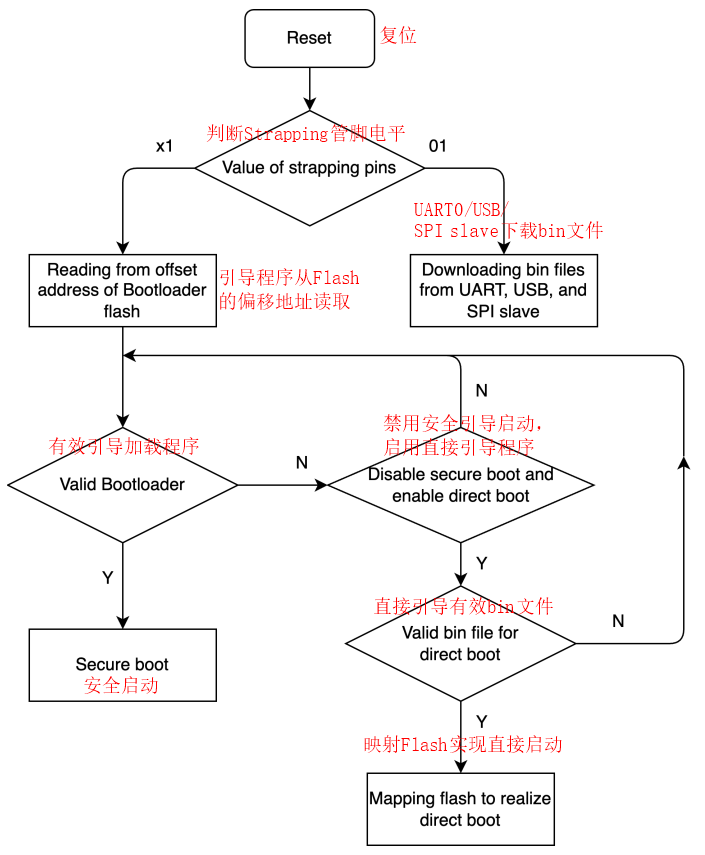

1,芯片啓動模式。

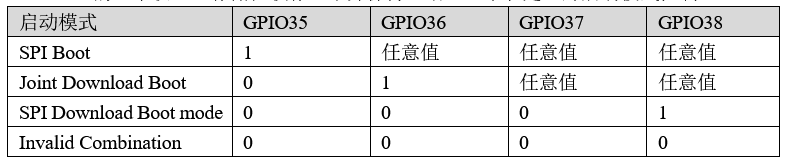

在電源上電或復位過程中,芯片會採集Strapping管腳(GPIO35、GPIO36、GPIO37、GPIO38)的電平狀態,存儲在鎖存器中並保持至斷電。下表是芯片啓動模式控制。

表2.4.4.1 芯片啓動模式控制

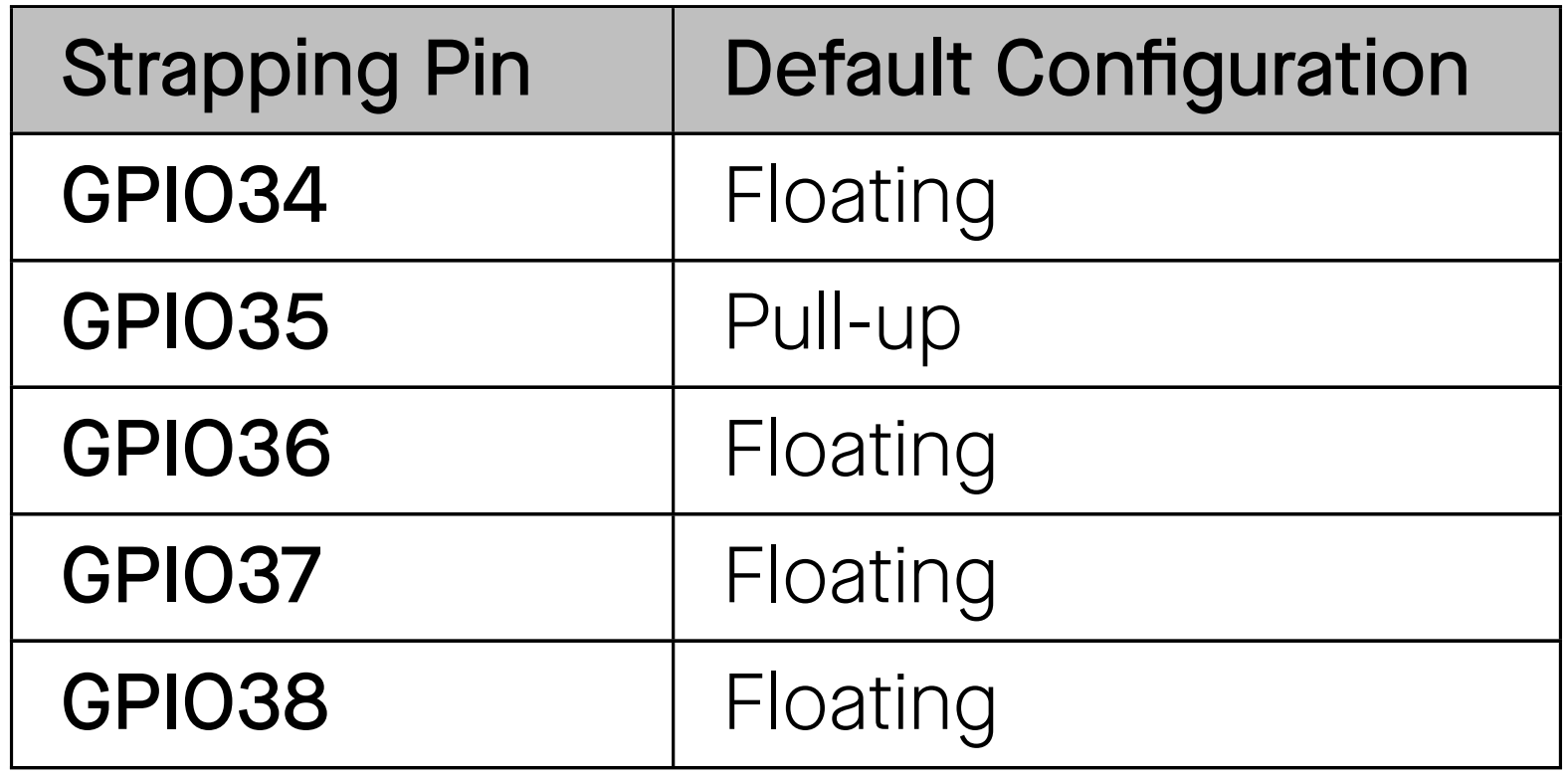

ESP32-P4芯片的啓動模式由GPIO35至GPIO38的電平決定。默認情況下,若GPIO35為高電平,則芯片進入“SPI Boot”模式;若GPIO35為低電平且GPIO36為高電平,則進入“Joint Download Boot”模式,支持“USB”、“UART”和“SPI Slave”三種下載方式;若GPIO35至GPIO37均為低電平且GPIO38為高電平,則芯片進入“SPI Download Boot”模式;若GPIO35至GPIO38均為低電平,則芯片進入“Invalid Combination”無效模式。下圖為Strapping管腳默認電平。

圖2.4.4.1 Strapping管腳默認電平

根據上圖所示,ESP32-P4芯片的GPIO35管腳在默認情況下內部連接有一個上拉電阻,這種配置使得芯片進入“SPI Boot”模式。若GPIO35管腳未連接或連接到外部高阻抗電路,那麼內部的弱上拉電阻將確定該管腳的默認輸入電平,進而決定芯片的默認啓動模式。下圖是芯片啓動流程。

圖2.4.4.2 ESP32-P4芯片啓動流程

注意:上圖中的“x1”和“01”表示GPIO35和GPIO36組合值,芯片根據這兩個管腳組合值進入不同的啓動模式。

小知識:

1)Strapping管腳是芯片每次上電或復位時,都需要一些初始配置參數,如加載芯片的啓動模式、flash存儲器的電壓等。這些參數通過strapping管腳控制。芯片讀取Strapping管腳上電時的狀態來配置芯片的初始化的參數,復位釋放後, strapping管腳和普通IO管腳功能相同。

2)在SPI Boot模式下,ROM引導加載程序通過從SPI flash中讀取程序來啓動系統。在這個模式下,我們還可以進一步分類如下:

①:Normal flash Boot:ROM引導加載程序通過從SPI Flash加載至L2MEM中啓動。

②:Direct Boot:程序從Flash運行。如果要啓動此模式,請確保下載的bin文件前兩個字為0xaedb041d。

3)在Joint Download Boot模式下,用户可通過USB或UART0接口將二進制文件下載至flash,或者下載至L2MEM中直接運行。

4)在SPI Download Boot模式下,用户可通過SPI接口將二進制文件下載至Flash,或者下載至L2MEM中直接運行。

2,ROM消息打印的啓動和禁用

系統啓動過程中,ROM代碼log可打印至如下控制器。

1)UART0和USB Serial/JTAG控制器(默認)

2)USB Serial/JTAG控制器

3)UART0

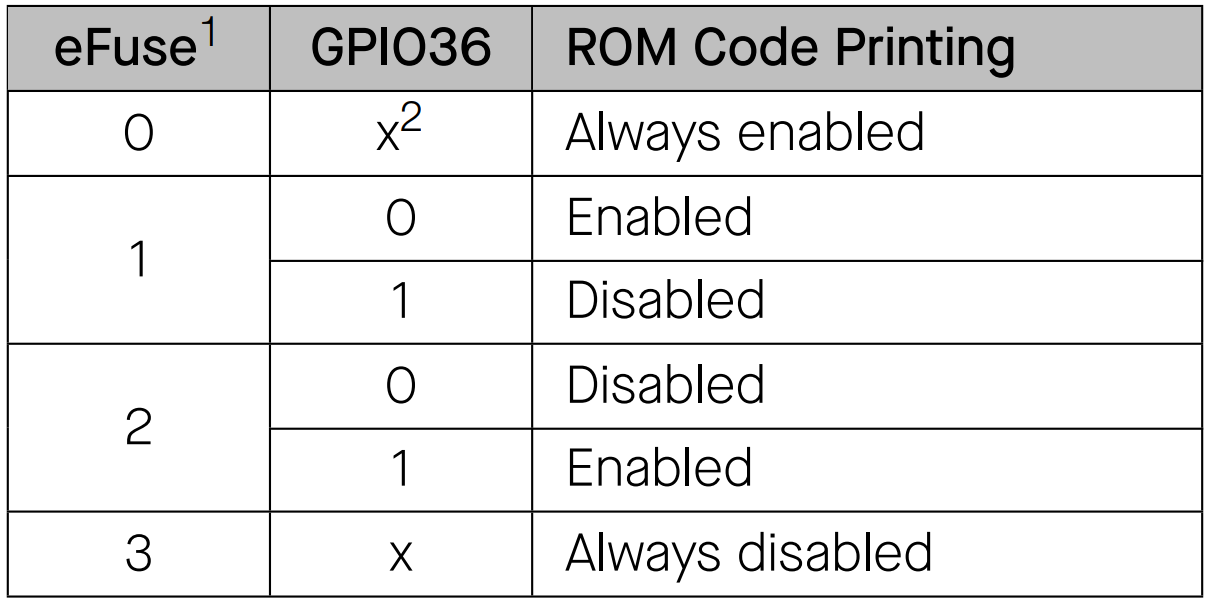

EFUSE_UART_PRINT_CONTROL(eFuse 位)和GPIO36控制ROM消息打印到UART0,如下圖所示。

圖2.4.4.3 UART0 ROM 日誌打印控制

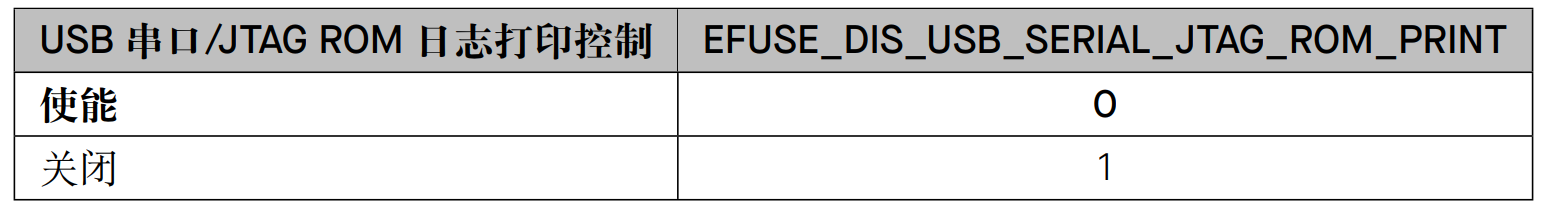

EFUSE_DIS_USB_SERIAL_JTAG_ROM_PRINT(eFuse 位)用於控制 ROM 日誌是否打印到 USB Serial/JTAG 控制器。當該位為 1 時,禁止將日誌打印到 UART Serial/JTAG 控制器。當該位為 0 時,如果通過 EFUSE_DIS_USB_SERIAL_JTAG 啓用 USB Serial/JTAG 控制器,則 ROM 消息將打印到 USB 串口/JTAG 控制器。具體情況如下圖所示。

圖2.4.4.4 USB 串口/JTAG ROM 日誌打印控制

默認情況下,EFUSE_UART_PRINT_CONTROL(eFuse 位)和 EFUSE_DIS_USB_SERIAL_JTAG_ROM_PRINT(eFuse 位)均配置為 0,表示啓用 UART0 和 USB Serial/JTAG ROM 日誌打印功能。請注意,如果 EFUSE_DIS_USB_SERIAL_JTAG_ROM_PRINT 設置為 0 以打印到 USB,但 USB Serial/JTAG 控制器已禁用,則 ROM 消息將不會打印到 USB Serial/JTAG 控制器。

有關 eFuse 控制器的詳細信息,請參閲《ESP32-P4 Technical Reference Manual》中的第 292 頁“eFuse Controller”章節,該章節提供了關於 eFuse 控制器的技術規格和功能説明。

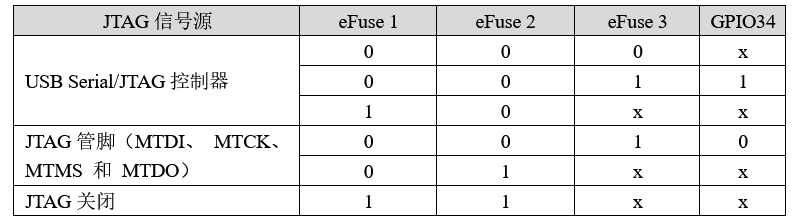

3,JTAG信號源

在系統啓動的早期,GPIO34可用於控制JTAG信號源。該引腳沒有內部上下拉電阻,因此strapping的值必須由不處於高阻抗狀態的外部電路控制。如下表所示,GPIO34與EFUSE_DIS_PAD_JTAG、EFUSE_DIS_USB_JTAG和EFUSE_JTAG_SEL_ENABLE共同控制JTAG信號源。

圖2.4.4.2 JTAG信號源控制

上圖中的 eFuse 1、eFuse 2 和 eFuse 3 分別代表 eFuse 位的 EFUSE_DIS_PAD_JTAG、EFUSE_DIS_USB_JTAG 和 EFUSE_JTAG_SEL_ENABLE。這裏的 x 代表任意值,可以忽略。

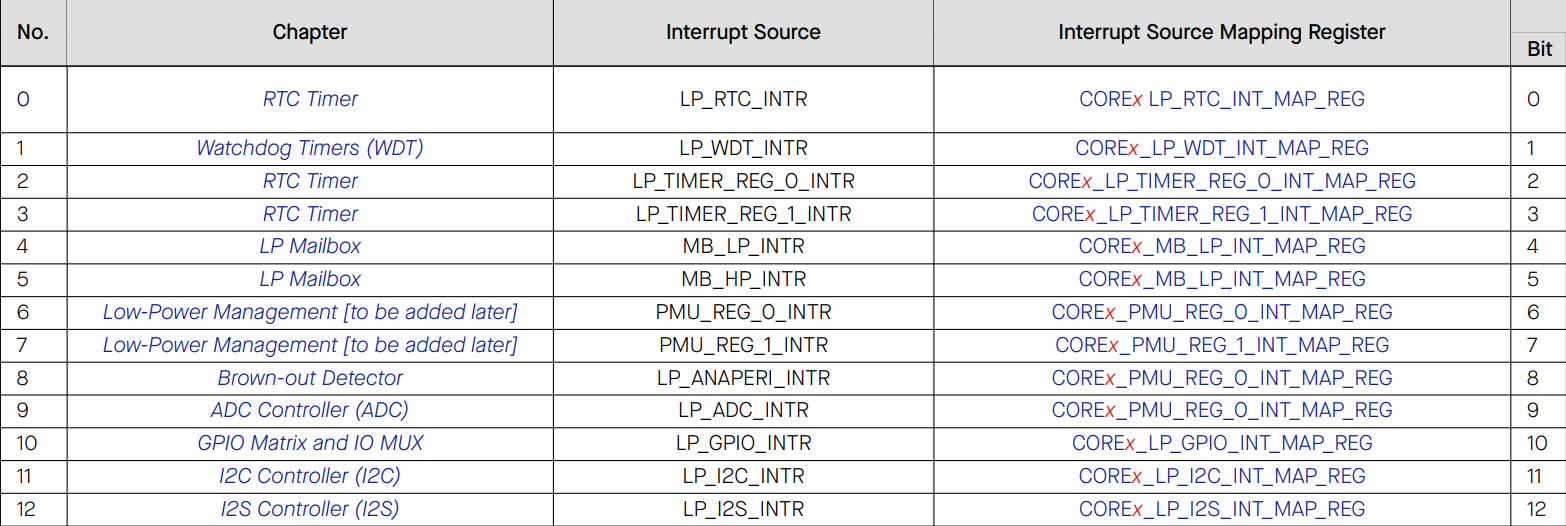

2.4.5 中斷矩陣

ESP32-P4 擁有多達 126個外設中斷源,需要通過中斷矩陣將這些中斷信號映射到 32個HP CPU0中斷 或 32個HP CPU1中斷。若沒有中斷矩陣,這樣大規模的中斷源管理將極具複雜性。而通過中斷矩陣,不僅能有效地將中斷源分配到不同的CPU核,還可以根據應用需求將同一中斷源路由至多個CPU中斷輸入,從而實現靈活的中斷處理和多任務並行操作。通過這種結構設計,ESP32-P4的中斷矩陣確保了複雜的外設中斷管理變得高效、靈活且可擴展,為開發者提供了更多的系統配置選項,優化了系統性能和響應能力。

關於ESP32-P4的這126個外設中斷源的詳細信息,可以參考 《ESP32-P4技術參考手冊》中的593頁,其中的表10.4-1 描述了 CPU外設中斷源映射/狀態寄存器和外設中斷源,為開發者提供了詳細的中斷源配置和映射方式。

1,中斷矩陣概述

中斷矩陣是一種靈活的硬件機制,用於管理和分配系統中斷信號,使得多個外設的中斷請求能夠靈活地映射到不同的CPU中斷輸入上。在ESP32-P4芯片中,中斷矩陣允許通過軟件配置,將不同外設或GPIO引腳的中斷源動態連接到特定的CPU中斷控制器(Interrupt Controller)。

中斷矩陣的主要功能在於其高度靈活性和可配置性,具體包括:

1)動態路由中斷源:中斷矩陣可以將不同的外設或GPIO中斷信號連接到任意CPU核心的中斷通道上,支持跨核中斷分配。

2)優先級管理:矩陣允許對不同的中斷源設置優先級,以確保高優先級中斷能夠搶佔低優先級中斷,提高系統的實時性。

3)中斷源隔離:它支持通過矩陣的配置隔離不同的中斷源,避免多箇中斷源競爭同一中斷通道,從而提升系統的穩定性和魯棒性。

4)可查詢當前外設中斷源的中斷狀態。

5)多箇中斷源可映射到單個HP CPU0或HP CPU1中斷,我們稱之為共享中斷。

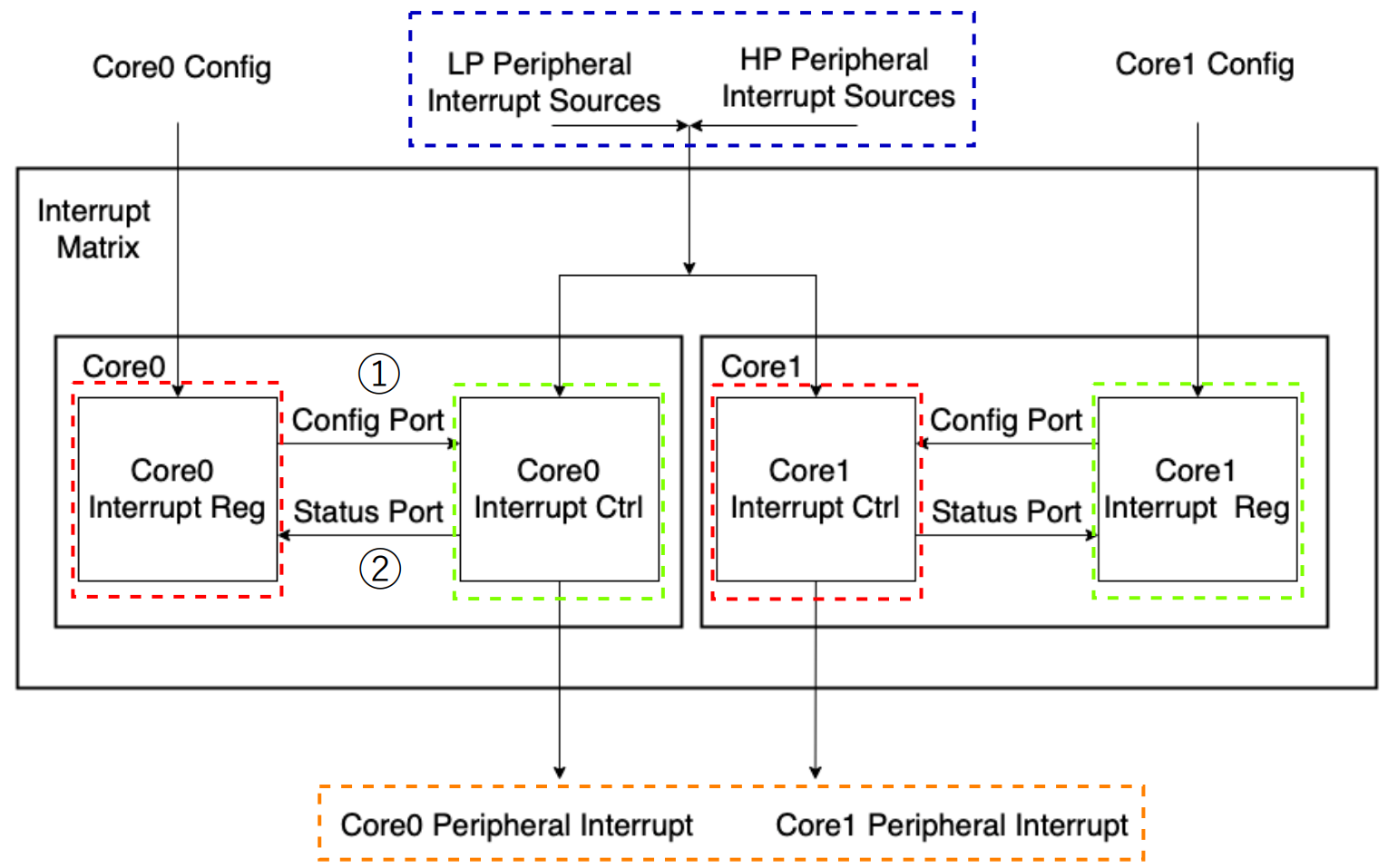

下圖為ESP32-P4芯片中斷矩陣結構。

圖2.4.5.1 中斷矩陣結構

上圖中的藍色框表示中斷矩陣,它負責接收來自外設的中斷信號,包括低功耗外設(LP Peripheral Interrupt Sources)和高性能外設(HP Peripheral Interrupt Sources)。當中斷矩陣接收到這些外設中斷信號後,用户可以通過配置紅色框標識的 Core0 Interrupt Reg 或 Core1 Interrupt Reg 寄存器,來選擇將外設中斷源路由到 HP CPU0 或 HP CPU1。

紅色框中的 Core0 Interrupt Reg 和Core1 Interrupt Reg寄存器具有兩個主要功能:

1)上圖中的①,通過配置端口(Config Port) 動態地將中斷信號路由到特定核心的中斷控制器,允許用户靈活配置中斷路由。

2)上圖中的②,通過狀態端口(Status Port) 查詢當前外設中斷源的狀態,幫助用户監控和調試中斷的處理情況。

上圖中的綠色框標識表示 Core0 Interrupt Ctrl 和Core1 Interrupt Ctrl中斷控制器,它負責處理路由到該核心的中斷信號。這些控制器可以根據中斷優先級、信號來源等條件,決定是否處理中斷。最終,當CPU接收到外部中斷信號時,會調用與該中斷相關聯的中斷服務程序(上圖的橙色框標識),處理完畢後,恢復正常操作。

2,中斷矩陣的操作流程

1)中斷信號生成:當某個外設或GPIO產生中斷事件時,信號傳遞至中斷矩陣。

2)信號路由:中斷矩陣根據預設的路由配置,將中斷信號映射至目標CPU的中斷輸入端。

3)CPU中斷處理:CPU接收到中斷信號後,根據中斷優先級判定是否處理該中斷。當中斷處理完成後,CPU通過清除相應標誌位或通過軟件控制的中斷服務恢復正常執行流程。

下圖為中斷處理流程圖。

圖2.4.5.1 中斷處理流程

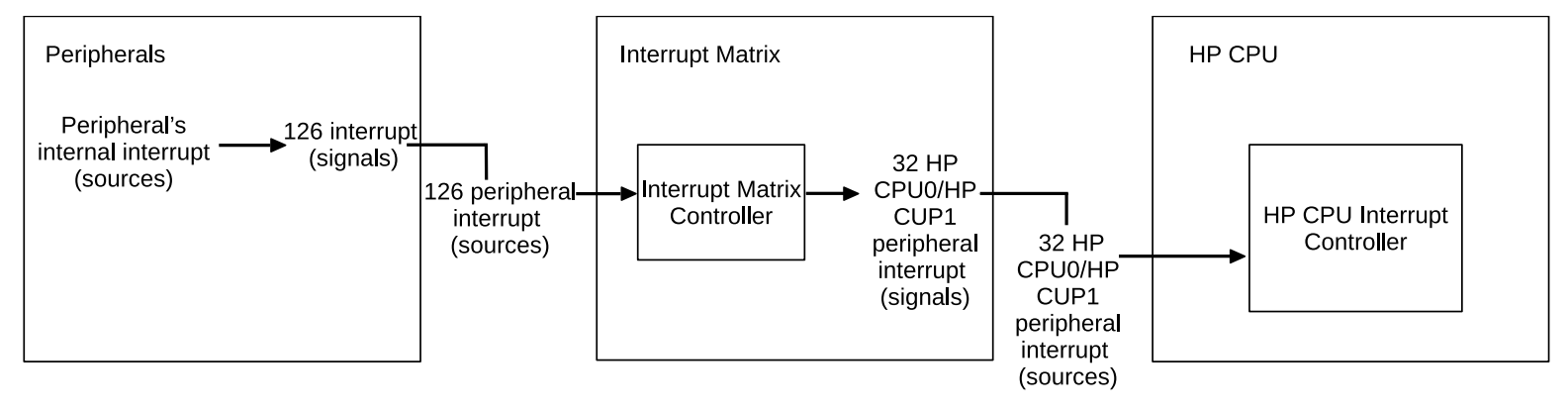

在 ESP32-P4 中,外設模塊可以生成多達126個內部中斷源,這些中斷源對應於不同的外設事件或狀態變化,如計時器溢出、串口數據接收完成、GPIO信號變化等。這些中斷源首先通過硬件生成 126條中斷信號(Interrupt Signals)。

接下來,這些外設中斷信號被髮送到中斷矩陣(Interrupt Matrix),一個用於靈活管理和分配中斷信號的硬件結構。中斷矩陣將外設的中斷信號轉化為 中斷源(Interrupt Sources),並根據系統配置將其路由到適當的CPU核上的中斷控制器。

上圖中的中斷控制器的任務是根據系統設計和開發者的配置,將這 126個外設中斷源路由到 32條CPU中斷通道,這些通道分別與ESP32-P4的不同CPU核(CPU0和CPU1)相對應。當中斷矩陣將中斷源映射到相應的CPU中斷信號時,信號最終會進入 HP CPU中斷控制器。該控制器負責進一步管理和處理來自中斷矩陣的信號,並根據中斷的優先級做出處理決策。當中斷控制器決定處理某個中斷時,CPU會暫停當前任務,執行與中斷相關的中斷服務例程(ISR)。中斷處理完成後,系統將恢復正常任務執行,並清除中斷標誌,確保系統順利運行。

下圖為中斷矩陣管理的CPU外設中斷源映射和狀態寄存器。

圖2.4.5.2 CPU外設中斷源映射和狀態寄存器(部分截圖)

讀者可在《ESP32-P4技術參考手冊》中的“Interrupt Matrix”章節中,參考表10.4.1,找到關於CPU外設中斷源映射和狀態寄存器的詳細內容。該表格列出了所有可用的中斷源及其映射關係,有助於理解中斷系統的工作機制和配置方法。

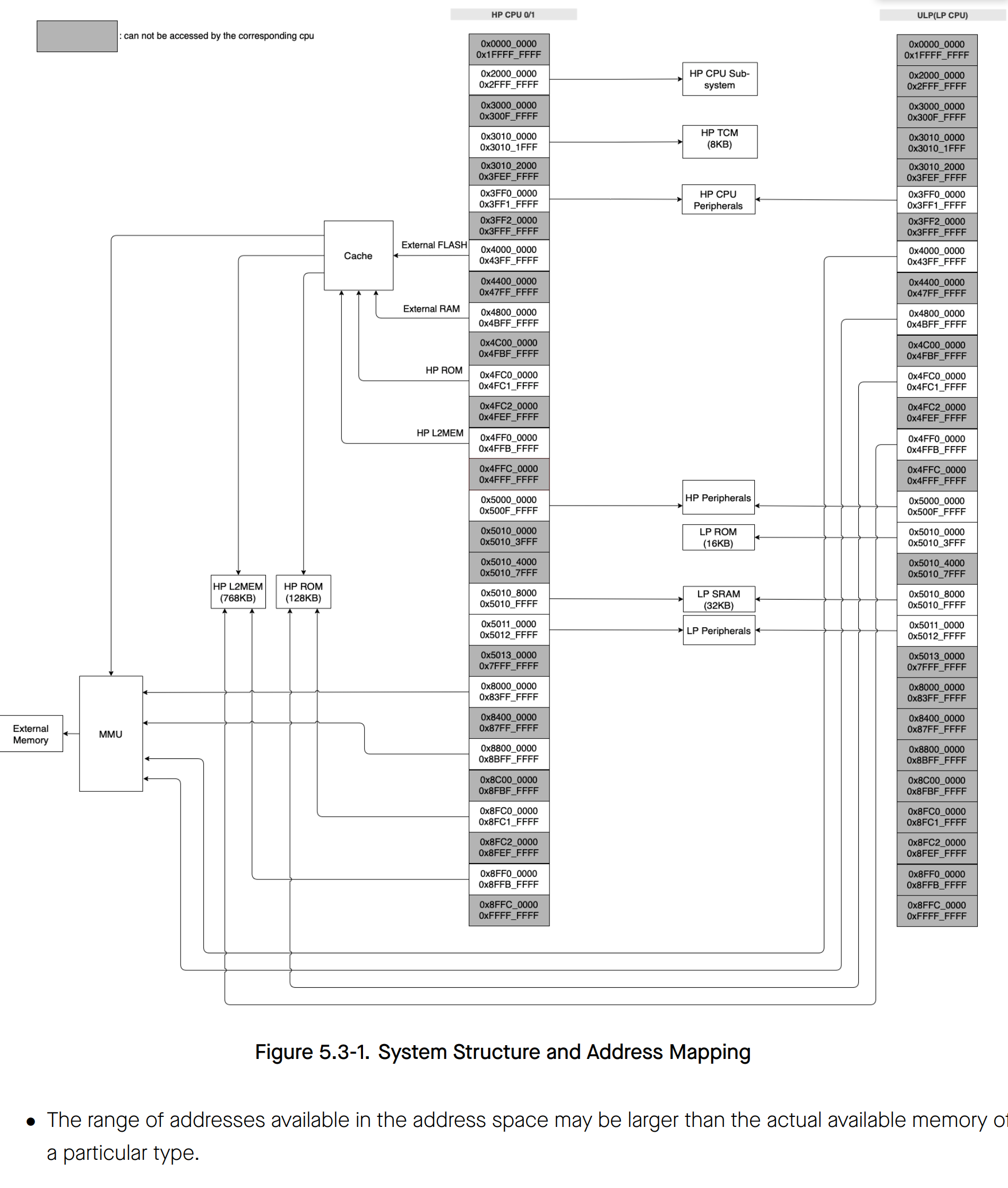

2.5 ESP32-P4 啓動流程

本文將會介紹ESP32-P4從上電到運行app_main函數中間所經歷的步驟(即啓動流程)。從宏觀上,該啓動流程可分為如下三個步驟。

1)一級引導程序,它被固化在ESP32-P4內部的ROM中,它會從flash的0x2000處地址加載二級引導程序至RAM(IRAM & DRAM)中。

2)二級引導程序從flash中加載分區表和主程序鏡像至內存中,主程序中包含了RAM段和通過flash高速緩存映射的只讀段。

3)應用程序啓動階段運行,這時第二個CPU和freeRTOS的調度器啓動,接着運行main_task任務函數,從而進入app_main函數執行用户代碼。

下面作者根據IDF庫相關的代碼來講解這三個引導流程,如下:

1,一級引導程序

該部分程序是直接存儲在ESP32-P4內部ROM中,所以普通開發者無法直接查看,它主要是做一些前期的準備工作(復位向量代碼),然後從flash 0x2000偏移地址中讀取二級引導程序文件頭中的配置信息,並使用這些信息來加載剩餘的二級引導程序。

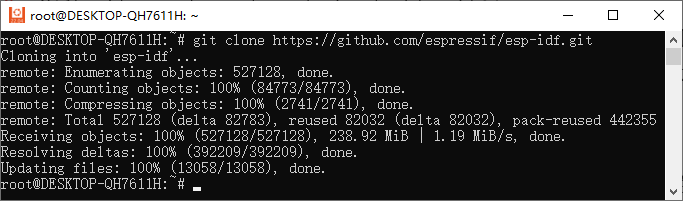

2,二級引導程序

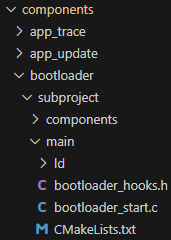

該程序是可以查看且可被修改,在搭建ESP-IDF環境完成後,可在esp-idf\components\bootloader/subproject/main/路徑下找到bootloader_start.c文件,此文件就是二級引導程序啓動處。首先我們克隆ESP-IDF庫,克隆過程如下所示。

圖2.6.1 克隆ESP-IDF庫

克隆完成後,使用VSCode打開ESP-IDF庫,接着找到bootloader_start.c,如下圖所示。

圖2.6.2 bootloader_start.c文件路徑

在這個文件下,找到call_start_cpu0函數,此函數是bootloader程序,如下是bootloader程序的部分代碼。

/*

ROM引導加載程序完成從閃存加載第二階段引導加載程序之後到達這裏

*/

void __attribute__((noreturn)) call_start_cpu0(void)

{

if (bootloader_before_init) {

bootloader_before_init();

}

/* 1. 硬件初始化:初始化內存、啓用超級看門狗自動餵養、配置時鐘、清除bss段、開啓cache和

復位mmu等操作。

bootloader_support/src/ esp32-p4/bootloader_esp32p4.c */

if (bootloader_init() != ESP_OK) {

bootloader_reset();

}

if (bootloader_after_init) {

bootloader_after_init();

}

/* 2. 選擇啓動分區的數量:加載分區表,選擇boot分區 */

bootloader_state_t bs = {0};

int boot_index = select_partition_number(&bs);

if (boot_index == INVALID_INDEX){

bootloader_reset();

}

/* 3. 加載應用程序映像並啓動

bootloader_support/src/esp32-p4/bootloader_utility.c */

bootloader_utility_load_boot_image(&bs, boot_index);

}

ESP-IDF使用二級引導程序可以增加FLASH分區的靈活性(使用分區表),並且方便實現FLASH加密,安全引導和空中升級(OTA)等功能。主要的作用是從flash的0x8000處加載分區表(請看在線ESP-IDF編程指南分區表章節)。根據分區表運行應用程序。

3,三級引導程序

應用程序的入口是在esp-idf/components/esp_system/port/路徑下的cpu_star.c文件,在此文件下找到call_start_cpu0函數(端口層初始化函數)。這個函數由二級引導加載程序執行,並且從不返回。因此你看不到是哪個函數調用了它,它是從彙編的最底層直接調用的(components\esp_system\ld\esp32p4\sections.ld.in彙編文件)。

這個函數會初始化基本的C運行環境(“CRT”),並對SOC的內部硬件進行了初始配置。執行call_start_cpu0函數完成之後,在components\esp_system\startup.c文件下調用start_cpu0(在36行中,弱關聯start_cpu0_default函數)系統層初始化函數,如下start_cpu0_default函數的部分代碼。

static void start_cpu0_default(void)

{

/* 初始化核心組件和服務 */

do_core_init();

/* 執行構造函數 */

do_global_ctors();

/* 執行其他組件的init函數 */

do_secondary_init();

#if SOC_CPU_CORES_NUM > 1 && !CONFIG_ESP_SYSTEM_SINGLE_CORE_MODE

s_system_full_inited = true;

#endif

/* 開啓APP程序 */

esp_startup_start_app();

while (1);

}

到了這裏,就完成了二級程序引導,並調用esp_startup_start_app函數進入三級引導程序,該函數的源碼如下:

/* components/freertos/app_startup.c */

/* 開啓APP程序 */

void esp_startup_start_app(void)

{

/* 省略部分代碼 */

/* 新建main任務函數 */

BaseType_t res = xTaskCreatePinnedToCore(main_task, "main",

ESP_TASK_MAIN_STACK, NULL,

ESP_TASK_MAIN_PRIO, NULL,

ESP_TASK_MAIN_CORE);

assert(res == pdTRUE);

(void)res;

void __attribute__((weak)) port_start_app_hook(void);

if (port_start_app_hook != NULL) {

port_start_app_hook();

}

ESP_EARLY_LOGD(APP_START_TAG, "Starting scheduler on CPU0");

/* 開啓FreeRTOS任務調度 */

vTaskStartScheduler();

}

/* main任務函數 */

static void main_task(void* args)

{ /* 省略部分代碼 */

/* 執行app_main函數 */

ESP_LOGI(MAIN_TAG, "Calling app_main()");

extern void app_main(void);

app_main();

ESP_LOGI(MAIN_TAG, "Returned from app_main()");

vTaskDelete(NULL);

}

從上述源碼可知,首先在xTaskCreatePinnedToCore函數創建main_task任務,然後開啓freeRTOS任務調度器,最後在main_task任務下調用app_main函數(此函數在創建工程時,在main.c下定義的)。