3-1 GPIO輸出

GPIO(General Purpose Input Output)通用輸入輸出口

可配置為8種輸入輸出模式

引腳電平:0V~3.3V,部分引腳可容忍5V(FT)

輸出模式下可控制端口輸出高低電平,用以驅動LED、控制蜂鳴器、模擬通信協議輸出時序等

輸入模式下可讀取端口的高低電平或電壓,用於讀取按鍵輸入、外接模塊電平信號輸入、ADC電壓採集、模擬通信協議接收數據等

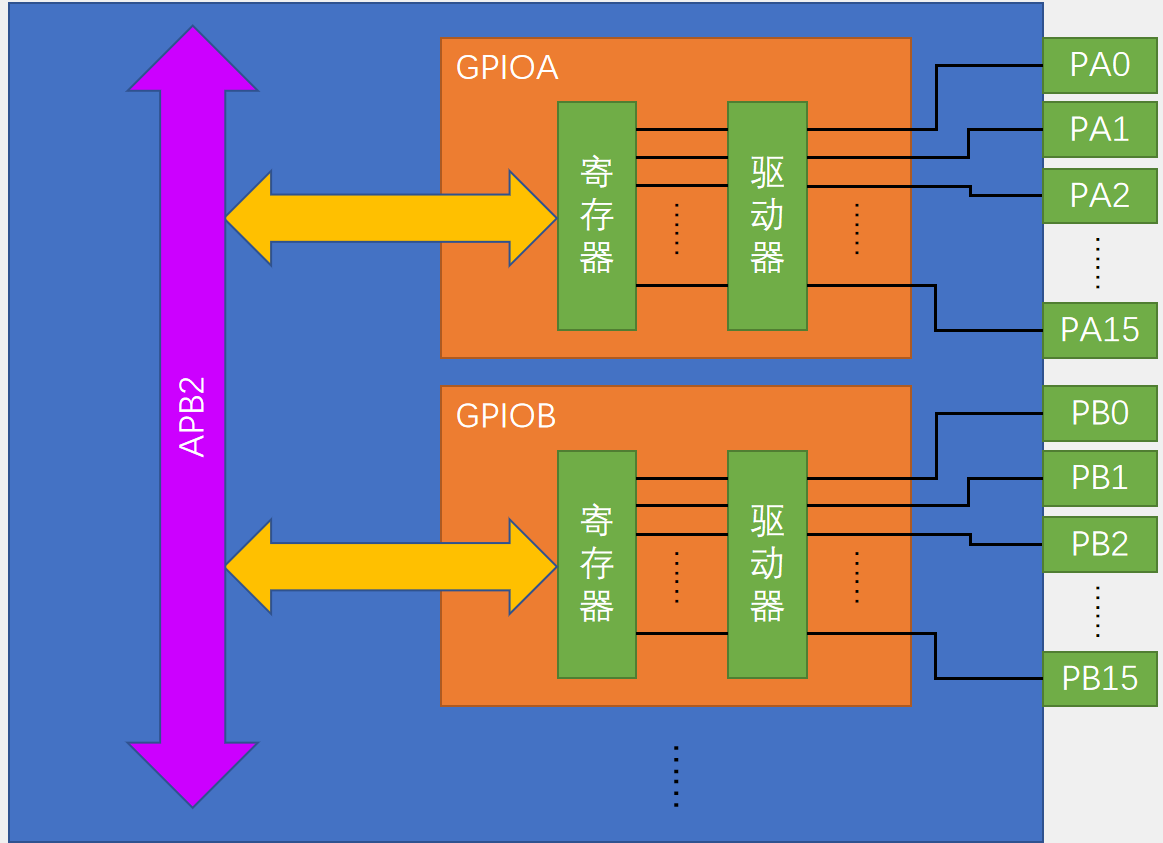

GPIO基本結構

GPIOA 的第一個接口命名為PA0,每個GPIO接口都有16個接口;STM32寄存器為32位,但是隻有16的端口,所以寄存器只有低16位有接口;所有GPIO接口都在APB2總線下。

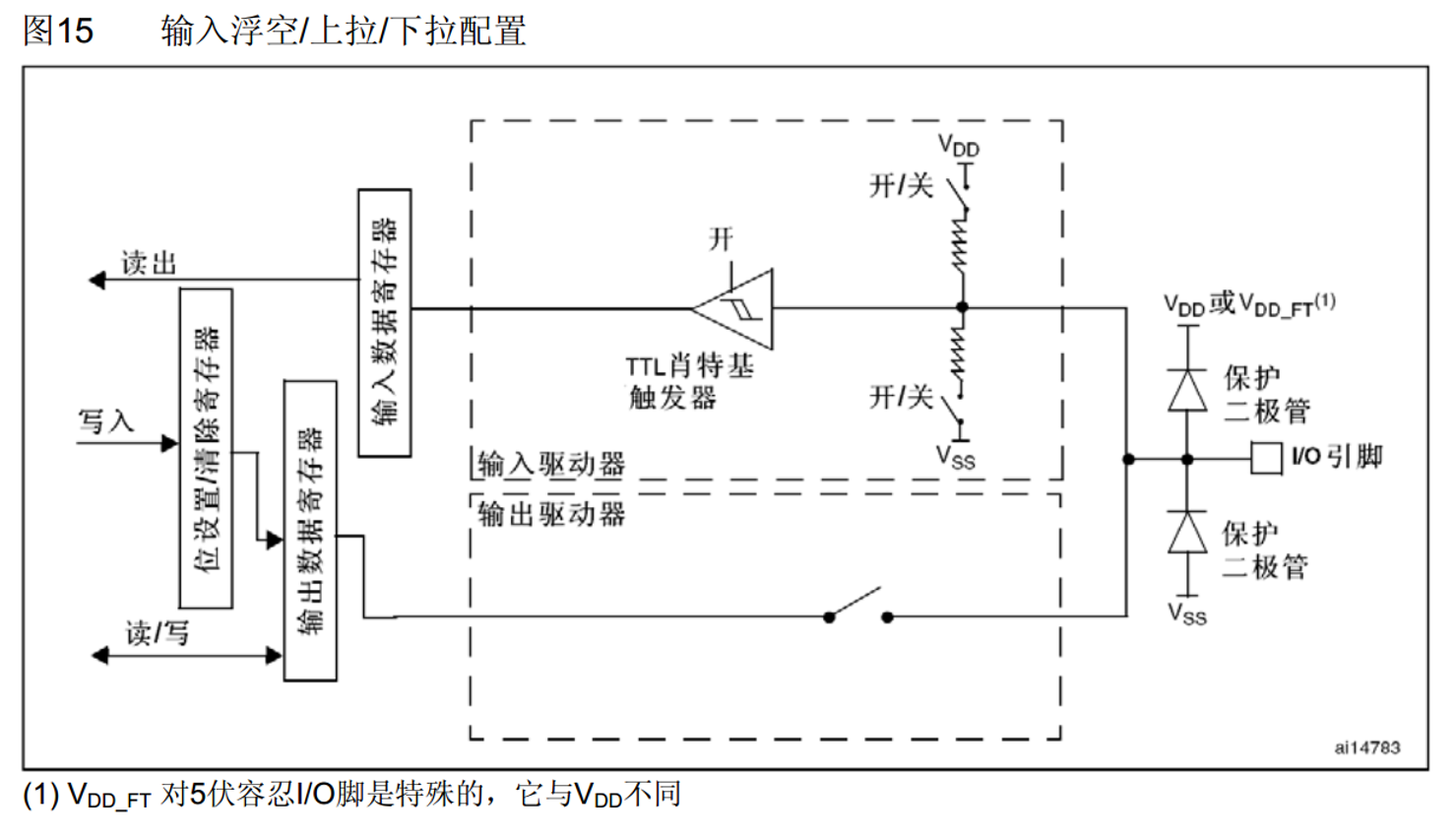

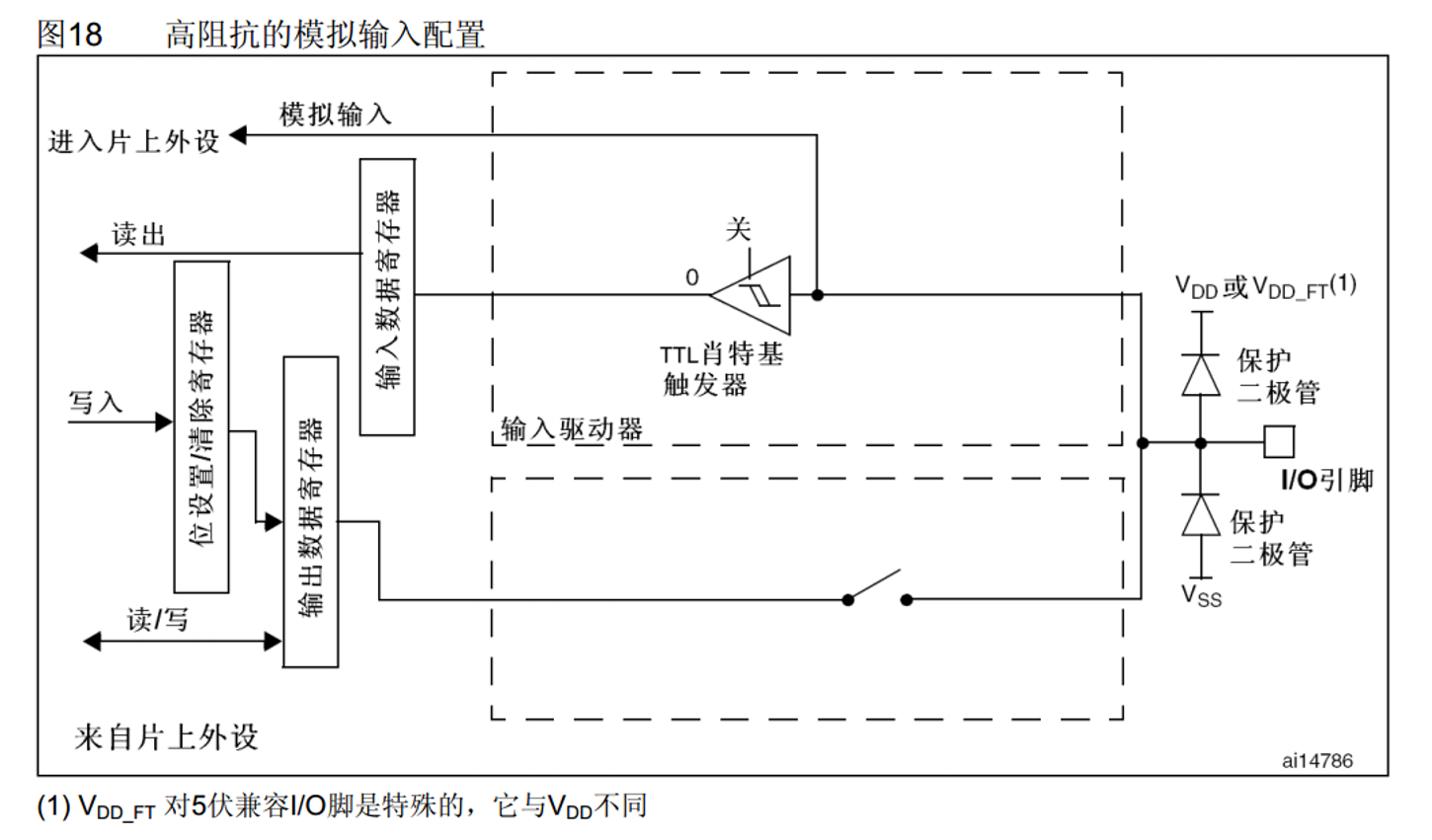

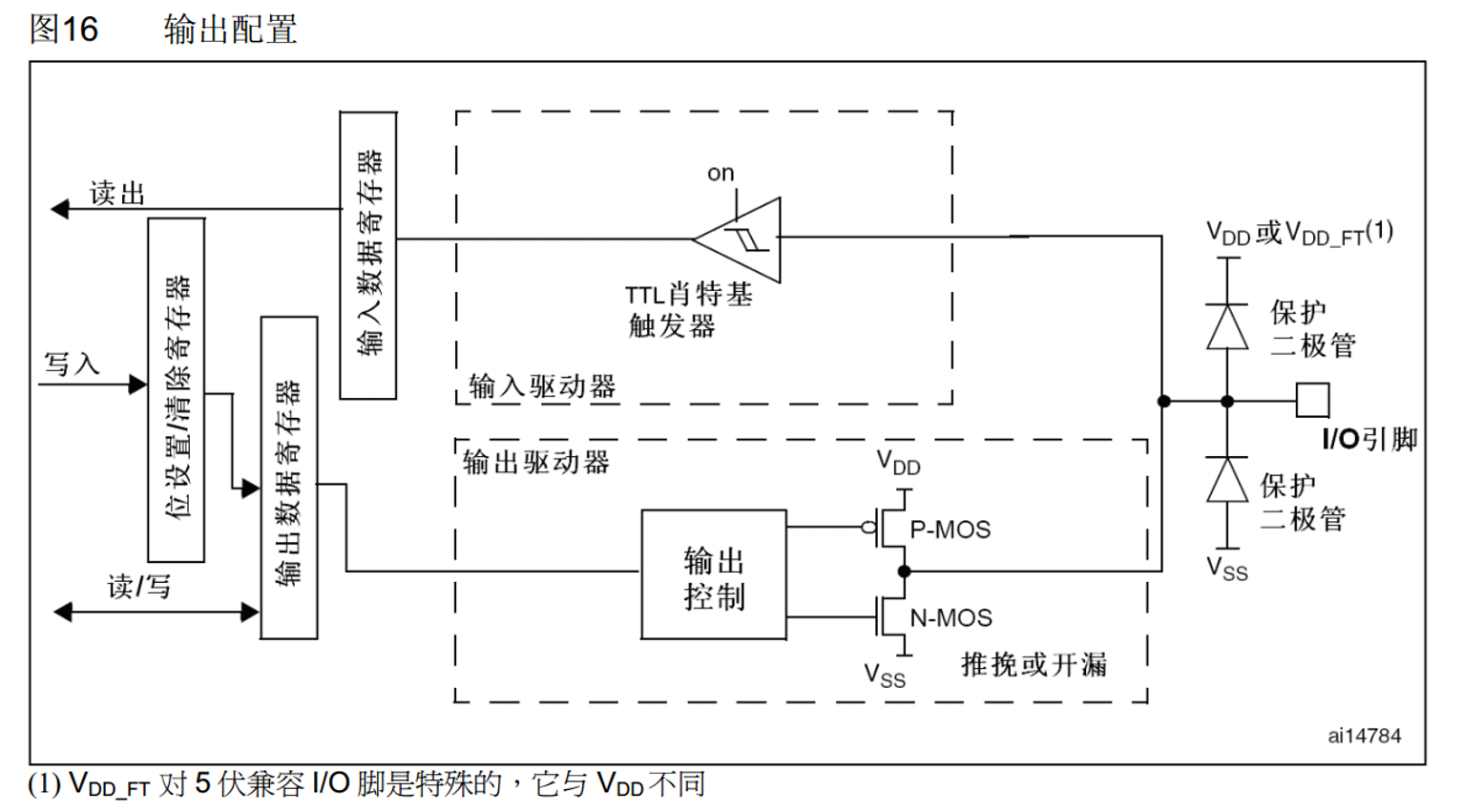

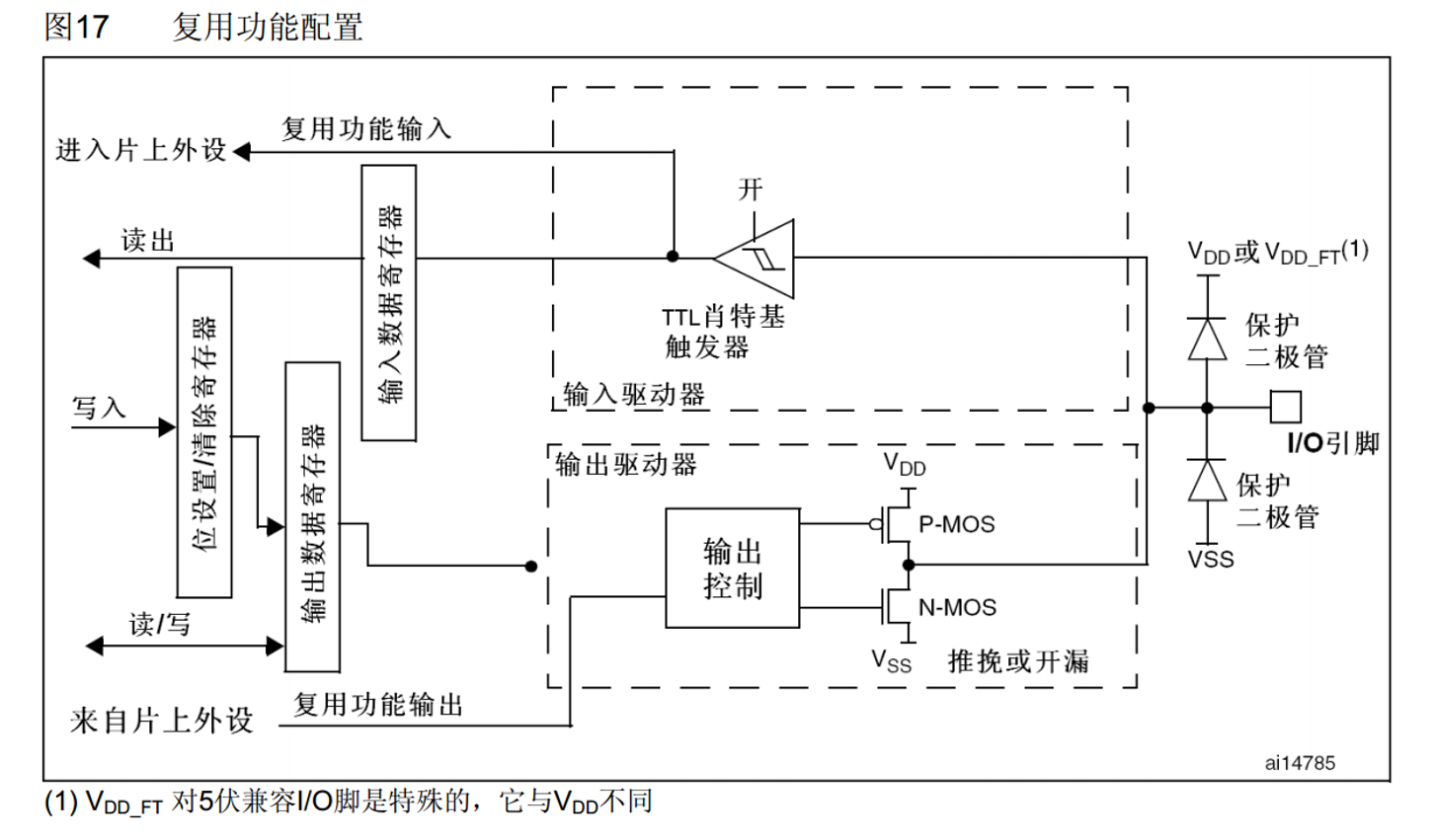

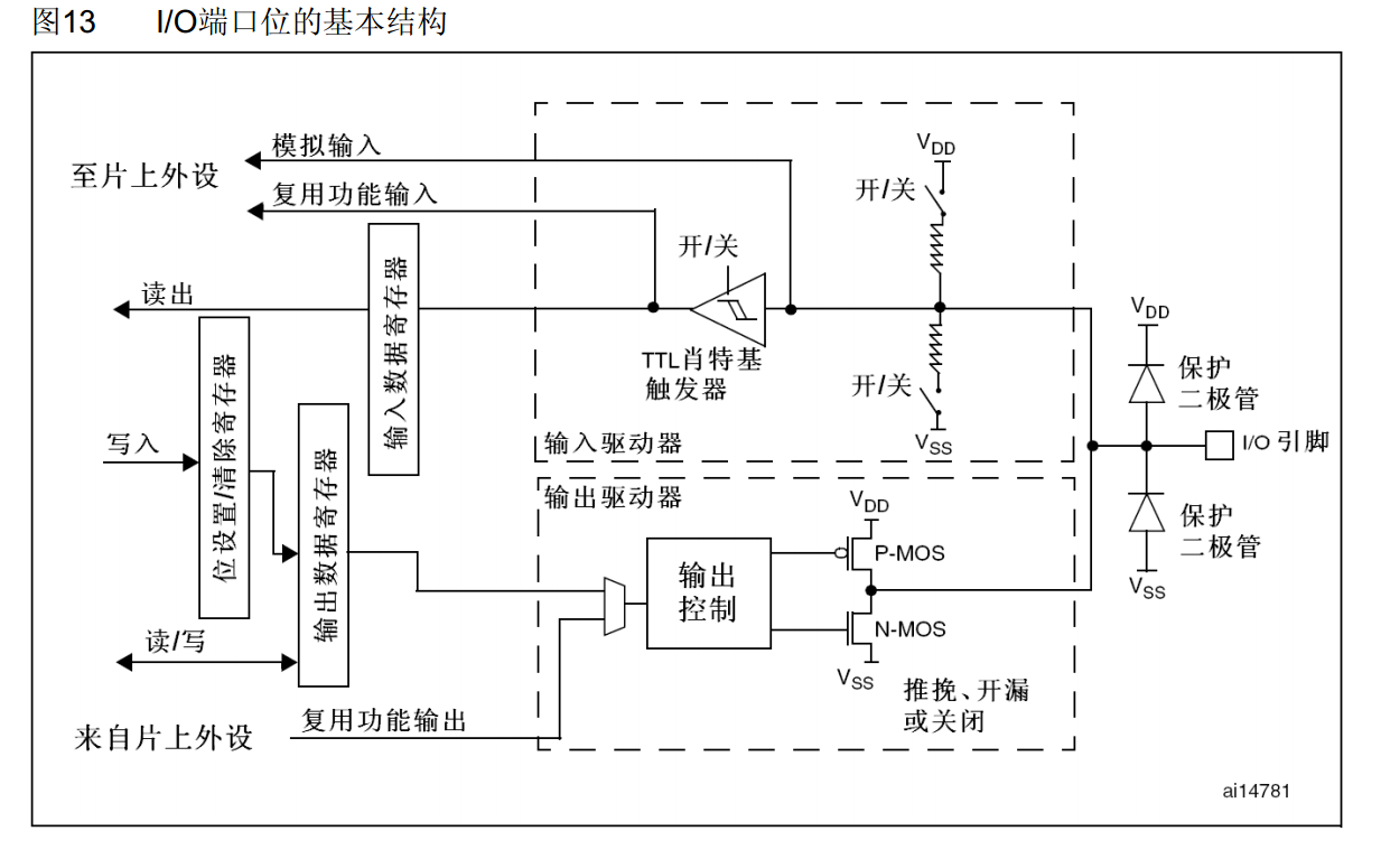

GPIO位結構

施密特觸發器:對信號設置上下閾值,防止信號不穩定產生抖動現象。

位設置/清除寄存器:可以單獨設置某一位,而不影響其它位。

輸出控制後的三極管:

在推輓輸出模式下:P-MOS和N-MOS均有效;數據寄存器為1時,上管導通,下管斷開,輸出直接接到VDD上,就是輸出高電平;數據寄存器為0時,上管斷開,下管導通,輸出直接接到VSS上,就是輸出低電平;

在開漏輸出模式下,P-MOS無效,只有N-MOS有效。數據寄存器為1時,下管斷開,輸出相當於斷開;數據寄存器為0時,下管導通,輸出直接接到VSS上,輸出低電平;(在這種模式下,只有低電平有驅動能力,可以作為通信協議的輸出模式,還可以作為輸出5V的電平信號,用來兼容5V的電平設備)

在關閉模式下,兩個MOS管都關閉,輸出的引腳設置為輸入模式,

GPIO模式

輸入模式

| 模式名稱 | 性質 | 特徵 |

|---|---|---|

| 浮空輸入 | 數字輸入 | 可讀取引腳電平,若引腳懸空,則電平不確定 |

| 上拉輸入 | 數字輸入 | 可讀取引腳電平,內部連接上拉電阻,懸空時默認高電平 |

| 下拉輸入 | 數字輸入 | 可讀取引腳電平,內部連接下拉電阻,懸空時默認低電平 |

| 模擬輸入(ADC) | 模擬輸入 | GPIO無效,引腳直接接入內部ADC |

| 開漏輸出 | 數字輸出 | 可輸出引腳電平,高電平為高阻態,低電平接VSS |

| 推輓輸出 | 數字輸出 | 可輸出引腳電平,高電平接VDD,低電平接VSS |

| 複用開漏輸出 | 數字輸出 | 由片上外設控制,高電平為高阻態,低電平接VSS |

| 複用推輓輸出 | 數字輸出 | 由片上外設控制,高電平接VDD,低電平接VSS |

在輸出模式中允許輸入,但是在輸入模式中不允許輸出。(一個端口只能有一個輸出,但是可以存在多個輸入)