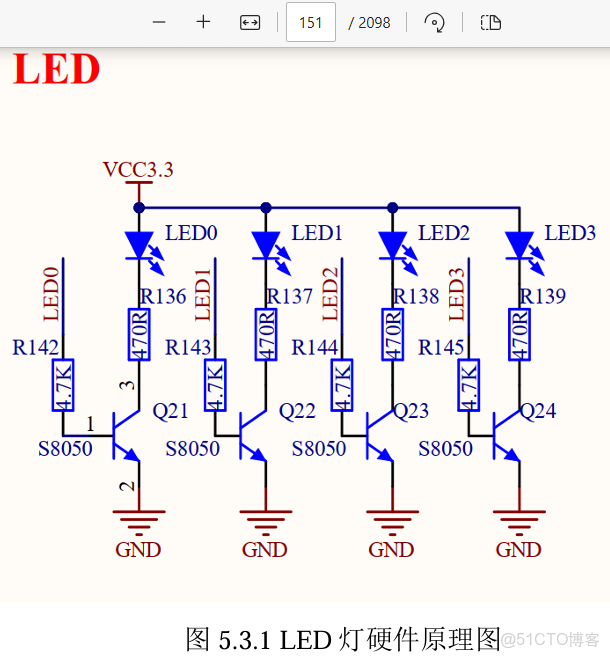

0、LED燈的電路原理:

----這就是一個三級管柵極控制開關的原理。暗紅色LED0是FPGA板上的GPIO管腳(輸出管腳),藍色LED0是發光二極管。柵極高電平,三極管導通,LED0亮。柵極低電平,三極管斷開,LED0滅。

----同理還有LED1~3,連帶LED0一共有3個GPIO管腳,一共有4個LED燈。

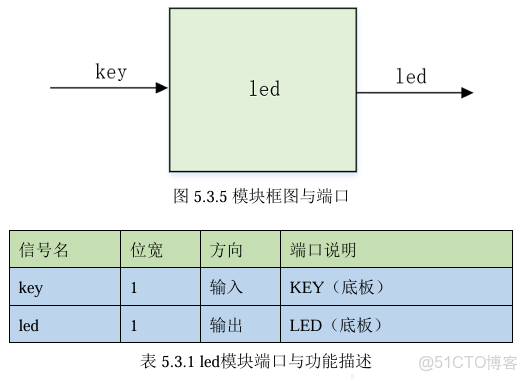

1、硬件原理圖到模塊框圖與端口的抽象。

gpio和led。就是----這個框圖與端口的抽象,有它的必要性!比如命名key和led,而不

----明確key是INPUT端口,led是OUTPUT端口。各自的位寬是什麼。等等。

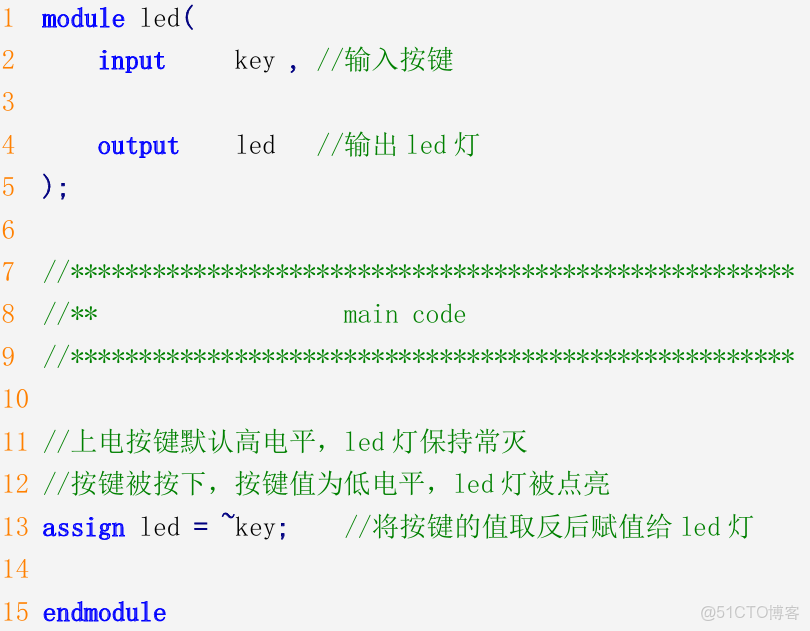

2、RTL代碼。

----代碼太過簡便,不解釋。

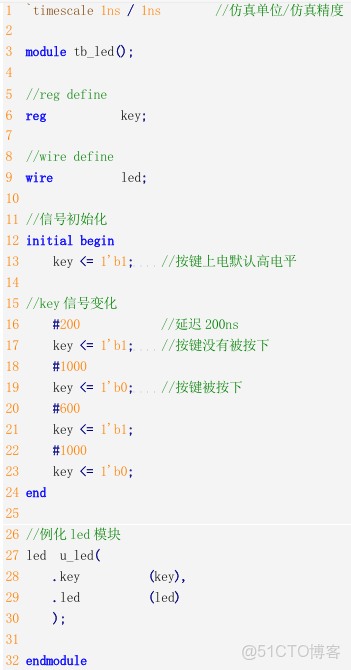

3、TestBench代碼:

通過----即使是小如led的模塊,也能夠(需要!)有一個TestBench。

----該TestBench中一共有5個離散的輸入,但依據時序構成一個離散輸入(&變化)的序列。

----問題!該Testbench的5個離散輸入,預期有5個離散的輸出。但在Testbench代碼中未使用assert()和printf()這樣的方法!若是使用assert()和print()方式,則可能自動化地運行。

----怎麼辦?使用FPGA的仿真工具軟件,將TestBench代碼(led_tb.v)的運行結果輸出為波形文件,然後查看波形。

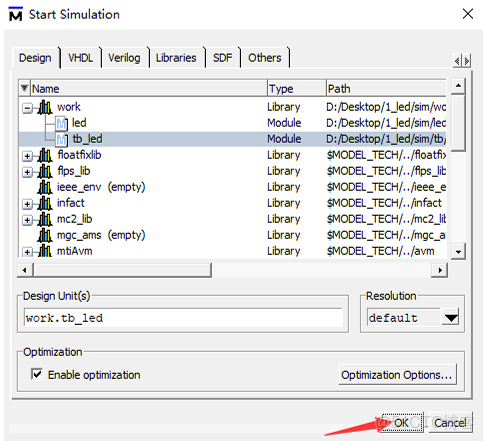

4、開始仿真:

----該Start Simulation對話框中,選定了Design Unit為work.tb_led。點OK開始仿真。

----運行仿真以後的運行結果,顯式波形圖。所謂波形圖,就是led電路實例(實例名為u_led)上的key管腳和led管腳上的電平(信號)值、隨着時序的推進時的變化。

5、上FPGA芯片和板卡上實際運行!雞凍的時刻?

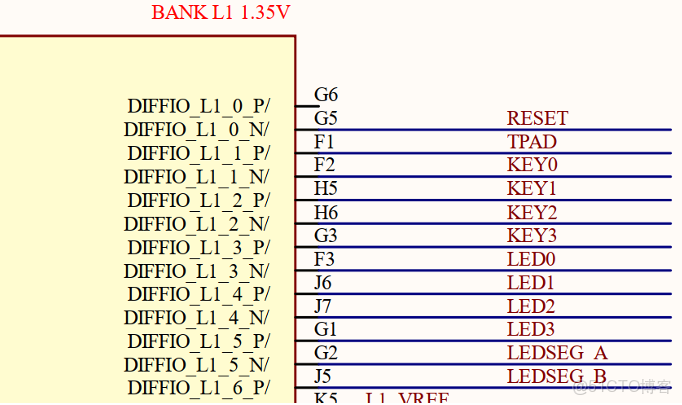

(1)就上面那麼一個“抽象”的led.v的電路模塊,FPGA怎麼知道代碼中的key管腳,和FPGA板的某個管腳對應呢?同理,led管腳和FPGA的某個管腳對應呢?這就要看FPGA開發板的原理圖了!

----這個原理圖行看出,開發板KEY0~3以及LED0~3對應的FPGA芯片的管腳分別哪個。

----這個表列出的管腳F2/F3就是FPGA芯片的管腳。

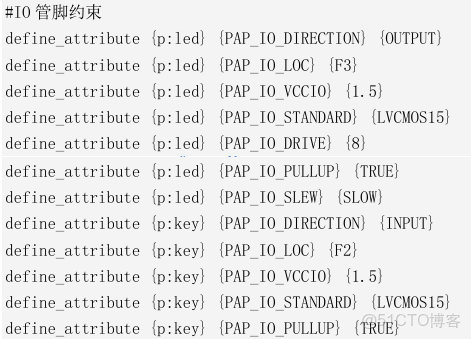

----將led.v代碼中的信號名,與FPGA芯片的管腳對應,該過程叫“增加約束”,Add Constraints。

----增加約束的結果,在後台實際上保存為文本文件。在某個FPGA平台下,這個約束文件的後綴叫fdc,本例中的文件名相應地叫led.fdc,文件內容如下。

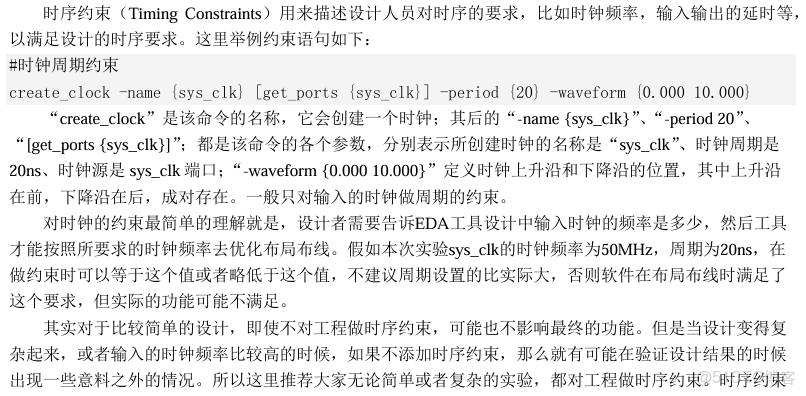

其中的IO管腳約束。在約束文件裏還會有其它的約束,比如時序約束。就是----這還只

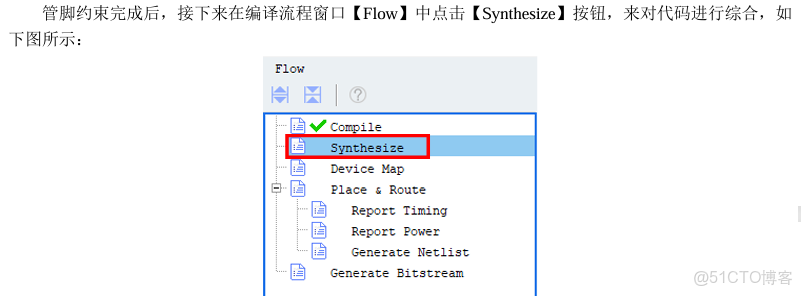

----然後基於led.v文件和led.fdc資料,使用FPGA的綜合工具,將源文件綜合為位流文件(BitStream資料),本例中為led.sbit資料。

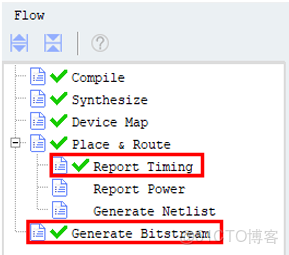

----一直到如下的狀態:

----此時已經生成led.sbit的文件。

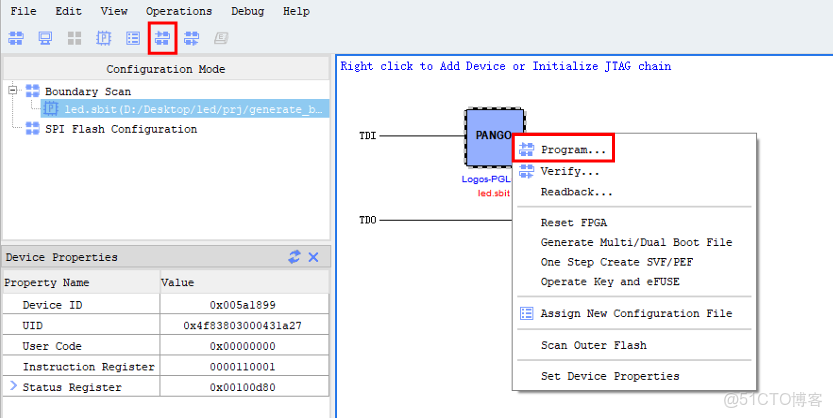

----啓用Boundary Scan掃描出研發PC上經過JTAG所連接的設備型號。然後添加上前面所生成的led.sbit檔案。再然後使用Program將位流文件下載到FPGA芯片中。本例中是PANGO的FPGA芯片。

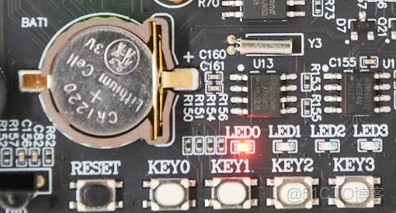

----然後,就可以在開發板上觀看到效果了。按一下key(開發板上的KEY0),則相應的LED燈亮(開發板上的LED0)。

該程序了。就是----此前的燒寫是直接燒寫到FPGA芯片的SRAM裏了,因為現在大多數FPGA都是SRAM作為可編程陣列的開關了。要想在斷電以後重新插電,還有這個效果,那就得把位流文件下載到非易失性存儲器中了,而且後續整個FPGA板的系統級行為就

----不過不用擔心,FPGA開發板可能會獻出一個系統出場時默認的位流檔案,許可燒寫它把體系上更豐富的功能展現出來。

7、總結:

----本文利用FPGA上的入門示例,梳理和備忘一下FPGA研發的主流程,包括:

----編寫RTL代碼。

----編寫TestBench代碼。

----使用FPGA所提供的EDA工具之RTL仿真,以RTL代碼和TestBench代碼為輸入,以波形文件為輸出,並使用波形查看的GUI工具查看波形!

----編寫IO約束,這是FPGA研發必須要的,因為RTL代碼中的管腳和FPGA芯片的對應必須通過IO約束才能達成,沒有這個IO約束,RTL代碼無法進行綜合(for FPGA)。

----使用FPGA所提供的EDA應用之RTL綜合,以RTL代碼+IO約束文件為輸入,以位流材料(BitStream)為輸出,生成綜合後的最終文件。

----使用FPGA所提供的下載器和下載軟件小兒科了。就是,將位流文件下載到FPGA芯片中,便可以在FPGA芯片中運行了。至於説下載到FPGA芯片中的SRAM,還是下載到片內SRAM+片外Flash中,這些都

<<<<<<<<完>>>>>>>>

文末貼一個圖,作為發帖的封面。

摘要:本文詳細介紹了FPGA開發中LED控制模塊的完成流程:通過三極管柵極控制LED開關原理,完成RTL代碼設計;強調TestBench的必要性,建議利用assert和printf實現自動化測試;説明仿真波形驗證方法;重點闡述FPGA開發關鍵步驟 - 利用約束文件將RTL信號與芯片管腳綁定,生成位流文件並下載到FPGA;最後總結了完整的FPGA開發流程,包括RTL編碼、仿真驗證、約束編寫、綜合實現和程序下載等核心環節。該流程適用於各類FPGA開發項目,是硬件開發的標準化方法。