在數字世界裏,數據的傳輸與存儲無處不在。但伴隨而來的,是噪聲、缺陷、傳輸錯誤等潛在威脅。錯誤糾正碼(Error Correction Code,ECC)作為保障數據可靠性的核心技術,成為芯片設計、內存架構和系統安全中不可或缺的一環。本文將從ECC的原理、常見方法到在DRAM中的應用逐層展開,並結合學習資源,幫助工程師與學習者全面理解這一關鍵技術。

ECC的基本原理

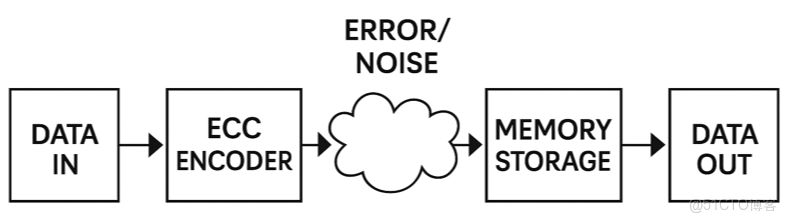

ECC的核心思想,是通過冗餘信息來檢測和糾正數據錯誤。

噪聲與干擾:當數據被讀取或傳輸時,隨機噪聲會改變比特值。

冗餘信息:ECC利用額外的校驗比特,使接收端能夠判斷甚至修復錯誤。

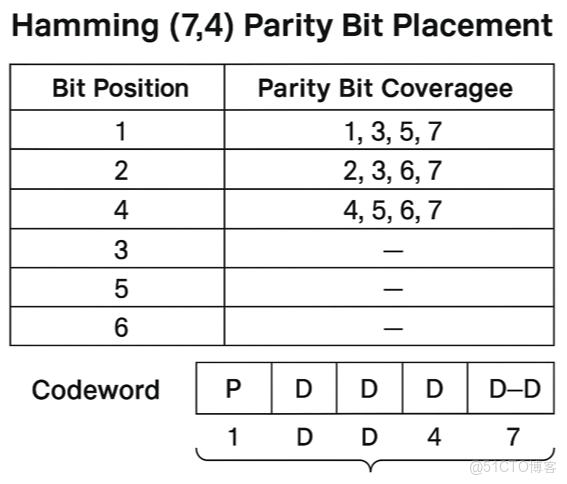

糾錯能力:以常見的漢明碼(Hamming Code)為例,能夠實現“單錯糾正、雙錯檢測”(SECDED)。

越強大的ECC方案,需要更多計算資源與存儲開銷。如果在硬件層面完成,就意味着更大的硅面積;在軟件層面完成,則意味着更多CPU週期。

ECC的進化

ECC技術並非一成不變,而是不斷演進:

第一代:以漢明碼為代表,解決單比特錯誤。

第二代:發展到可修復整顆器件級別錯誤。

第三代:在芯片內部直接集成ECC,提供更底層的保護。

這些演進不僅提升了數據安全,也讓工程師在設計和測試環節中有了更大的靈活性。例如,可以將部分糾錯能力用於修復已知壞單元,而將另一部分用於運行時抗噪聲,形成靈活的資源分配。

ECC在DRAM中的四種應用方式

DRAM作為計算機系統的核心存儲,ECC在其中的實現方式尤為多樣。

1、旁帶式(Side-band ECC)

額外增加存儲芯片專門用於保存校驗碼。

控制器負責在寫入和讀取時計算與校驗。

優點:簡單高效,應用廣泛。

2、內嵌式(In-line ECC)

數據與校驗碼共存在同一存儲芯片內。

常用於LPDDR等16位總線架構,避免總線過寬。

缺點:需要額外的讀寫操作,帶來延遲。

3、芯片內ECC(On-chip ECC)

從DDR5開始普及,錯誤在傳輸到控制器前即可修復。

但無法檢測傳輸鏈路上的錯誤,需配合其他機制。

4、鏈路ECC(Link ECC)

專注於傳輸鏈路數據的保護,發送和接收兩端均計算校驗。

與芯片內ECC結合,才能實現端到端完整保護。

此外,還有循環冗餘校驗(CRC)作為另一種保障數據傳輸可靠性的選擇。

ECC與設計權衡

ECC的強弱設計,本質上是性能、成本與安全性的博弈:

更強的糾錯能力 = 更高的硅片面積或更多CPU計算。

更大的校驗塊 = 更昂貴的存儲成本。

靈活使用ECC比特 = 更精細的設計與測試策略。

因此,不同應用場景需要量身定製的ECC方案。例如,企業級服務器偏好強ECC以保證穩定,而消費級設備則更關注性能與成本平衡。