介紹

JESD204B是用於轉換設備(data converters devices,也就是AD/DA)和邏輯設備(logic devices,也就是FPGA或ASIC)交互數據的串行接口。

協議有時會用converter、logic device而不是TX、RX做描述,因為converter、logic分別作TX、RX時會有細微差別。此外協議規定的場景中可能會有多個AD/DA,但只會有1個logic device。

(1)和JESD204A區別

JESD204、JESD204A、JESD204B框架行見下圖,204B和204A區別在:

• 串行信息最高速率提升到12.5 Gbps。

• 參考時鐘從frame_clk變為了device_clk。

• 針對確定性延時(deterministic delay)增加同步機制,JESD204B的Subclass1、2子類支撐同步,後面會有單獨小節詳細描述。確定性延時的意思就是每次上電都一樣的延時,可能是因為走線或者片間差異,機制是以多幀LMFC為單位對齊延時,後面也會詳細描述。

藉由環境圖,可以看到首先JESD204B是單向傳輸,每個link包含多個lane,每個lane是一對差分的p/n線。TX和RX需要同源的device clock,圖中省去了RX給TX的SYNC信號。對於Subclass1,TX和RX還需要和device clock同步的SYSREF輸入。除此之外,協議層面在片間就沒有其他連線或時鐘信號了。

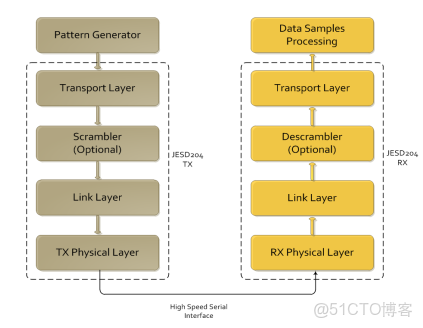

協議層

JESD204B協議包含傳輸層、鏈路層和物理層,此外還可以加入加解擾層。傳輸層的能力是將各種AD/DA數據形式轉換為8bit形式,鏈路層的功能是8b10b編碼和建鏈,物理層的功能是實現Serdes的串並轉換,對於RX還具備CDR電路用來恢復時鐘。

傳輸層(Transport Layer)

要看有幾個轉換器和幾個link。就是傳輸層的機制是將AD/DA採集的信息轉換為8bit形式(octet)。包括1個轉換器到1個link、多個轉換器到1個link、1個轉換器到多個link、多個轉換器到多個link的情況,簡單的説就

(1)傳輸層參數

基本參數,有L個lane,M個AD/DA通道,每次採S個點(>1即過採樣),每個點量化為N bit。就是首先

• L :lane數量。

• M :converter的數量。

• S :每幀採樣點數(後面會介紹幀概念)。

• N :轉換分辨率(即AD採樣位數)。

實際每次採樣對應的位數是N’,協議要求單採樣點大小為4 bit的整數倍,對於非整數倍的N必須補位,此外根據需求許可加控制位,例如指示採樣溢出。

• N’:補位後的採樣位數,N′=N+CS+T。

• CS: 可選控制位

• T:可選尾位

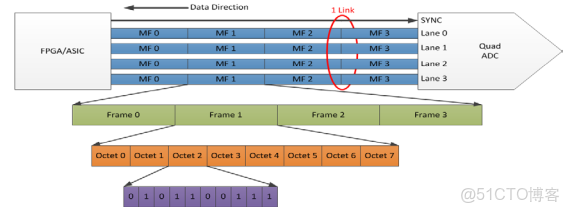

可以通過上述參數計算出來的。幀對應幀時鐘(frame clock),幀時鐘為內部(local)時鐘,對外不可見。就是在上述參數的基礎上,協議定義幀(frame)的概念,幀就是一次採樣,要清晰幀的概念,後續會多次出現。1幀包含S個過採樣點,M個通道。幀的字節數F

• F :每一幀的字節數(octets),F=(M×S×N′)/(8×L)。

• CF: 可選控制位,和CS相似不過是一幀補一次,上公式算沒算上CF。

在幀的基礎上,再定義多幀,將K個幀定義為一個多幀,多幀週期同樣是內部時鐘,稱為LMFC(Local Multiple Frame Clock),LMFC定義也需要清晰,後續會多次出現。

•K :多幀情況下的幀數

各層關係可以參照下圖,以多幀(藍色)進行傳輸,每個多幀又涵蓋幀(綠色),每個幀又包括octets(橘色)。

用來同步對齊的,即針對確定性延時,大家都按同源device clock產生的LMFC週期同時採用或生成數據,從而實現多個轉換器的數據對齊,在確定性延時小節還會詳細講解。就是幀的概念比較好理解,可能會疑惑為什麼採樣都是連續的還要定義多幀,簡單的説多幀

(2)空採樣(Dummy samples)

通過轉換器非有效時發送空採樣數據,例如有多個轉換器但部分沒工作,協議其實對這種情況下發什麼沒有限定,協議建議能夠發一些偽隨機序列。

(3)測試模式(Test modes)

傳輸層支持測試序列,具體包含長測試碼型(long transport layer test pattern)和短測試碼型。普通的測試方法是在模擬側轉換器進行採樣,接收數據後憑藉頻譜、信噪比等參數確認傳輸正常。而使用傳輸層的測試序列可以完全在數字區域,單獨對lane間收發傳輸進行測試(後面鏈路層還有單獨鏈路層測試的方法)。

短測試碼型(short test pattern)以幀為週期循環,長測試碼型(long test pattern)以幀為max(M·S+2, 4)向上舍入到多幀數為週期循環。協議要求邏輯設備必須支持測試碼型,轉換器設備可以選擇支持長碼型或短碼型。

轉換器的生產廠商確定測試序列的碼型內容,例如AD,那就是AD發送固定測試碼型,FPGA接收並判斷和AD手冊上寫的固定測試碼型是否相符;例如DA,那就是FPGA按DA手冊要求發送固定測試碼型,藉助DA的寄存器指示接收比對是否正確。

鏈路層(Link layer)

鏈路層主導實現8b10b編碼和碼同步。

(1)8b10b編碼

8b10b編碼可以參見文章8b10b編碼詳解,簡單易懂然後按照從MSB到LSB進行傳輸,即先發10b中的bit “a”。

(2)碼同步

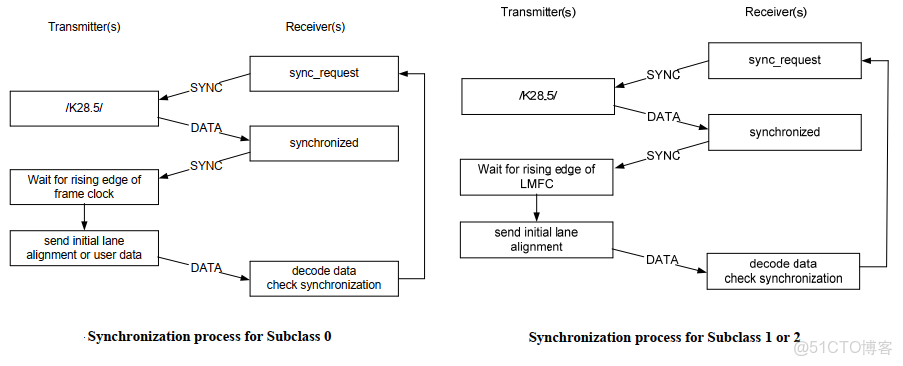

JESD204B的同步流程如下圖,具體步驟為:

• RX將SYNC拉低,發起同步請求。

• TX檢測SYNC拉低後發送K28.5序列。

• RX收到連續多個K28.5序列後,將SYNC拉高,指示碼同步搞定。

• TX檢測SYNC拉高後發送ILA初始化序列

• TX然後開始傳輸數據

子類Subclass 0和Subclass 1、2的區別在,Subclass 0在檢測到SYNC拉高後的第1個frame clock開始輸出;Subclass 1、2在SYNC拉高後的第1個LMFC開始輸出。

(3)波形示例

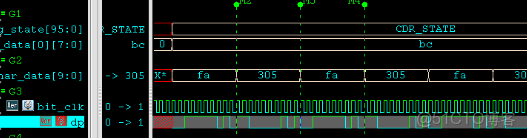

下面以Subclass 0傳輸波形為示例,上面是RX lane,下面是TX lane,許可看到傳輸步驟如下:

a)初始SYNC為低,所以TX開始發送K28.5序列。

b)RX的CDR電路依據序列恢復出lane時鐘。

c)RX使能SYNC信號。

d)TX檢測到SYNC後,開始發送ILA序列,序列長度為4個LMFC週期。由於是Subclass 0,起始相位和LMFC沒有固定關係。

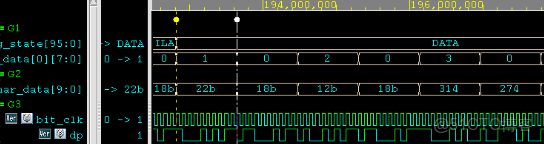

e)TX發送完ILAS後開始發送數據。

0xbc,依據8b10b編碼規則,會按照RD-和RD+循環分別編碼成0xfa和0x305,從差分線dp/dn上可以看到先發高位再發低位。就是步驟a)中,TX持續發送K28.5,也就

步驟e)中,示例N‘=16bit,數據為1、2、3,按照8bit拆分為0、1、0、2、0、3。0按RD+查表得到0x18b,RD符號不變,1按照RD+查表得到0x22b,RD符號不變,0又查到0x18b,2按RD+查表得到0x12b,以此類推。

最後是Subclass 1/2的波形示例,關注lmfc_clk信號,和Subclass0區別在傳輸均以LMFC週期為對齊。

(4)錯誤處理

協議要求設備必須支持一些錯誤類型:

• Disparity error :收到的10bit失衡,例如當前狀態RD-,但收到了RD+列裏的數。

• Not-in-table error:收到的10bit無效,不在8b10b編碼表中。

• Unexpected control character:是有效的控制字符,但出現位置不對。

• Code group synchronization error:同步錯誤,狀態機重新回到初始態。

要求可選支持錯誤類型:

• Frame realigned (previous conversion samples may be in error)

• Lane realigned (previous conversion samples may be in error)

• Uncorrectable frame alignment error

• Initial lane alignment failure

• Uncorrectable lane alignment error

• Link configuration data error (parameters in TX and RX do not match)

• Lane alignment sequence decoding error (wrong octets decoded)

對於錯誤的處理分為可以繼續傳輸和得重新初始化(即SYNC拉低),協議中針對錯誤的處理方式基本都是建議。例如編碼錯誤則用上一幀的數據,RD錯誤則以接收RD為準。對於重新初始化,RX應該將SYNC拉低至少5幀+9個字符的長度。

還有一種特殊情況,就是用SYNC指示錯誤但又不希望重新初始化。對於Subclass 1或Subclass 2,可以將SYNC拉低2幀指示錯誤,同時不能跨越LMFC邊界。為了兼容JESD204A,還可以選擇協助將SYNC拉低1幀指示錯誤。此外Subclass 2會使用SYNC信號進行同步,所以要注意以同步功能為優先。

(5)測試模式

鏈路層的測試模式就是所有幀、link和lane上發送預先定好的的8b10b編碼,此時不能加擾。

協議要求TX設備應當有發送下列測試序列的能力:

• 連續的/D21.5/字符,高頻碼型,用於測試隨機抖動(random jitter RJ)和接收測眼圖。

• 連續的/K28.5/字符,混合頻率碼型,用於測試確定性抖動(deterministic jitter DJ)

• 連續發送ILA初始化對齊序列

要求至少包含1中下面2個碼型

• 包含可變隨機碼型的連續序列(modified RPAT)

•包含擾動抖動的連續序列(JSPAT)

INCITS TR-35-2004中定義了12-octet modified RPAT碼型,INCITS 450-2009中定義了50-octet JSPAT碼型。除此之外,發送設備還可以擁護其他標準的鏈路層測試碼型,例如低頻的/K28.7/碼型或偽隨機序列(PRBS)。

物理層( Physical layer)

JESD204B的物理層摒棄了前代單一速率標準,劃分了三個速度檔位,分別適配 OIF 組織的三種電氣接口規範,分別為:

• LV-OIF-SxI5 – based operation: from 312.5 Mbps to 3.125 Gbps (adapted from OIF SxI-5).

• LV-OIF-6G-SR – based operation: from 312.5 Mbps to 6.375 Gbps (adapted from CEI-6G-SR).

• LV-OIF-11G-SR – based operation: from 312.5 Mbps to 12.5 Gbps (adapted from CEI-11G-SR)

物理層採用 CML 電平完成高速信號傳輸,主要涵蓋完成高度串並轉換的Serdes模塊,對於RX還包含CDR電路用來恢復時鐘。。