在高速數據交換、服務器加速卡、嵌入式系統裏, PCIe 接口幾乎是“必備武器”。但對於很多 FPGA 工程師來説,自己實現一條 PCIe 通道從零起步仍然很困難——涉及 TLP 層、BAR 映射、DMA 引擎、收發邏輯、時鐘域交叉、PHY 部署…… 好消息是,有一個開源項目 LitePCIe 為你掃清了這條路。

✅ 項目簡介

一個由 Enjoy‑Digital(https://github.com/enjoy-digital) 組織維護的“輕量級且可設置”的 PCIe 核心。它關鍵特點包括:就是LitePCIe

- 支持多種 FPGA 設備:例如 Xilinx 7 系列(可達 Gen2 x8)、UltraScale(+) (可達 Gen3 x16)等。

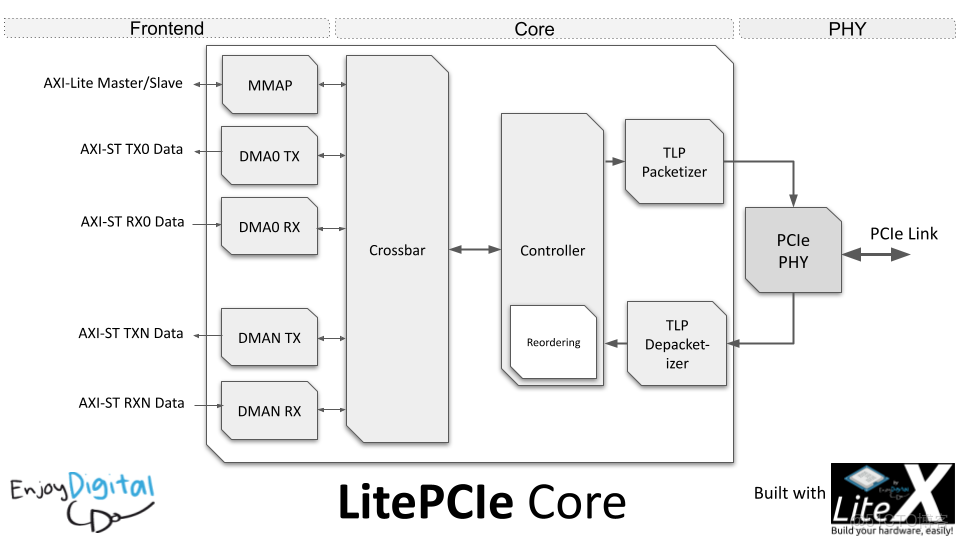

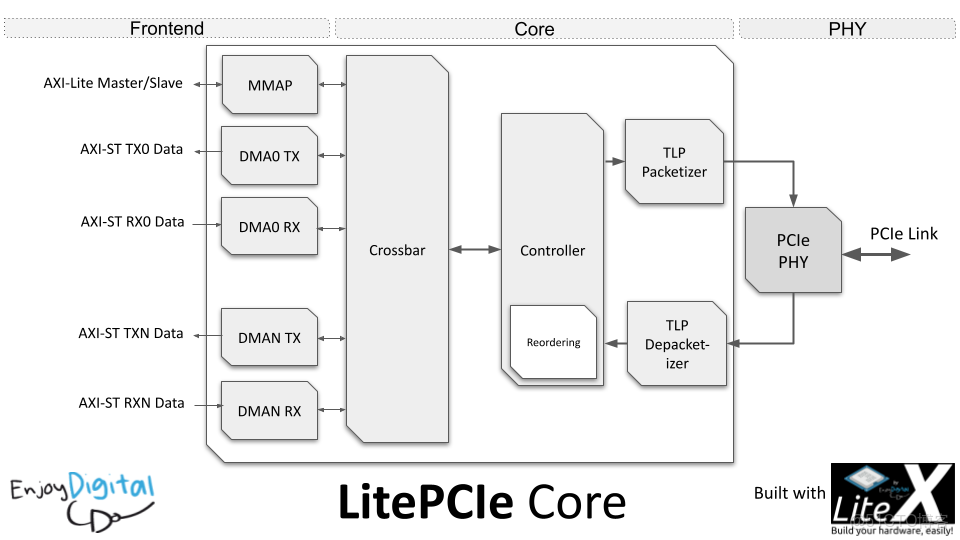

- 內置 TLP 層、重排序機制 (reordering)、MSI / MSI-X 支撐、交叉開關 (crossbar) 結構。

- 支持 DMA(Scatter-Gather)、映射接口 (MMAP)、AXI/Wishbone 主/從等。

- 採用 Python + Migen 設備鏈描述邏輯,高度可配置,也可生成 Verilog 供傳統 FPGA 流程使用。

也就是説,假設你要在 FPGA 上實現高速 PCIe 數據通道、構建高性能卡片或加速器,LitePCIe 絕對是一個“起點即戰力”的開源方案。

架構亮點拆解

幾個核心技術亮點:就是以下

• PHY 接口支持

LitePCIe 支持如下 PHY 層:

- Xilinx Ultrascale(+):高帶寬、協助 Gen3、x16。

- Xilinx 7 系列:支持 Gen2 x8。

- Intel Cyclone5:支持 Gen2 x4。

這説明項目兼具“高端擴展性”和“入門門檻低”的優勢。

• 核心功能層

最關鍵的部分。LitePCIe 將其模塊化、開源化,使 FPGA 工程師能夠直接“拿來用”,再在此基礎做定製。就是包括 TLP 層、重排序、交叉開關、MSI 支持等,這些都是傳統 PCIe 核中最難實現、但也

• 前端接口

為了讓你 真正在 FPGA 內部做信息搬運/加速/交互。就是承受DMA + Scatter-Gather、MMAP (AXI/Wishbone) 等方式進行數據讀寫。也就是説,這個核不只是為了 “連通 PCIe”,更

• 開源工具鏈 &可生成 RTL

項目是用 Python + Migen 編寫,用户既可能在 LiteX 生態中使用,也可以導出 Verilog 加入傳統 FPGA 開發流程。對於國內團隊來説,這意味着“開源 + 可定製 + 易遷移”。

• 架構説明

① LitePCIe 內部模塊劃分示意

用途:直觀展示整個 LitePCIe 核心結構(PHY 層、TLP 層、DMA、跨總線等)。

② LitePCIe + LiteX 平台生態圖

用途:展示 LitePCIe 如何融入整個 LiteX 生態,與 LiteDRAM / LiteEth / LiteSDCard 等協同。

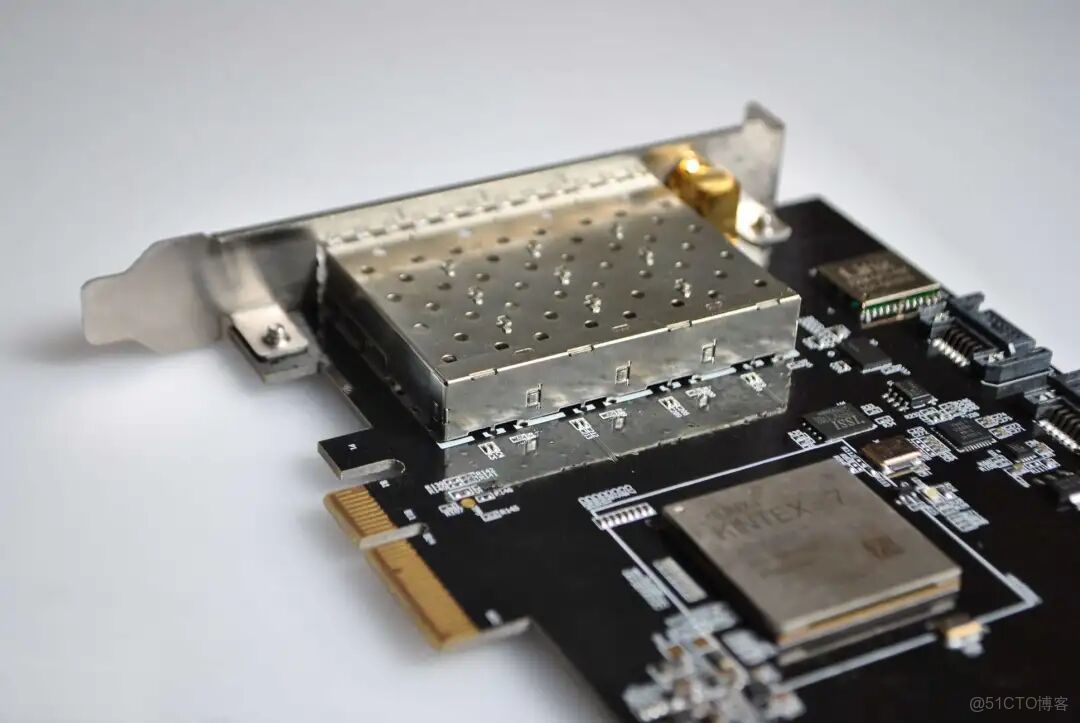

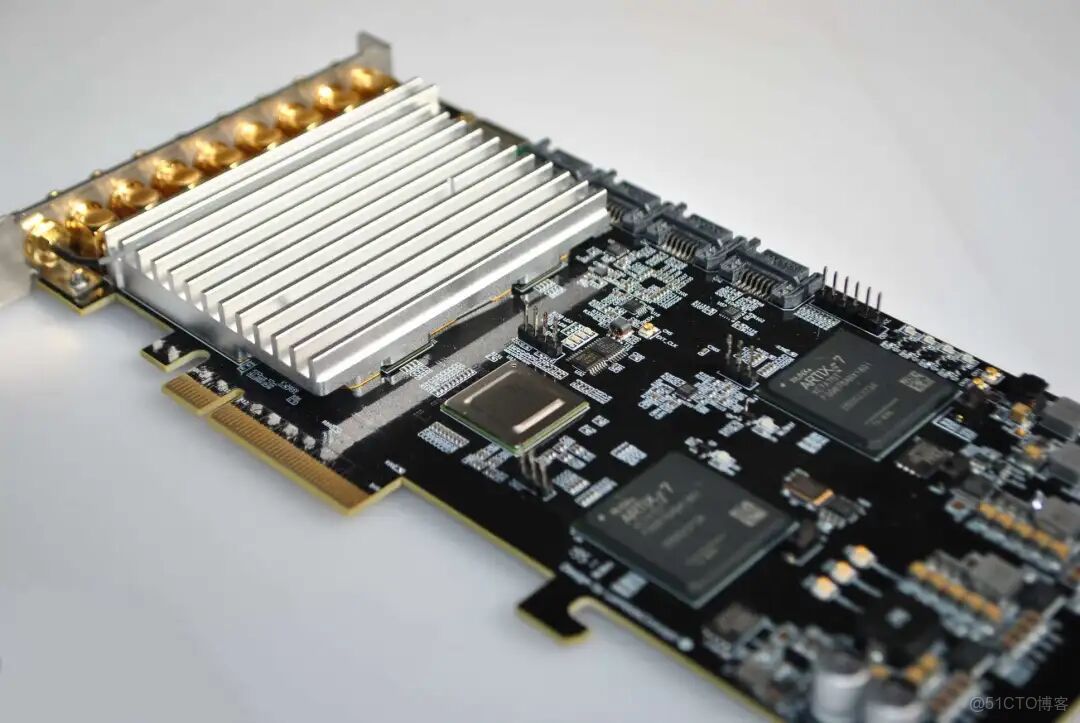

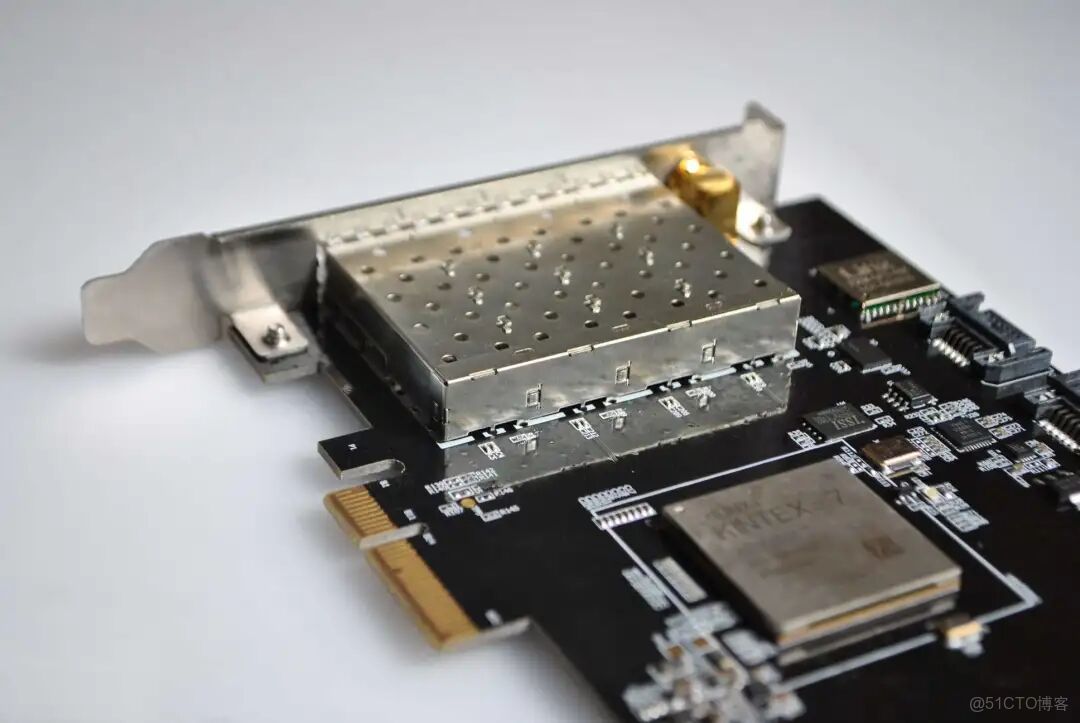

③ FPGA 板卡實拍圖(測試板卡)

工程應用場景

以下幾個場景特別適合用 LitePCIe:

- 高速採集卡/存儲卡:FPGA 做資料預處理 → 經過 PCIe 發送給主機;

- 數據中心 FPGA 加速卡:例如 DPDK 數據包處理、網絡卸載;

- 嵌入式系統中:FPGA 與 CPU 協作,通過 PCIe 完成高速交互;

- 教學與研究平台:用於學生理解 PCIe 協議、實踐 FPGA 設計。

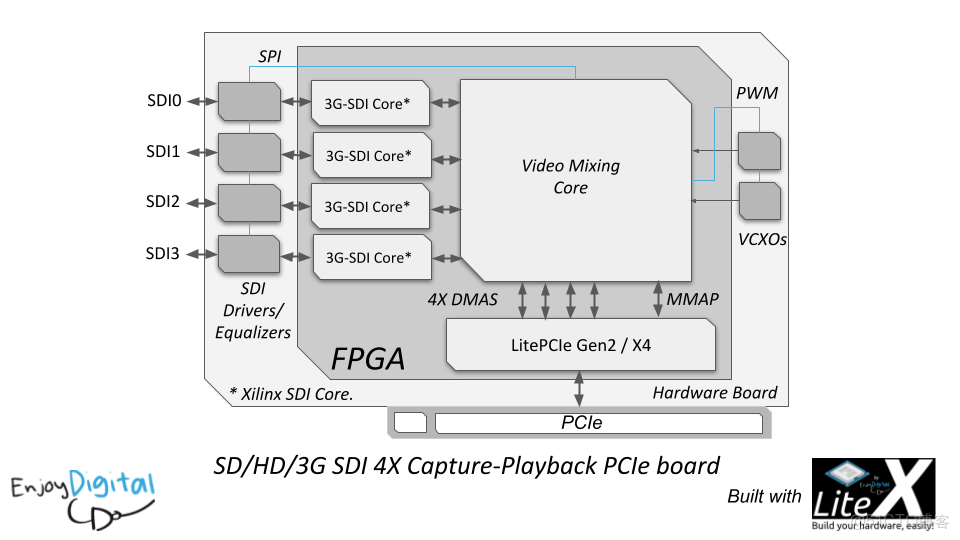

- 3G-SDI Capture/Playback board:

http://www.enjoy-digital.fr/experience/pcie_3g_sdi.jpg

- SDR MIMO 2x2 board:

https://www.amarisoft.com/products-lte-ue-ots-sdr-pcie/#sdr

- SDR MIMO 4x4 board:

http://www.enjoy-digital.fr/experience/pcie_ad937x.jpg

- SDR CPRI board:

http://www.enjoy-digital.fr/experience/pcie_sfp.jpg

小結

開源 PCIe 核意味着 不必從零開始設計 TLP/BAR/MSI 邏輯,能大幅降低難度。

承受 Python + Migen 描述,降低傳統 HDL 門檻,更符合“軟件化+硬件化”融合趨勢(國內認可度不高)。

可以借鑑其模塊化結構、平台適配方式、工具鏈遷移經驗,助力國產 FPGA 生態建設。

LitePCIe 不僅是一個“開源 PCIe 核”,更是一個“FPGA 開發者加速器”。

它讓 PCIe 從難題變成可控模塊,讓你在 FPGA 設計裏,把更多精力放在“算法/數據流”而不是“協議細節”。