一、引言

ZYNQ 是來自 Xilinx 公司 ZYNQ-7000 所有可編程片上系統的開發板,具有開發片上系統能力。

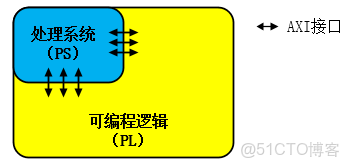

在 ZYNQ 上,ARM Cortex-A9 是一個應用級的處理器,能運行完整的像 Linux 這樣的操作系統,而可編程邏輯是基於 Xilinx 7 系列的 FPGA ,兩部分之間採用標準 AXI 接口實現了高帶寬、低延遲連接。

二、ZYNQ與片上系統(SOC)

對於片上系統,我們比較熟悉的是:基於ASIC的片上系統,舉例來講PC、平板以及智能手機等都屬於此類片上系統,其缺點主要是缺乏靈活性,升級能力差。因此,催生了一種可編程,硬件可重新配置的Soc。而FPGA恰好可以彌補這一缺點,可以被配置來實現任何芯片,甚至可以實現嵌入式處理器。

ZYNQ就是這樣一種基於FPGA的Soc,主要包含兩部分:PS(Processing System)部分是由雙核ARM Cortex-A9構成的處理系統,PL(Programmable Logic)部分等價於一片FPGA可編程邏輯;另外集成了存儲器,一些外設和高速通信接口。

PL部分主要用來實現高速邏輯、簡單算術和數據流處理,PS部分支持軟件設計或者操作系統。對於任意算法都可以在PL和PS部分恰當劃分,通過軟硬件協同設計思想在ZYNQ平台實現。PL和PS部分的連接是採用高級可擴展接口(Advanced eXtensible Interface,AXI)。處理器即 ARM Cortex-A9 作為 ZYNQ 的中央單元,運行軟件系統,外設是除處理系統之外的部件,其功能為:1.協處理器---輔助主處理器,被優化用於特定任務或算法加速;2.與外部接口交互;3.存儲器資源。

三、ZYNQ模塊化設計

在ZYNQ上進行嵌入式系統開發除了具有靈活性高這一優勢外,還具有可設計重用優勢。IP(Intellectual Property)核,即知識產權模塊,就是屬於上面講的外設部分,可以從Xilinx的設計工具中直接調用,也可以從其他項目中重用,或者從第三方開源庫獲得,然後將所有模塊集成起來進行系統設計。ZYNQ就具有大量標準IP,因此開發時,這些IP部件無需我們再次設計,而是直接引用,從而加速開發,降低成本。

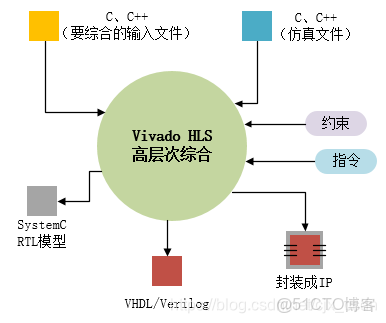

如果ZYNQ標準庫中沒有的IP,我們也可以自己封裝,接口採用AXI協議。在這兒就不得不提到高層次綜合工具(High Level Synthesis),可以用比傳統的寄存器傳輸級 (Register Transfer Level,RTL)方式 更少的細節來創建系統部件,進一步提高了我們對ZYNQ的開發效率。不過,採用HLS工具封裝的IP一般為AXI接口,靈活性差是一大缺點,當然採用該開發工具的缺點還有很多,但我關注的是採用 HLS 可以讓我們快速的將算法佈置在FPGA端,尤其是針對一些複雜的算法,如果採用RTL級邏輯代碼設計,難度較大,需要設計人員具備豐富的開發經驗。隨着算法功能變得愈發複雜,開發週期也愈發漫長。設計人員現在往往需要在給定項目中實現數十萬行 HDL 代碼,逐次綜合,仿真每個模塊,以確保設計實現細節正確,把大部分時間花在細節的實現工作上,而不是設計更具價值的算法。高層次綜合 HLS 是一種全新的邏輯設計思想,可直接從算法級對硬件電路進行描述,設計者可在更高層次上進行設計,仿真和驗證,不用過多關心具體的電路設計,因此可以將更多精力放在設計結構的優化上,將數字系統設計從繁瑣的底層硬件系統構建和設計中解放出來,把更多精力放在尋求最佳的設計方案上。