提示:基於Altera的FIR數字濾波器設計 2021

文章目錄

- 前言

- 一、FIR濾波器

- 二、Altera FPGA實現過程

- 1.抽頭係數

- 2.IP核配置

- 3.代碼

- 4.關於數據截斷問題

- 總結

前言

使用軟件版本 quartus ii 18.0

基於Altera的FIR數字濾波器設計

一、FIR濾波器

FIR濾波器是有限長單位衝激響應濾波器,又稱為非遞歸型濾波器,是數字信號處理系統中最基本的元件,它可以在保證任意幅頻特性的同時具有嚴格的線性相頻特性,同時其單位抽樣響應是有限長的,因而濾波器是穩定的系統。

二、Altera FPGA實現過程

1.抽頭係數

- 打開Matlab,輸入fdatool打開濾波器設計工具

(根據自己設計要求選取參數) - 然後導出抽頭係數。

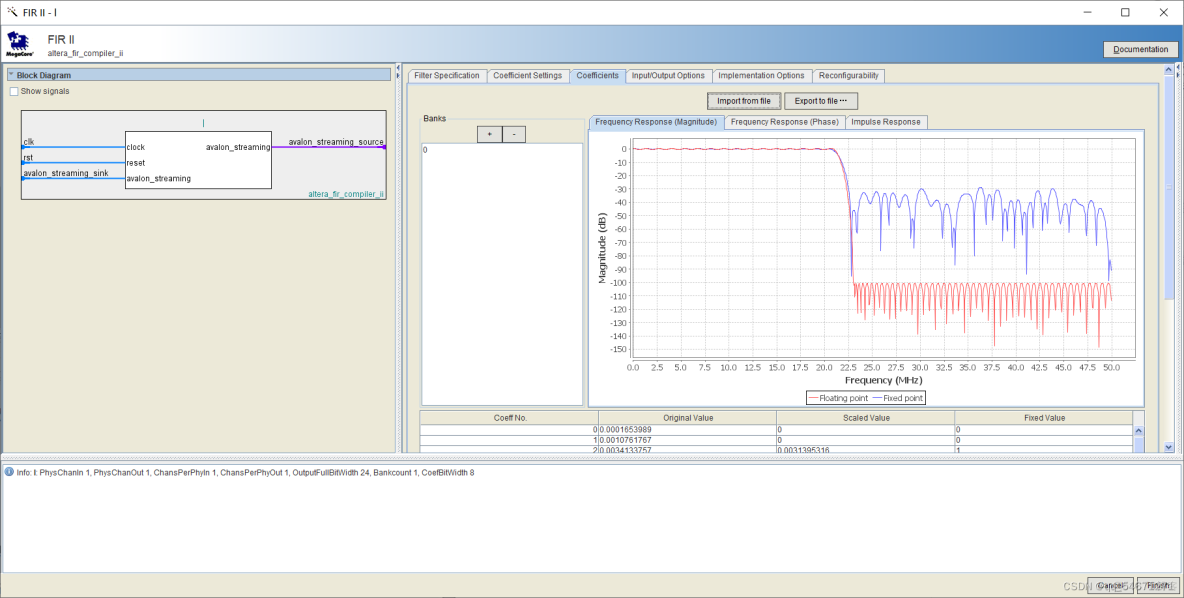

2.IP核配置

在配置界面配置好時鐘與抽頭係數的形式,然後導入之前生成好的抽頭係數。

輸出的配置暫時不用動,之後在代碼中實現數據位的截斷。

3.代碼

- 高速ADC

我這裏使用的ADC是8位ADC,ADC的時鐘設置50KHz。 - 高速DAC

DAC是10位DA,DA的時鐘設置50KHz。

//`配置AD DA模塊

always @(posedge sys_clk or negedge sys_rst_n)

begin

if(!sys_rst_n)

begin

AD_Clk<=1'b0;

clk_cnt<=32'd0;

end

else

if(clk_cnt==32'd499)//sample 50K

begin

AD_Clk<=~AD_Clk;

DA_Clk<=~DA_Clk;

clk_cnt<=32'd0;

end

else

clk_cnt<=clk_cnt+1'b1;

end

always @ (posedge sys_clk or negedge sys_rst_n)

begin

if(sys_rst_n == 1'b0)

cnt <= 6'd0;

else if(cnt == 6'd999)

cnt <= 6'd0;

else

cnt <= cnt + 1'b1;

end- IP核配置代碼

FIR IP的例化程序代碼。

4.關於數據截斷問題

//`

fir_ip fir_ip_inst(

. clk (sys_clk),

. reset_n (sys_rst_n),

. ast_sink_data (AD_Dat_tmp),

. ast_sink_valid (fs_pulse),

. ast_sink_error (2’b0),

. ast_source_data (ast_source_data),

. ast_source_valid (ast_source_valid),

. ast_source_error (ast_source_error)

);關於信號ast_source_data數據位的截斷

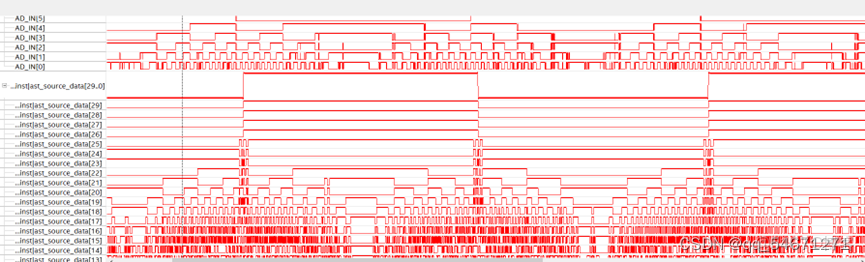

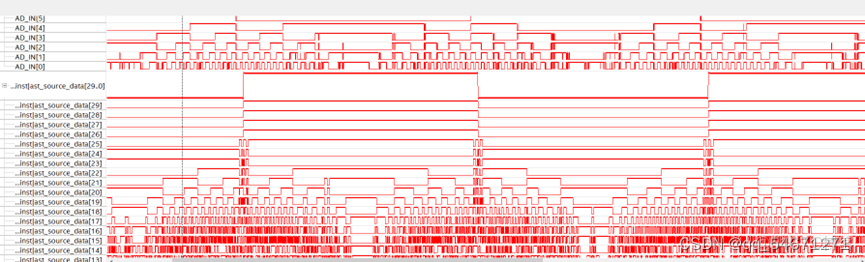

可以在singaltap裏面觀察ast_source_data波形,然後選擇保留兩三個符號位剩下的為數據位

例如這個,選擇[27:18]就可以(根據不同的DA芯片的位數不同,選擇的截斷長度也不同,這裏只是給出一個參考)

總結

以上就是設計FPGA數字濾波器的全過程,很簡單。如果上板成功得到的波形是正弦階梯波的形式,你還需要做一個模擬低通濾波器過濾高頻諧波,進行波的整形。