目錄

12、核心調試控制器

12.1、運行控制特性

12.2、調試事件

12.2.1、外部調試事件

12.2.2、調整宏指令

12.2.3、MTCR和MFCR指令

12.2.4、觸發事件單元

12.3、調試觸發器

12.3.1、組合調試觸發器

12.3.2、任務特定的調試觸發器

12.3.3、累計調試觸發信息

12.4、調試操作

12.4.1、更新調試狀態寄存器(DBGSR)

12.4.2、顯示核心斷開信號

12.4.3、顯示核心暫停輸出信號

12.4.4、停止

12.4.5、斷點陷阱

12.4.6、斷點中斷

12.4.7、暫停輸出

12.4.8、性能計數器啓動/停止

12.4.9、None

12.4.10、Disabled

12.4.11、掛起暫停

12.5、調試事件的優先級

12.6、回調跟蹤

12.7、調試控制寄存器

12.8、調試控制寄存器-摘要

12.9、調試控制寄存器

12.10、核心績效衡量與分析

12.11、性能計數器寄存器

12、核心調試控制器

TriCore™ 調試功能是架構、實施和軟件工具的接口。請用户注意,後續架構的機制可能會有所不同。

需要非侵入式調試的實時系統。CPU內核和內核片上存儲器中的大多數架構狀態都可以通過系統地址映射訪問。

對核心調試的訪問通常通過包含CPU的系統的片上調試支持(OCDS)提供。

核心調試控制器功能

核心調試控制器功能主要針對軟件開發環境。它提供實時運行控制以及數據和內存等資源的內部可見性。功能包括

- 實時運行控制(停止和重啓 CPU)。

- 訪問和更新內部寄存器和內核本地存儲器。

- 設置具有複雜觸發條件的斷點和觀察點。

使能核心調試控制器

DBGSR.DE == 0 時禁用內核調試控制器,DBGSR.DE == 1 時啓用內核調試控制器。如何控制 DBGSR.DE 位以及如何啓用或禁用內核調試控制器取決於系統。啓用核心調試控制器時,內核處於調試模式。(思考:在網上看到很多鎖Debug口,是通過這個功能嗎?好疑惑)

解釋環節:英飛凌的Core Debug Controller 是指通過PLS UDE調試嗎?還是什麼功能?

英飛凌的Core Debug Controller與PLS UDE調試密切相關,但不僅僅是通過PLS UDE進行調試。Core Debug Controller是芯片內部的一個模塊,主要用於控制和管理芯片的調試過程。它提供了多種功能,包括但不限於:

·多核調試支持:允許對多核系統進行同步調試,包括同時停止、單步執行和重新啓動不同核上的軟件。

·斷點設置:支持在共享代碼中設置多核斷點,簡化複雜應用的調試。

·實時監控和系統分析:提供實時監控功能,支持系統可視化和分析。

·非侵入式調試和跟蹤:通過代碼跟蹤和數據跟蹤,實現對系統運行時行為的觀察和測量。

·任務跟蹤和可視化:支持操作系統任務的跟蹤和可視化,幫助識別性能瓶頸。

·系統內編程:支持通過UDE進行系統內FLASH編程。

PLS UDE(Universal Debug Engine)是一款強大的調試工具,廣泛應用於包括英飛凌在內的多種架構芯片的調試。它通過與芯片的調試接口(如JTAG或DAP)進行通信,利用Core Debug Controller的功能來實現對芯片的調試和分析。

總結來説,Core Debug Controller是芯片內部用於調試的核心模塊,而PLS UDE是外部調試工具,兩者協同工作以實現高效的調試和系統分析。

看到這裏其實很明瞭了,也就是本章節要是深入理解可以看,只是使用本章節可自行選擇。

12.1、運行控制特性

實時運行控制功能通過地址映射讀寫進行訪問和控制,通常由 OCDS 或任何其他具有適當授權的總線主控器進行訪問和控制。內核調試控制器為內核提供硬件鈎子,允許檢測調試事件,從而採取調試行動。

核心調試控制器提供四種信號,用於與OCDS通信:

- 核連接。Core Break-In.

- OCDS 向核發出的相關條件指示。

- 核斷開(Core Break-Out)。

- 核向 OCDS 發出的相關狀態指示。

- 核掛起(Suspend-In)。

- OCDS 向核發出的進入 “停止 ”模式的指示。

- 核恢復。Core Suspend-Out

- 核向 OCDS 發出的調試狀態寄存器 (DBGSR) SUSP 字段 (DBGSR.SUSP) 狀態指示。該信號可通過寫入調試狀態寄存器來控制,而內核中斷信號則無法控制。

功能點

- 硬件支持單步調試。

- 可導致調試操作的調試事件:

- 向內核發出外部 Core Break-In 信號。

- 執行 DEBUG 指令。

- 執行 MTCR(移動到內核寄存器)或 MFCR(從內核寄存器移動)指令。

- 觸發事件單元引發的事件

- 調試操作可以是以下一種或多種:

- 更新調試狀態寄存器。

- 在內核中斷信號和/或內核暫停信號上顯示事件。

- 停止 CPU 執行。

- 採取斷點捕獲。

- 引發斷點中斷

- 控制性能計數器

實時功能

- 在內核運行時讀寫內核內存和寄存器,儘量減少干擾(可能會佔用週期)。

- 使用斷點中斷調試程序,為高優先級中斷例程提供服務。

注意:CPU 運行時讀寫其他系統內存可能會造成干擾,這取決於執行操作所需的週期數。當發生這種情況時,就會出現週期竊取。

調試事件和調試動作的編程可以在CPU運行時進行,很少或沒有入侵。調試事件的檢測對實時執行沒有影響。

12.2、調試事件

當Core Debug Controller開啓時,Debug Event可以通過以下方式生成:

·Core Break-In signal.

·Execution of a DEBUG instruction.

·Execution of the MTCR or MFCR instruction.

·A hardware Event generation unit.

12.2.1、外部調試事件

外部調試事件與指令流沒有任何關聯,但它提供了無需復位即可停止並獲得 CPU 控制權的能力。如果 CPU 當前正在執行多週期、不可取消的指令(例如上下文保存和恢復),調試事件可能需要幾個時鐘才能被 CPU 識別。

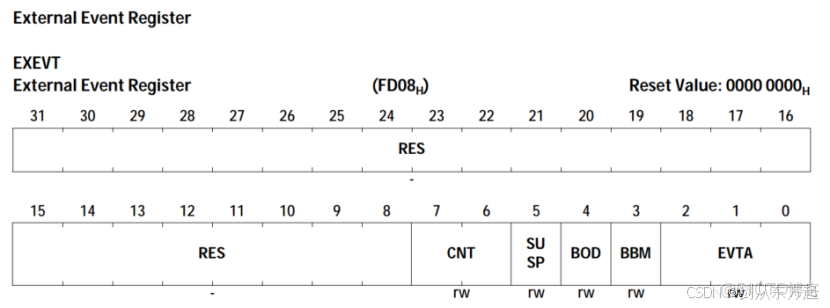

EXEVT (外部事件)寄存器中指定了核心斷開信號發生時的調試操作。

12.2.2、調整宏指令

TriCore 支持用户模式 DEBUG 指令,該指令可在啓用內核調試控制器時生成調試事件。當核心調試控制器被禁用時,它將被視為 NOP(無操作)。DEBUG 指令有 16 位和 32 位兩種形式。該功能有利於軟件調試,允許跳轉到監控程序,並提供了相對廉價的軟件儀器和詢問機制。

在 SWEVT(軟件調試事件)寄存器中指定對調試事件採取的調試操作。

12.2.3、MTCR和MFCR指令

當使用 MTCR(移動到核心寄存器)或 MFCR(從核心寄存器移動)指令讀取或修改用户核心特殊功能寄存器(CSFR)時,調試事件將被觸發。這使得調試軟件能夠監控、檢測和修改 CSFR 的變化。對 F000H 至 FDFFH 範圍內的寄存器執行 MTCR 或 MFCR 時,不會引發調試事件。該範圍包含所有專用調試 SFR(特殊功能寄存器):

T就是To

F就是From

注意到了把,一般核心功能寄存器是16bit的,之前章節是有過描述的。

- 調試狀態寄存器(“DBGSR”)。

- 核心寄存器訪問事件寄存器(“CREVT”)。

- 軟件調試事件寄存器(“SWEVT”)。

- 外部事件寄存器(“EXEVT”)。

- 觸發事件寄存器(TRnEVT)(“TRxEVT”)。

- 調試監控啓動寄存器(“DMS”)。

- 調試上下文指針寄存器(“DCX”)。

- 調試陷阱控制寄存器(“DBGTCR”)。

- 累積觸發信息寄存器(“TRIG_ACC”)。

附加計數器寄存器

- 計數器控制寄存器 - “計數器控制寄存器” .

- CPU 時鐘計數寄存器 - “CPU 時鐘週期計數寄存器”。

- 指令計數寄存器 - “指令計數寄存器”。

- 多計數寄存器 1 - “多計數寄存器 1” .

- 多計數寄存器 2 - “多計數寄存器 2” .

- 多路計數寄存器 3 - “多路計數寄存器 3”。

配置調試控制器或訪問性能計數器不會導致調試事件。

12.2.4、觸發事件單元

當一組可編程的調試觸發器處於活動狀態時,觸發事件單元負責生成調試事件。調試觸發器是:

•代碼地址。

•數據訪問。

備註:比較的地址為虛擬地址。

這些調試觸發器為可編程邏輯塊提供輸入,該邏輯塊產生調試事件作為輸出

調試事件觸發時的調試操作在觸發事件寄存器 (TRnEVT) 中指定。

12.3、調試觸發器

每個調試觸發器由一個觸發器地址寄存器 (TRnADR) 和一個關聯觸發器事件寄存器 (TRnEVT) 組成。調試觸發器地址對用於定義地址範圍。

核心調試控制器可生成以下類型的調試觸發器:

- 在特定地址執行指令。

- 在地址範圍內執行指令。

- 從特定地址加載數值

- 從地址範圍內加載數值。

- 將數值存儲到特定地址。

- 在地址範圍內存儲數值。

可用調試觸發器的數量取決於執行情況。

12.3.1、組合調試觸發器

對奇數和偶數觸發地址寄存器可以組合來定義地址範圍。將為該範圍內的地址生成一個觸發器。

•偶數地址寄存器<=地址<奇數地址寄存器

通過在一對寄存器的EVT觸發事件中設置RNG位,一對寄存器被定義為一個範圍對。

當設置偶數EVT觸發器的RNG位時,範圍的所有設置都從偶數EVT寄存器中獲取,而奇數EVT寄存器被忽略。

- 範圍 0 由 TR0ADR 和 TR1ADR 定義,由 TR0EVT.RNG 啓用

- 範圍 1 由 TR2ADR 和 TR3ADR 定義,由 TR2EVT.RNG 啓用

- 範圍 2 由 TR4ADR 和 TR5ADR 定義,由 TR4EVT.RNG 啓用

- 範圍 3 由 TR6ADR 和 TR7ADR 定義,由 TR6EVT.RNG 啓用

注意:“奇數”編號的觸發事件寄存器(TR1EVT, TR3EVT等)的RNG位總是保留的。

12.3.2、任務特定的調試觸發器

在某些情況下,可能希望僅在特定任務生成目標地址時才斷言調試觸發器。這是通過使用應用程序空間標識符(ASI)比較特性實現的。

如果在觸發事件寄存器(trnet)中設置了ASI_EN位,那麼只有當地址和trnet都匹配時才會斷言觸發器。ASI字段匹配當前任務ASI(在TASK_ASI寄存器中編程)。

12.3.3、累計調試觸發信息

為了進一步幫助調試,提供了TRIG_ACC寄存器。此寄存器包含自上次清除寄存器以來調試觸發器的累積狀態。無論觸發器何時被激活——無論它是否導致調試事件——它都會被記錄在TRIG_ACC寄存器中。(對於距離比較,只記錄較低的觸發激活)。

例如如果TRIG_ACC。設置了T[n],那麼TRIG_ACC寄存器最後一次被清除後,trigger-n被激活。TRIG_ACC寄存器是隻讀的,任何讀操作都會清除它,所有寫操作都會被忽略。

12.4、調試操作

當調試事件發生時,根據相關事件寄存器的編程,將執行以下一個或多個調試操作:

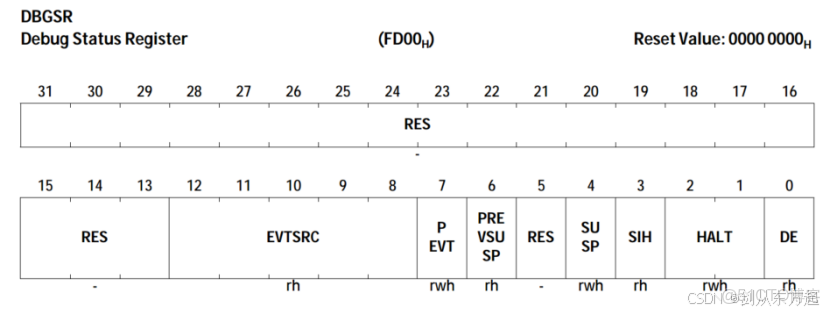

12.4.1、更新調試狀態寄存器(DBGSR)

當調試事件發生時,調試狀態寄存器(DBGSR)的EVTSRC(事件源),PEVT(發佈事件),PREVSUSP(掛起信號的前一狀態)和SUSP(掛起信號的當前狀態)字段總是更新。

PREVSUSP 字段根據 SUSP 字段的內容更新。

SUSP 根據提示調試事件(EXEVT、CREVT、SWEVT 或 TRnEVT)的寄存器 EVTA 字段更新。

12.4.2、顯示核心斷開信號

調試事件可以向OCDS指示事件已經發生。請注意,這取決於該信號是否連接到外部引腳的實現。

12.4.3、顯示核心暫停輸出信號

在 Core Suspend-Out 操作中,調試狀態寄存器 (DBGSR) 中 SUSP 字段的值被複制到 PREVSUSP 字段 (DBGSR.PREVSUSP)。

DBGSR.SUSP 字段將根據提示調試事件(EXEVT、CREVT、SWEVT 或 TRnEVT)的寄存器中的 SUSP 字段內容進行更新。

DBGSR.SUSP 位的修改將反映在核心掛起信號中。寫入 DBGSR.SUSP 位時,PREVSUSP 不會更新。

當調試事件導致發佈斷點中斷時,DBGSR.SUSP、DBGSR.PREVSUSP 和 Core Suspend-Out 信號保持不變。

12.4.4、停止

調試動作暫停,導致進入暫停模式。暫停模式執行取消:

- 如果設置了 BBM(Break Before Make),則包括引起斷點的指令在內的所有指令。

- 如果 BBM 清除,則在導致斷點的指令之後的所有指令。

一旦這些指令被取消,CPU 就會進入 “停止 ”模式,不再獲取或執行指令。當 DBGSR.HALT 位字段設置為 01 時,CPU 將進入停頓模式。進入 “停止 ”模式後,DBGSR.EVTSRC 位字段將被更新。

一旦進入Halt模式,外部調試系統就會通過將架構狀態映射到FPI地址空間來詢問目標。

在停止期間,CPU 不會響應任何中斷,只有在調試狀態寄存器 HALT 位(DBGSR.HALT)被清除後才會恢復執行。向 HALT 字段寫入 10B 可清除該位。

也可以通過寫入 DBGSTR.HALT 字段來輸入停止。這將被視為外部事件,並相應地更新 DBGSTR 字段。

復位後,DBGSTR.HALT 字段將被清除,CPU 將恢復正常運行。

12.4.5、斷點陷阱

斷點陷阱在不使用任何用户資源的情況下進入調試監視器。它依賴於以下模擬器資源:

- 調試監控器從 DMS(調試監控器起始地址)寄存器中定義的地址開始執行。

- 在 DCX(調試上下文保存區域指針)寄存器中定義的地址處有一個 4 字的 RAM 區域。該區域用於存儲調試監控器進入序列期間的臨界狀態。

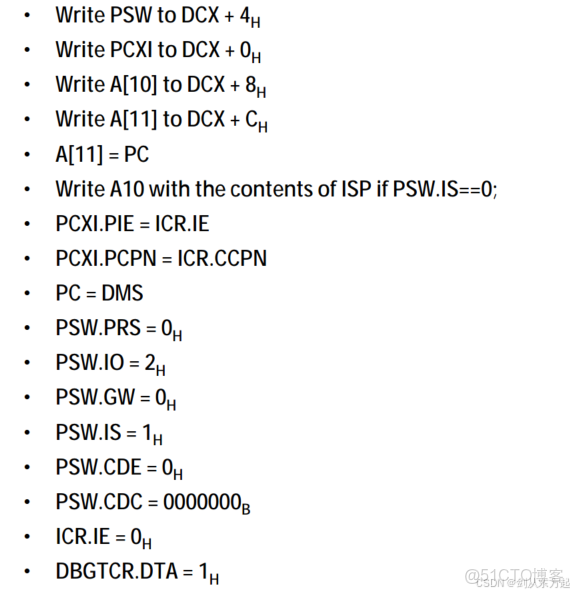

當發生斷點陷阱時,將執行以下操作:

相應的返回序列通過特權指令 RFM(從監控器返回)提供。這提供了進入調試監控器的自動路徑,不佔用任何用户資源。然後使用 RFM(從監控器返回)指令將控制權返回到原始任務。當不在調試模式(即 DBGSR.DE == 0)時,RFM 指令是一個 NOP(無操作)指令。

注意:在任何由陷阱或中斷引起的CSA訪問的負載或存儲地址上產生斷點陷阱是被抑制的。

模擬器空間

為了使調試監視器能夠在不需要修改當前內存保護設置的情況下運行,在調試模式下應用以下保護修改:

- 在調試模式下,包含 DMS 指針(基地址 == {DMS[31:24],24'h000000})的 16 MB 字節區域將禁用用於指令獲取的 MPX 陷阱。

- 在調試模式下,包含 DCX 指針(基地址 == {DCX[31:24],24'h000000})的 16 MB 字節區域將禁用 MPR 和 MPW 陷阱以進行加載和存儲操作。

這兩個內存區域被稱為仿真器空間。通過設置 SYSCON 寄存器(SYSCON.ESDIS)中的仿真器空間禁用位,可以無條件禁用這一功能。

仿真器空間的緩存能力取決於 PMA 寄存器為其所在段分配的內存屬性。

多個斷點陷阱

在執行斷點陷阱時,TriCore 會在 DCX 寄存器指示的位置保存調試上下文(PCX、PSW、A10、A11)。在調試陷阱處理程序結束時,使用 RFM 指令恢復該狀態。

DCX 位置只能存儲一個調試上下文。因此,如果觸發多個斷點陷阱,就會出現問題。只有最後一個斷點陷阱保存的狀態會被保留,之前所有斷點陷阱的狀態都會丟失。

為防止出現這種情況,斷點陷阱進入序列會設置調試陷阱控制寄存器 (DBGTCR) 中的調試陷阱激活 (DTA) 位。該位用於抑制進一步的斷點陷阱。

RFM 指令清零 DTA 位,斷點陷阱設置 DTA 位(也可通過 MTCR 設置和清零)。斷點陷阱只能在 DTA==0 的條件下觸發。因此,在斷點陷阱處理程序清除 DTA 位之前,或在斷點陷阱處理程序以 RFM 結束之前,其他斷點陷阱將被禁用。

應用復位後,DTA位被置為1。因此,在出現調試陷阱之前,必須清除寄存器。

12.4.6、斷點中斷

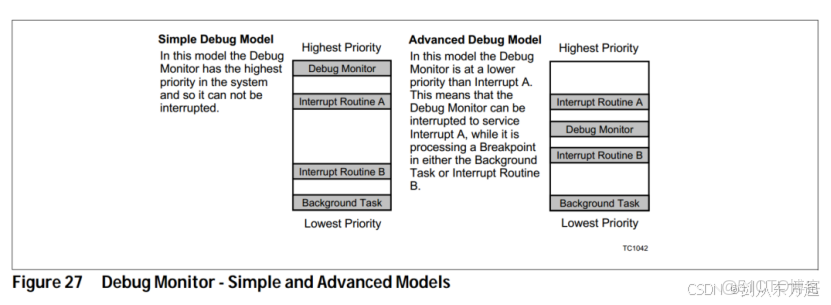

在調試事件上可能採取的調試動作之一是引發斷點中斷。中斷優先級是可編程的,並在與斷點中斷相關的控制寄存器中定義。

該體系結構允許調試事件引發四個斷點中斷中的一個,每個斷點中斷都可以有自己的中斷優先級。斷點中斷的數量取決於實現。

斷點中斷允許定義一個靈活的調試環境,它能夠滿足實時系統高效調試的許多要求。例如,在調試器處於活動狀態時,可以保留安全關鍵代碼的執行。

斷點中斷可用於提供傳統微控制器中可用的常規調試模型,其中斷點通過簡單地將最高中斷優先級分配給調試監視器或通過確保在調試監視器中禁用中斷來停止處理器。它還為關鍵中斷提供了靈活性,使其具有比Debug Monitor更高的優先級。這樣做的好處是:

- 調試監控器可以以與任何其他中斷相同的方式被更高級別的中斷中斷。這樣,CPU 就能在調試監控器運行時為關鍵中斷提供服務。

- 在關鍵例程中發佈的任何調試事件都會被推遲,直到 CPU 的優先級降到調試監控器的優先級以下。

已發佈斷點中斷

需要考慮的情況是,針對 CPU 的斷點中斷的優先級低於當前 CPU 的優先級。例如,在上圖中的高級模式中,如果在中斷例程 “A ”中設置了斷點中斷,就會出現問題,因為調試監控程序的優先級低於當前任務的優先級。

在與斷點相關聯的中斷級別上發佈軟件中斷就表明了這種情況。因此,當 CPU 中斷優先級低於調試監控器的優先級時,將進入調試監控例程。為了向監控例程表明斷點被推遲,當軟件中斷被髮布時,調試狀態寄存器中的發佈事件位(PEVT)將被置位。斷點中斷處理程序有責任檢查調試狀態寄存器中的該位,並在必要時清除該位。

注意:DBGSR。SUSP和DBGSR。當斷點中斷被髮布時,PREVSUSP不會更新。

1. DBGSR。無論是否發佈斷點中斷,EVTSRC總是更新的。

對其他目標的中斷

除了針對CPU之外,斷點中斷還可以針對系統中的其他核心。

12.4.7、暫停輸出

當調試事件發生時,掛起信號要麼被斷言,要麼被否定。掛出信號的先前狀態記錄在DBGSR.PREVSUSP中。

12.4.8、性能計數器啓動/停止

當性能計數器在任務模式下運行時,計數器通過調試操作啓動和停止。 所有事件寄存器都允許啓動或停止計數器。

觸發事件寄存器還允許將模式切換為激活(啓動)或非激活(停止)。這樣,在某些應用中就可以使用單個 RTE 來控制性能計數器。

12.4.9、None

沒有任何操作通過事件寄存器的EVTA字段實現,但是掛起信號、性能計數和DBGSR寄存器更新仍然像正常事件一樣發生。

12.4.10、Disabled

該事件被禁用並且不發生任何操作:掛起信號、性能計數器控制和DBGSR寄存器忽略該事件。

12.4.11、掛起暫停

當暫停輸入信號斷言時,只要調試功能啓用,就會始終進入停止模式。只要 Suspend In 信號被置信,CPU 就會一直處於停止模式。當暫停輸入信號為負時,CPU 將從停止狀態中釋放。

實現這一功能的目的是,在多核系統中,多個內核可以同時停止運行並從停止狀態釋放。

12.5、調試事件的優先級

可以同時激活多個觸發點。與流水線中最老指令相關的觸發點會優先處理。此外,與流水線中相同點相關的同時觸發點的優先級從高到低依次為

- 外部輸入(異步)。

- PC

上的可編程組觸發器 - 激活多個觸發器時,0 的優先級最高,7 的優先級最低。

- MTCR/MFCR 指令。

- 調試指令。

- 地址

上的可編程觸發器 - 激活多個觸發器時,0 的優先級最高,7 的優先級最低。

12.6、回調跟蹤

1. 設置基於 PSW 的調用深度計數器,以便在每次調用子程序時生成 CDO 陷阱。(PSW.CDC = 1111110B)

2. 啓用調用深度計數系統。(PSW.CDE = 1)

3. 當嘗試下一次調用時,將產生 CDO 陷阱,而不是子程序調用。

4. CDO 陷阱處理程序將執行所需的跟蹤功能。

5. CDO 陷阱處理程序清除內存中陷阱上下文的 PSW.CDE 位。

6. CDO 陷阱處理程序執行 “從異常返回”(RFE)。這就從內存中恢復了陷阱上下文,這次禁用了調用深度跟蹤。(PSW.CDE=0)。

7. 執行原始 CALL。由於調用深度跟蹤系統已禁用(PSW.CDE=0),子程序調用將成功。

- 每當 CALL 指令保存 PSW 時,CDE 位將被強制置 “1”。

- 子程序開始時,PSW.CDE 位的狀態為 “1”。

在調用跟蹤序列中,PSW.CDE 位是 “一次性 ”操作,在 CDO 陷阱清零後,在一次子程序調用中被禁用。

更多信息,請參閲本手冊指令集卷(第 2 卷)中的 CALL 指令。

12.7、調試控制寄存器

調試狀態寄存器(DBGSR)包含有關CPU核心中核心調試控制器硬件的當前狀態的信息:

•表示是否啓用調試的位。

•最後一個調試事件的來源。

調試事件的每個源都有一個相關的寄存器,該寄存器定義了在引發調試事件時要採取的調試操作。這些寄存器可能包含有關引發調試事件必須滿足的標準的額外信息,例如調試觸發器的組合。

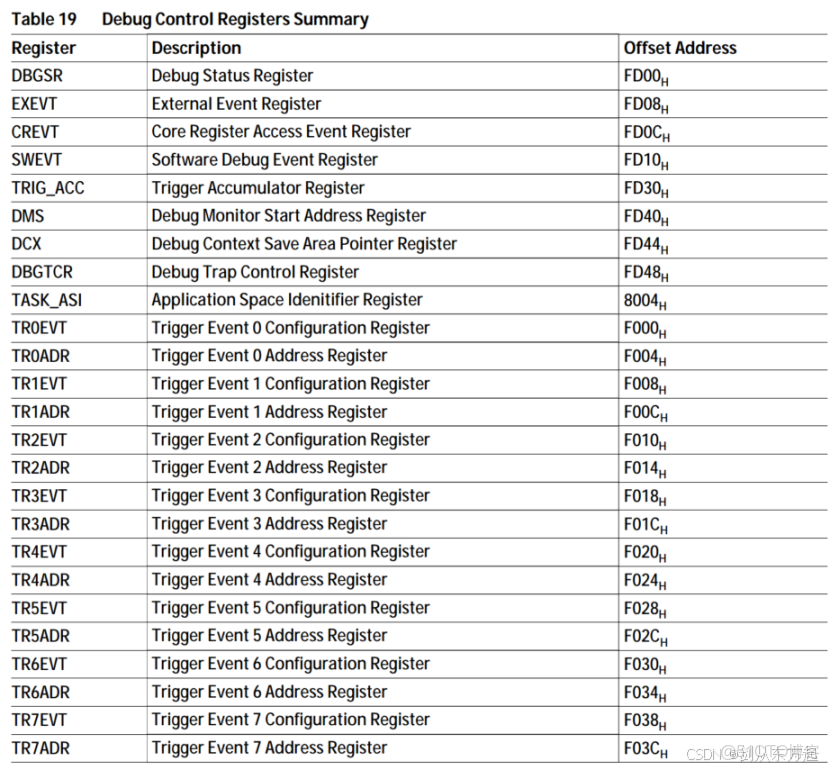

12.8、調試控制寄存器-摘要

12.9、調試控制寄存器

寄存器不再列舉了,太多了,詳細的查看手冊就好

12.10、核心績效衡量與分析

核心性能的實時度量為系統開發人員、架構師、編譯器開發人員、應用程序開發人員、操作系統開發人員等提供了有用的見解。

TriCore包括測量處理器不同性能方面的能力,而不會對其執行產生任何實時影響。對性能測量硬件進行了配置,以便只能同時進行性能測量的一個子集。

性能測量塊可用於測量基本參數,如:

- CPU 時鐘。

- 指令計數。

- 指令緩存命中/未命中

- 數據緩存命中/未命中(乾淨或不乾淨)。

可能測量的實際參數是特定於實現的。

性能計數器可以自由運行方式使用,以獲取綜合信息。此外,它們還可與調試事件邏輯結合使用,以控制單個任務的運行 “窗口”,例如動態啓動和停止計數器,以過濾某些所需事件的測量信息。

典型性能計數器使用

性能計數器由 CCTRL CSFR 寄存器控制。

通過向計數器使能寄存器 CCTRL.CE 位寫入適當的值,可以啓用或禁用性能計數器。

通常情況下,基線測量總是對兩個參數進行計數:

•時鐘計數。

•發出指令的數量。

之一:

- 指令緩存點擊數。

- 數據高速緩存點擊數。

之一:

- 指令緩存未命中。

- 數據緩存清除未命中。

另外:

- 數據緩存髒缺失(需要緩存回寫/剔除)。

注意:計數器只能在禁用(即不在 “計數模式 ”下)時寫入。在 “計數模式 ”下的任何寫入嘗試都不會有任何效果。

注:計數器啓用後即為自由運行遞增器,在達到最大值後將翻轉為零。

通過對計數器功能進行分組,可以對典型的測量結果進行分組,如數據高速緩存性能和指令高速緩存性能。

這些都可以根據時鐘週期和發出指令的背景統計數據進行測量。

計數器的啓動並不與任何流水線階段精確同步。例如,一旦啓用指令計數器計數,它就會開始計數從該時鐘週期開始的所有退行指令。同樣,指令緩存未命中計數器一旦啓動,就會從該時鐘週期開始計數所有指令緩存未命中。

有兩種啓用計數器的方法: 正常模式和任務模式 (CCTRL.CM)。正常模式(默認模式)或任務模式由 CCTRL.CM 配置:

- 正常模式 - 一旦啓用,計數器就開始計數,並一直計數到禁用為止。

- 任務模式 - 只有當處理器檢測到調試事件並啓動性能計數器時,計數器才會計數。

計數器的書寫

計數器可以在任何時候被讀取,但是它們只能在不主動計數時被寫入(即當它們被禁用時)。如果計數器被禁用,則不認為它們處於計數模式,因此可以寫入它們。

如果出現以下情況,則表示計數器處於計數模式:

- 選擇了 “正常 ”或 “任務 ”模式。

- 模式處於激活狀態(正常模式始終處於激活狀態)。

- 計數器使能 CE 位(在計數器控制寄存器 - CCTRL 中)已啓用。

計數器模式

計數器控制 CSFR 中的計數器模式 (CM) 位(即 CCTRL.CM)決定所有計數器的運行模式。

在正常運行模式下,如果 CCTRL 中的計數使能位被設置(CCTRL.CE),計數器會在各自的觸發器上遞增。在 “任務 ”模式下,調試單元提供了額外的門控功能,可根據某些特定條件(如單個任務)對性能計數器中收集的數據進行過濾。

計數器/粘性位的包裝

性能計數器會向用户提示計數器已纏繞(使用粘性位),這有助於判斷計數器是否在兩個測量值之間纏繞。

- 所有性能計數器都是 31 位計數器,可進行自由包絡操作。

- 每個計數器的第 31 位都是粘性位。當第 30:0 位纏繞時,該位被置位。在軟件寫入之前,該位一直處於置位狀態。

12.11、性能計數器寄存器

寄存器不再一一列舉,有興趣查看手冊