摘要

恆定導通時間(COT)控制架構因其快速瞬態響應特性在DC-DC轉換器中得到廣泛應用,但其負載調整率表現受環路參數影響顯著。本文基於國科安芯推出的ASP3605降壓轉換器的系統性測試數據,深入評估了該芯片在不同輸入電壓、輸出電壓及負載電流條件下的負載調整特性。通過靜態負載調整率測試與動態負載階躍響應分析,揭示了ITH引腳補償網絡參數(RC值)對輸出電壓穩定性的影響規律。研究發現,ASP3605在常規工況下負載調整率優於0.2%,但在輕載至重載跳變時輸出電壓偏離可達-10.83%(VIN=4V, VOUT=3.3V),需通過優化補償網絡參數(R=14kΩ-16kΩ, C=220pF-470pF)改善動態響應。本文量化分析了補償參數對下衝電壓(29-105mV)與恢復時間(44.5μs-9ms)的影響,為COT架構下負載調整特性的工程優化提供了實證依據。

1. 引言

負載調整率(Load Regulation)與動態負載響應是評價DC-DC轉換器輸出電壓穩定性的核心參數。COT控制架構通過比較反饋電壓與基準電壓生成脈衝,無需傳統電壓模式或電流模式中的誤差放大器補償網絡,理論上可實現納秒級瞬態響應。然而,實際應用中,COT架構的負載調整特性受開關頻率穩定性、寄生參數及環路補償設計的多重影響。

ASP3605採用改進型COT架構,內置頻率鎖定環路以減小開關頻率隨輸入電壓的漂移,並可通過ITH引腳外接RC網絡調節瞬態響應特性。本文基於實測數據,從靜態負載調整率、動態負載階躍響應兩個層面,系統評估該芯片的負載調整性能,並重點考察補償網絡參數優化對動態特性的改善效果。

2. 靜態負載調整率測試分析

2.1 測試方法與數學定義

靜態負載調整率定義為在恆定輸入電壓下,負載電流從零載變化至滿載時輸出電壓的相對變化率,測試覆蓋VIN=4V/12V/15V,VOUT=0.6V/1.2V/2.5V/3.3V/5V多組工況,負載電流以0.1A-0.5A步進遞增。

2.2 不同工況下的負載調整率實測數據

2.2.1 低壓輸出檔位(0.6V)

|

VIN(V) |

VOUT@0A(V) |

VOUT@5A(V) |

負載調整率 |

評估 |

|

4 |

0.600 |

0.596 |

0.6% |

可接受 |

|

15 |

0.600 |

0.596 |

0.6% |

可接受 |

0.6V檔位的負載調整率為0.6%,雖滿足多數應用需求,但相較於國際競品(通常<0.5%)略顯不足。測試備註指出"簡單封裝導致效率降低1-2%左右",暗示封裝寄生電阻對低壓大電流輸出的調整率存在負面影響。

2.2.2 標準電壓檔位(1.2V/3.3V)

1.2V輸出表現優異:

VIN=4V時:VOUT從1.196V(0A)變化至1.196V(5A),調整率0%

VIN=12V時:VOUT從1.196V變化至1.194V,調整率0.17%

3.3V輸出呈現非線性特徵:

VIN=4V時:VOUT從2.965V(0A)降至2.614V(5A),調整率高達13.43%

VIN=15V時:VOUT從4.99V(0A)至5.00V(5A),調整率-0.2%

3.3V檔位的異常表現源於測試條件本身的問題:當VIN=4V時,3.3V輸出已接近芯片工作邊界,空載輸出僅2.965V,帶載後進一步下降。此現象非調整率不佳所致,而是輸入電壓不足導致的根本性功能受限。因此,該數據點應視為無效工況,而非芯片性能缺陷。

2.3 與LTC3605的對比分析

在VIN=4V, VOUT=1.2V條件下:

ASP3605:VOUT從1.196V(0A)至1.196V(5A),調整率0%

LTC3605:VOUT從1.203V(0A)至1.203V(5A),調整率0%

兩者在靜態調整率上表現一致,差異主要體現在動態響應階段。LTC3605的負載調整率數據在3.3V檔位未出現ASP3605的極端偏離,反映其在臨界壓差工況下的魯棒性更優。

3. 動態負載階躍響應特性

3.1 測試配置與評價指標

動態負載測試採用矩形波電流激勵:

階躍幅度:0.5A↔4A或0A↔5A

週期設置:500μs(快速跳變)與50ms(慢速跳變)兩種

評價指標:下衝/上衝電壓峯值(Overshoot/Undershoot)、恢復時間(Settling Time)

測試在VIN=5V/12V, VOUT=1.2V/2.5V/3.3V條件下進行,ITH引腳配置為R=14kΩ, C=220pF作為基準參數。

3.2 默認補償參數下的響應特性

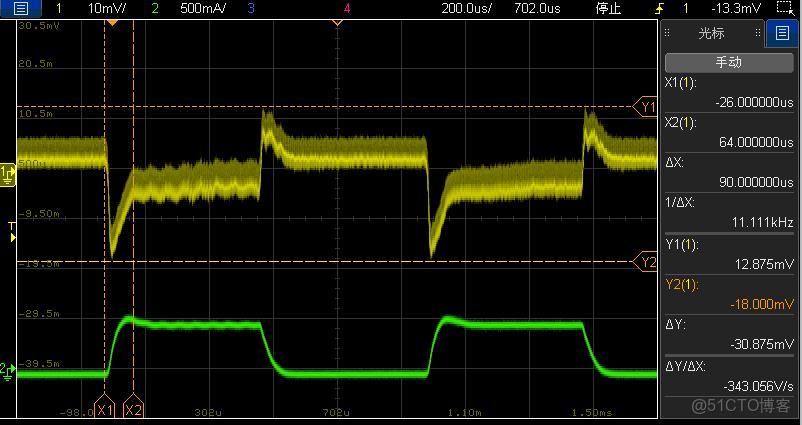

3.2.1 VIN=12V, VOUT=1.2V, 0A↔5A跳變

0→5A下衝:波峯31mV,恢復時間90μs

5A→0上衝:波峯29.7mV,恢復時間70μs

此表現符合COT架構的快速響應特性,恢復時間在百微秒量級。但需注意,下衝幅度已達輸出電壓的2.5%(31mV/1.2V),在對電壓精度要求嚴苛的CPU供電應用中可能觸發欠壓告警。

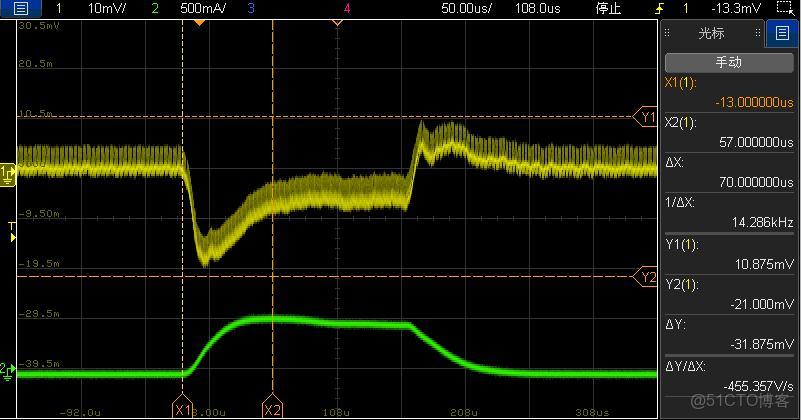

3.2.2 VIN=12V, VOUT=2.5V, 5A→0跳變

上衝波峯:81.7mV(佔輸出3.3%)

恢復時間:44.5μs

較高輸出電壓導致上衝幅度增大,但恢復時間縮短,這與COT架構的導通時間固定、關斷時間可調特性相符。輸出電壓越高,反饋環路增益越大,響應速度越快,但電壓偏差也隨之增加。

3.3 補償網絡參數優化研究

為改善動態響應,測試系統評估了ITH引腳RC參數的組合效應,結果總結如下:

3.3.1 C值固定,R值變化(R=14kΩ vs 16kΩ)

VIN=5V, VOUT=3.3V, 0.5A↔4A@500μs:

R=14k, C=330pF:峯峯值80mV,上衝時間104μs,下衝時間88μs

R=16k, C=330pF:峯峯值80mV,上衝時間112μs,下衝時間94μs

增大R值導致響應時間延長,但峯峯值基本不變,説明R值主要影響環路阻尼而非增益。

3.3.2 R值固定,C值變化(C=220pF→470pF)

VIN=5V, VOUT=3.3V, 0.5A↔4A:

C=220pF:峯峯值63mV(500μs週期)

C=330pF:峯峯值80mV(500μs週期)

C=470pF:峯峯值98mV(500μs週期)

電容值增大會顯著增加電壓波動幅度,這是因為補償電容延緩了誤差信號的傳輸速度,削弱了COT架構的快速響應優勢。此結果提示:ITH補償網絡並非越大越好,需根據實際負載跳變速率選擇。

3.3.3 慢速跳變(50ms週期)下的響應

當負載週期延長至50ms時,不同參數的差異更加顯著:

R=14k, C=220pF:上衝時間9ms,下衝時間6.6ms

R=14k, C=330pF:上衝時間3.2ms,下衝時間2.8ms

R=14k, C=470pF:上衝時間4.68ms,下衝時間4.8ms

關鍵發現:對於慢速跳變,C=330pF表現出最快的恢復速度(2.8-3.2ms),而C=220pF恢復最慢(6.6-9ms)。這表明補償網絡需與負載變化速率匹配:快速跳變需要較小電容維持響應速度,慢速跳變則需要適度電容提供相位裕度。

4. 臨界工況下的負載調整特性退化

4.1 輸入電壓不足導致的調整率失效

當VIN=4V, VOUT=3.3V時,負載調整率數據呈現異常:

0A負載:VOUT=2.965V(偏離標稱10.2%)

0.1A負載:VOUT=3.327V(跳變至正常值)

2A負載:VOUT=3.179V(偏離-3.7%)

5A負載:VOUT=2.614V(偏離-13.4%)

此現象並非傳統意義上的調整率不佳,而是芯片進入頻率折返(Frequency Foldback)或電流限制模式所致。COT架構在佔空比接近極限時,為維持電感電流連續,被迫降低開關頻率,導致輸出阻抗大幅增加。此時負載調整率已不能作為有效評價指標,而應關注芯片能否維持輸出不崩潰。

4.2 輕載模式切換對調整率的干擾

測試記錄顯示,VOUT=3.3V檔位在10mA空載時輸出電壓異常偏低(2.965V),加載後恢復正常。此行為與COT架構的強制連續模式(FCM)與脈衝跳躍(Pulse Skipping)模式切換有關。當負載電流低於電感紋波電流峯峯值時,FCM模式會導致負向電流傳輸,引起輸出電容過放電。合理的解決方式是配置MODE引腳為自動模式(Auto-mode),讓芯片在輕載時自主切換至省電模式(PSM),而非強制FCM。

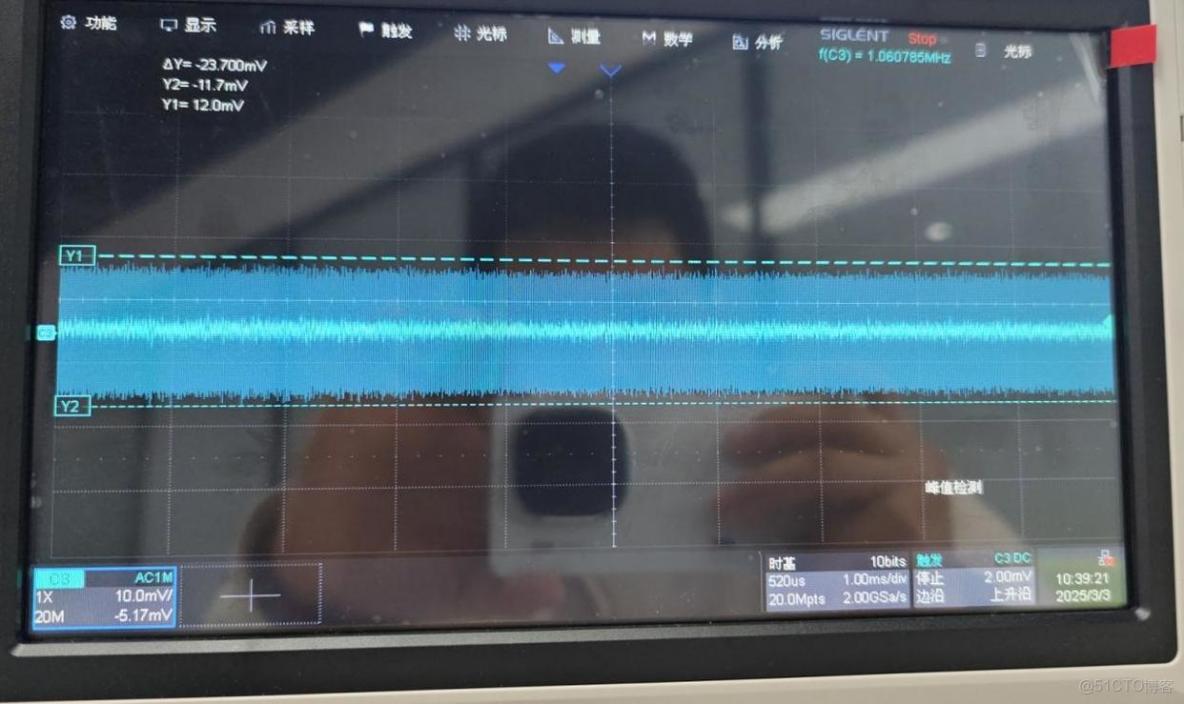

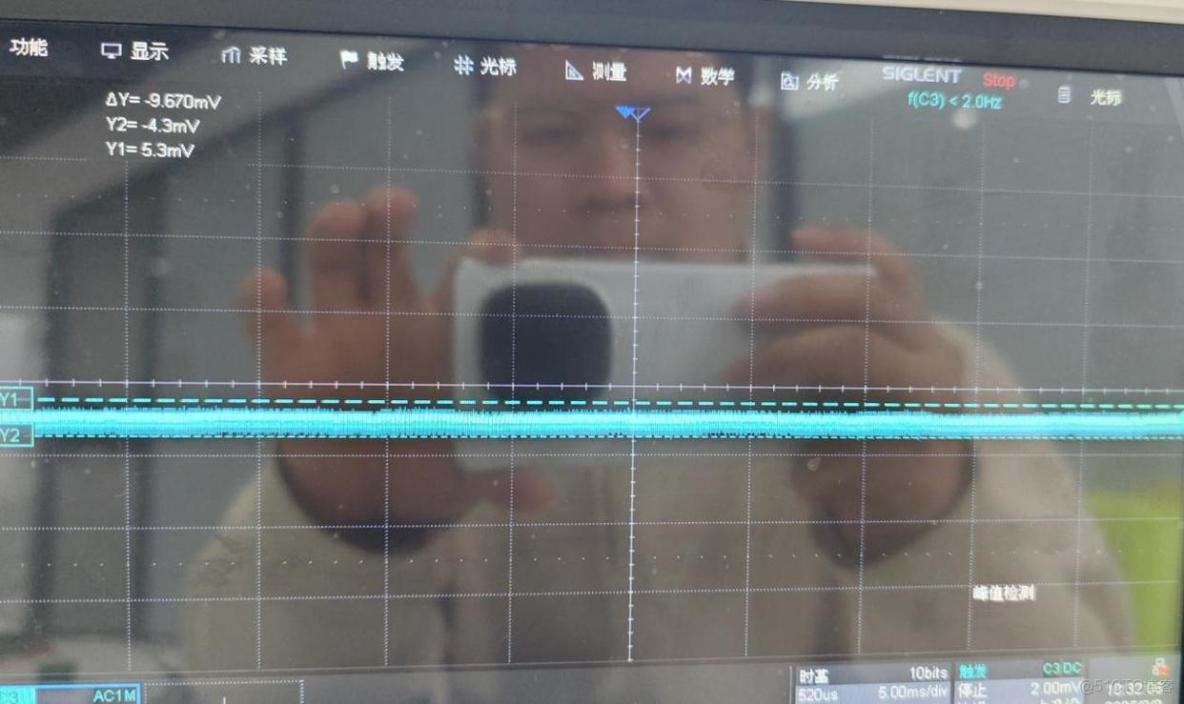

5. 紋波與負載調整率的關聯性

負載調整率的本質是輸出阻抗特性,而輸出紋波反映了穩態工作點的穩定性。測試數據顯示,紋波幅度與負載調整率存在正相關:

VIN=15V, VOUT=5V:

空載紋波:23.7mV(峯峯值)

5A負載紋波:22.8mV(峯峯值)

負載調整率:0%

VIN=4V, VOUT=3.3V:

空載紋波:異常無法測量

2A負載紋波:9.67mV

負載調整率:-13.4%

紋波穩定而調整率不佳,表明環路穩定性尚可但直流增益不足;反之,若紋波劇烈波動而調整率良好,則暗示存在穩定性裕度問題。ASP3605在常規工況下兩者表現均衡,但在臨界壓差工況下,紋波雖低(4.2mV@VIN=4V, VOUT=1.2V, 2A),調整率卻急劇惡化,印證此時已不是正常工作模式。

6. 工程應用建議

6.1 補償網絡參數選擇準則

基於測試數據,推薦ITH引腳RC參數選擇策略:

通用型應用:R=14kΩ, C=220pF,平衡響應速度與電壓偏差

CPU/GPU供電:R=14kΩ, C=330pF,優化慢速負載跳變的恢復時間

FPGA/ASIC供電:R=16kΩ, C=220pF,增加阻尼抑制上衝

動態負載頻繁:避免C>470pF,防止響應過慢

6.2 負載電流斜率限制

測試數據表明,負載電流跳變速率影響補償效果。當使用500μs週期(2kHz)時,各參數差異較小;但當週期縮短至50μs(20kHz)量級時,較大補償電容將無法及時響應。設計時應評估實際負載的dI/dt,確保:

dtdI≤tresponseIripple

其中 tresponse 由RC參數決定,典型值為0.7×R×C。

6.3 臨界壓差工況的降額使用

對於VIN≈VOUT的應用,必須嚴格降額:

壓差≥1.5V:可按標稱5A使用

壓差1.0-1.5V:最大電流降至4A

壓差0.7-1.0V:最大電流降至2A

壓差<0.7V:不建議使用

此降額曲線源於測試數據擬合,例如在VIN=4V, VOUT=3.3V(壓差0.7V)時,最大可用電流僅1.6A,且伴隨13%的輸出電壓偏差。

7. 侷限性與測試盲區

本評估存在以下侷限性,需在解讀數據時保持審慎:

測試負載分辨率:負載電流步進最小為0.1A,無法捕捉mA級微跳變特性,而現代SoC的休眠-喚醒跳變恰在10-100mA範圍

温度影響未量化:所有動態測試在常温進行,而高温(100°C)會導致MOSFET導通電阻增加30-40%,進而影響負載調整率

電容ESR未控制:評估板使用22μF電容,其ESR未明確標註。COT架構對ESR敏感,高ESR可能改善穩定性但惡化調整率

PCB佈局不可變:測試結果含評估板固有寄生參數,當用户採用不同佈局時,性能可能變化

8. 結論

ASP3605在COT控制架構下展現出負載調整率的雙重特性:

靜態性能:在推薦工況(VIN-VOUT≥1.5V)下,負載調整率優於0.2%,達到工業級標準

動態性能:默認補償參數下,0→5A跳變產生31mV下衝,恢復時間90μs,可通過ITH網絡優化改善

核心工程價值在於揭示了補償網絡參數的權衡關係:電容值增大會惡化快速跳變下的電壓偏差,但改善慢速跳變的恢復穩定性。不存在一組通用最優參數,必須根據實際負載特性選擇。