軟件版本:Quartus II 18.1 Standard Edition + ModelSim SE-64 10.1

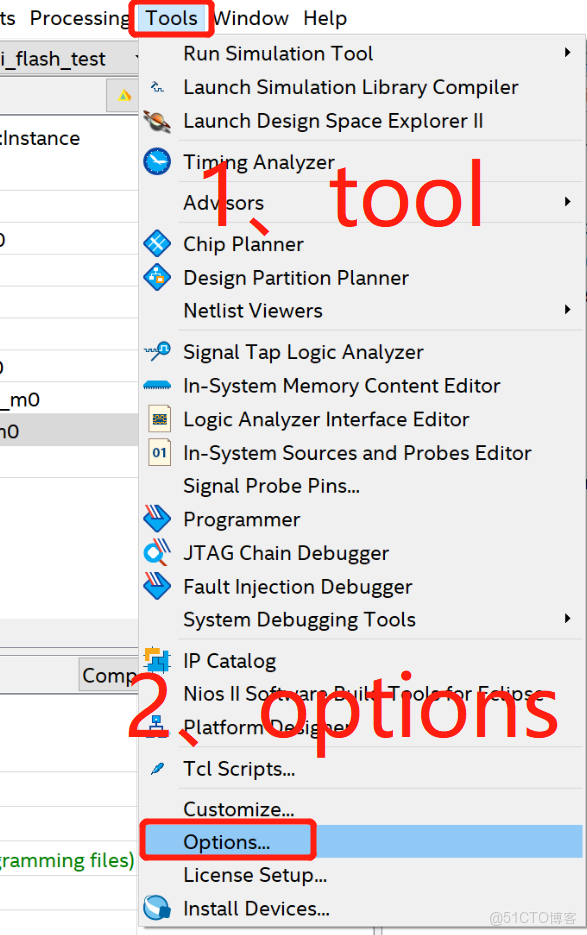

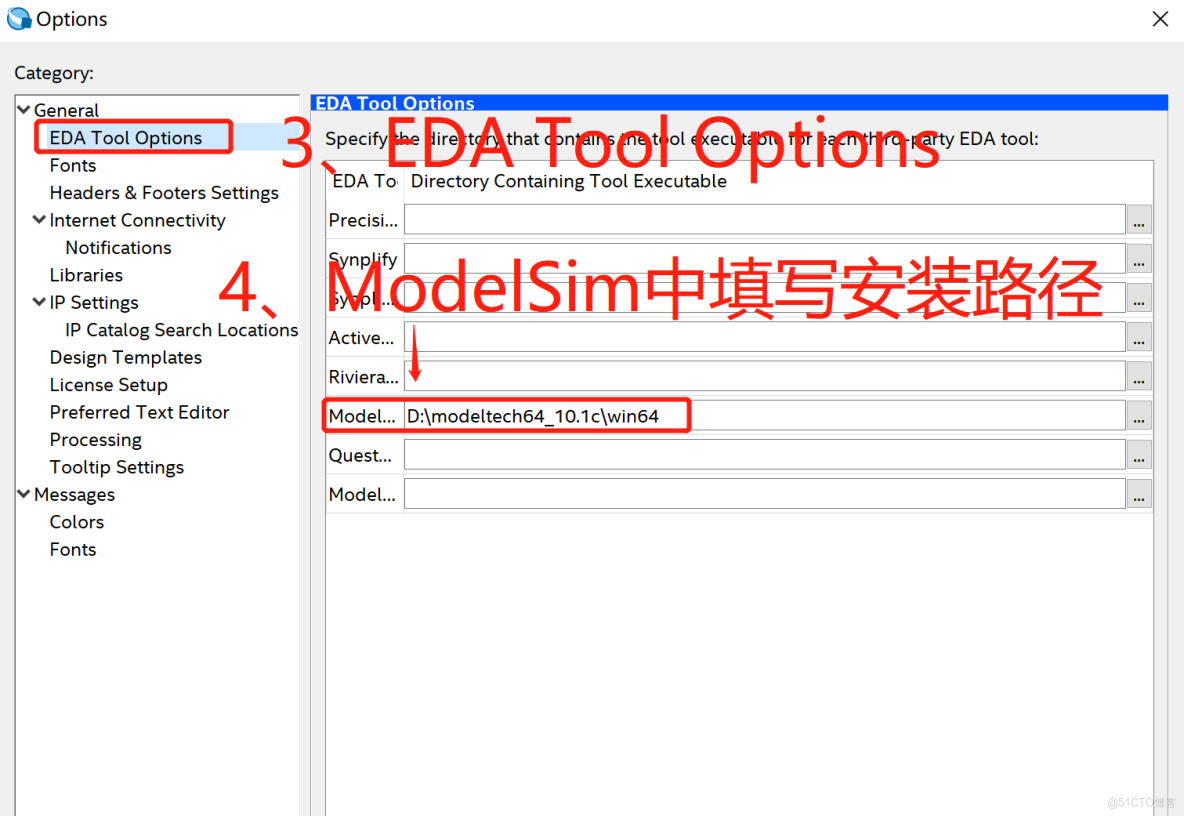

1、設置Quartus中各仿真軟件exe的安裝路徑

選擇tool—》options—》General—》EDA Tool Options,在ModelSim一欄填寫Modelsim的可執行程序的路徑,典型路徑為:安裝路徑\win64,例如:

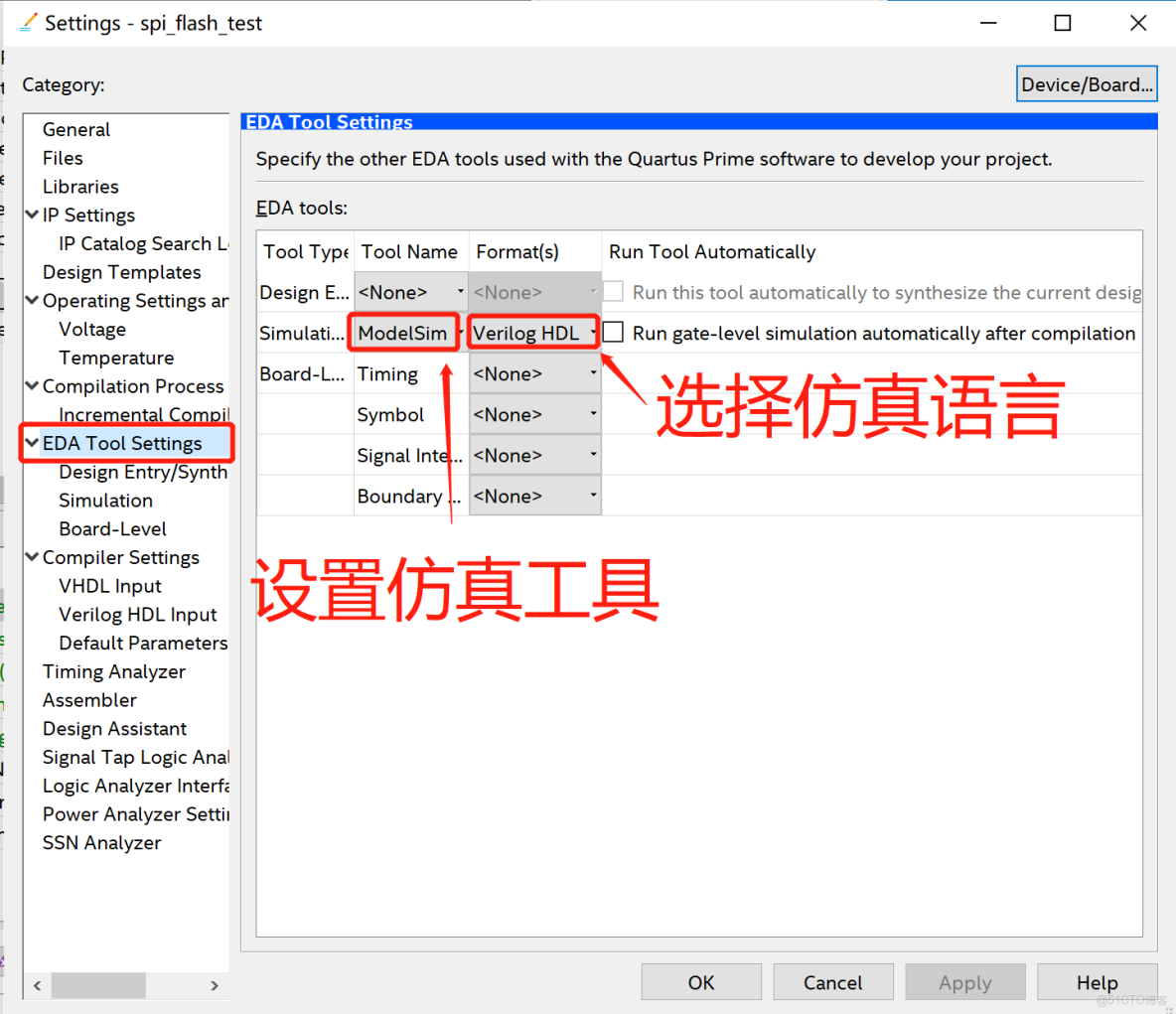

2、設置工程將要使用的仿真工具與編程語言(必須要在Start Testbench Template Writer前設置完成,否則不能自動生成.vt測試文件 )

點擊Assigments —》Settings—》EDA Tool Settings-Simulation,填寫仿真工具Modelsim與仿真語言。

3、創建測試文件

有兩種方式,分別是Quartus II自動生成測試文件(.vt)與自己手動創建測試文件(.vt或者.v)文件;

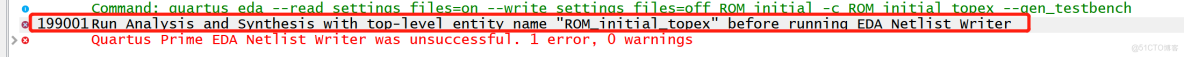

方式一:Quartus II自動生成測試文件(.VT文件,注意要先analysis&synthesis源文件後才能創建測試文件):

在自動生成測試文件之前,要先" Analysis and Synthesis (分析與綜合) "源文件後才能創建測試文件;不能是” Analysis and Elaboration(分析與闡釋) “,否則會報錯提示進行" Analysis and Synthesis (分析與綜合) ":

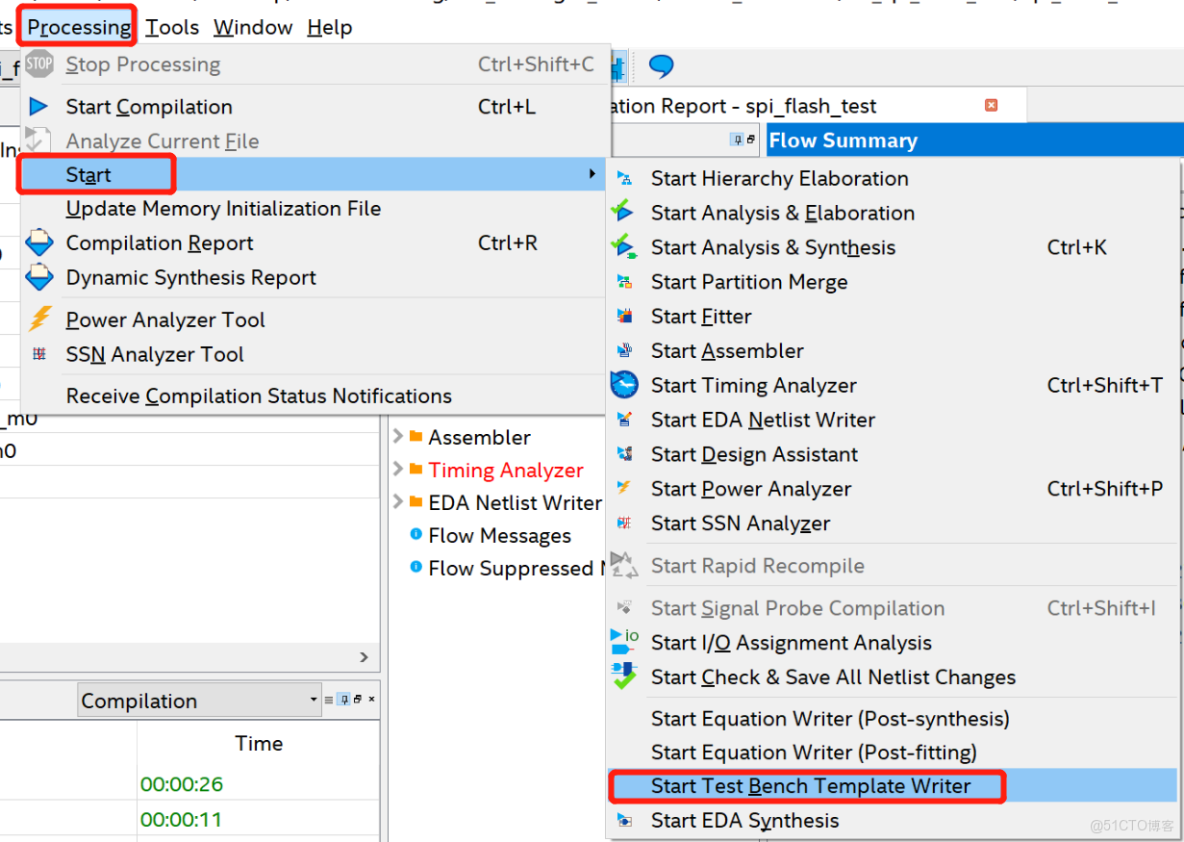

點擊Processing—》Start—》Start Testbench Template Writer,自動生成vt文件

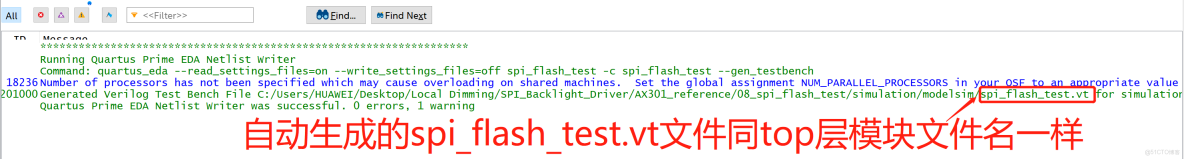

自動生成的測試文件名同top文件名相同,典型路徑為:[project_diretory]/simulation/modelsim/xxx.vt;

方式二:自己手動創建測試文件(.vt或者.v)文件;

在工程文件夾下創建一個sim文件夾,然後創建一個txt文本文件,接着修改文件文件名並修改後綴名為.v或者.vt即可

建議使用.v的測試文件,用notepad++打開後有多種顏色顯示,notepad++不支持.vt測試文件的多種顏色顯示。

4、編輯測試文件,生成激勵

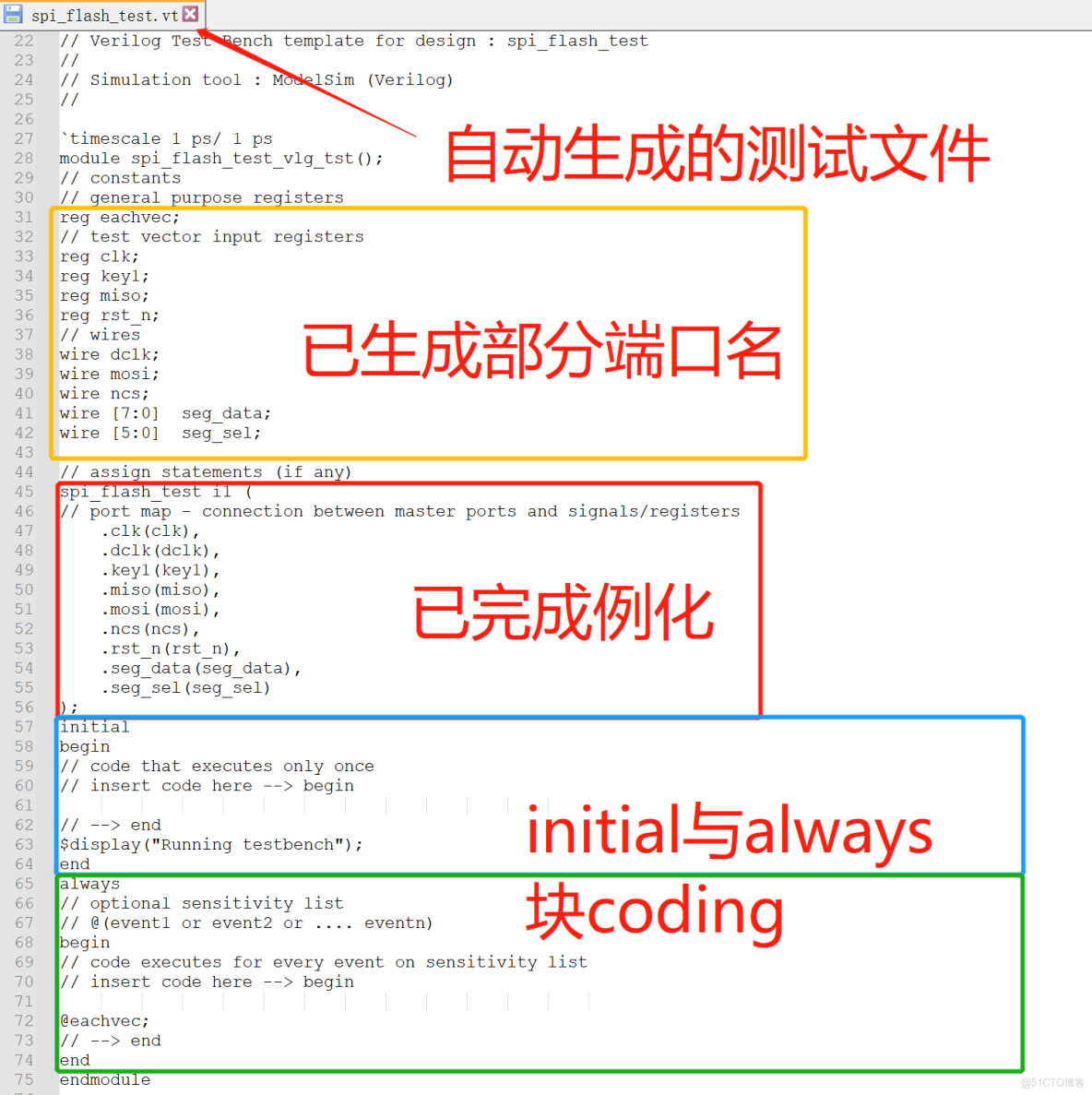

自動生成的xxx.vt文件完成了端口定義和實例化,但是需要設置激勵波形,即編寫initial語句與always調用塊;

具體方法通過文本編輯器來產生激勵波形。

ps:自己手動生成的.v測試文件需要自己手動編輯源代碼。

5、添加測試文件並設置仿真時長

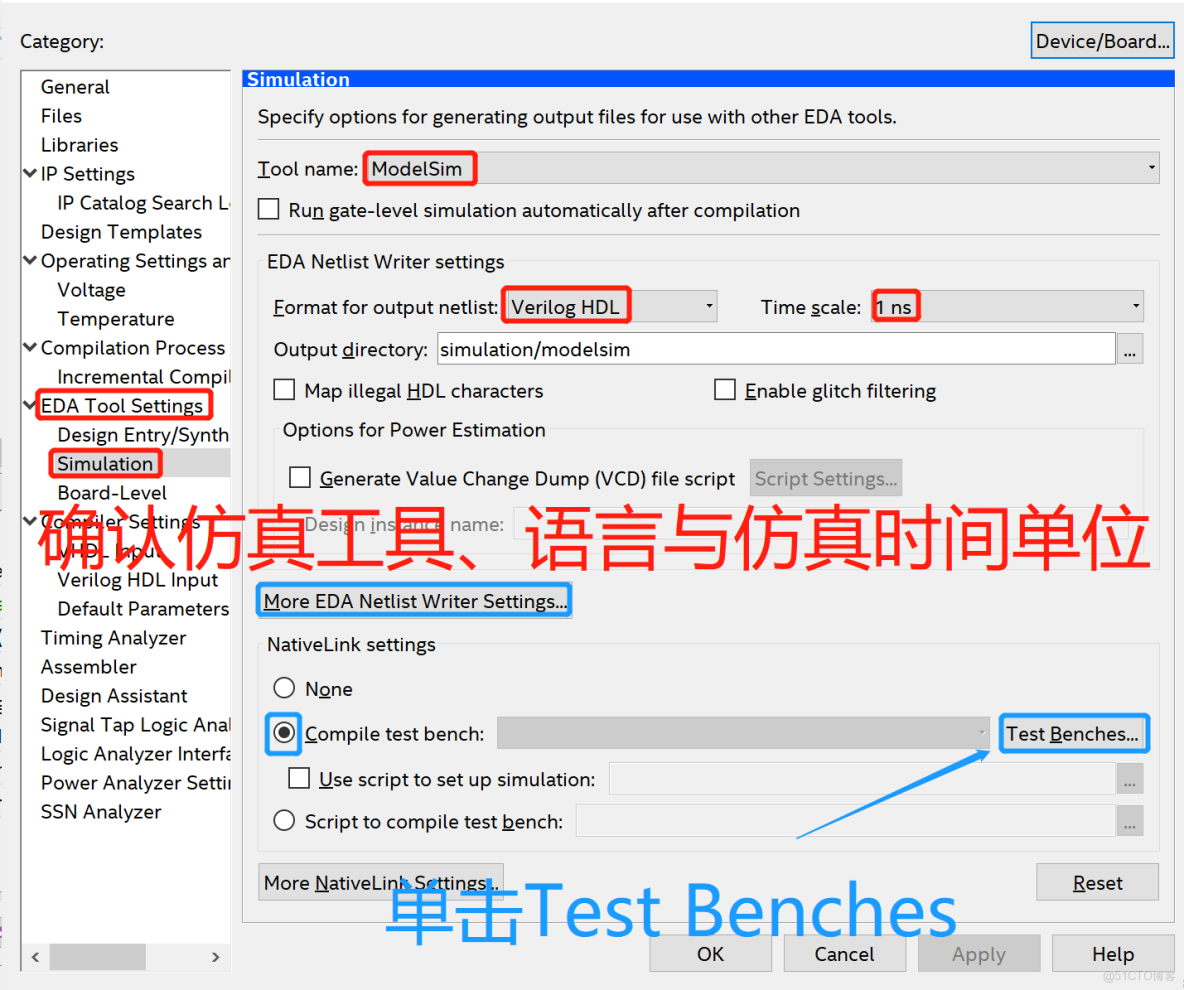

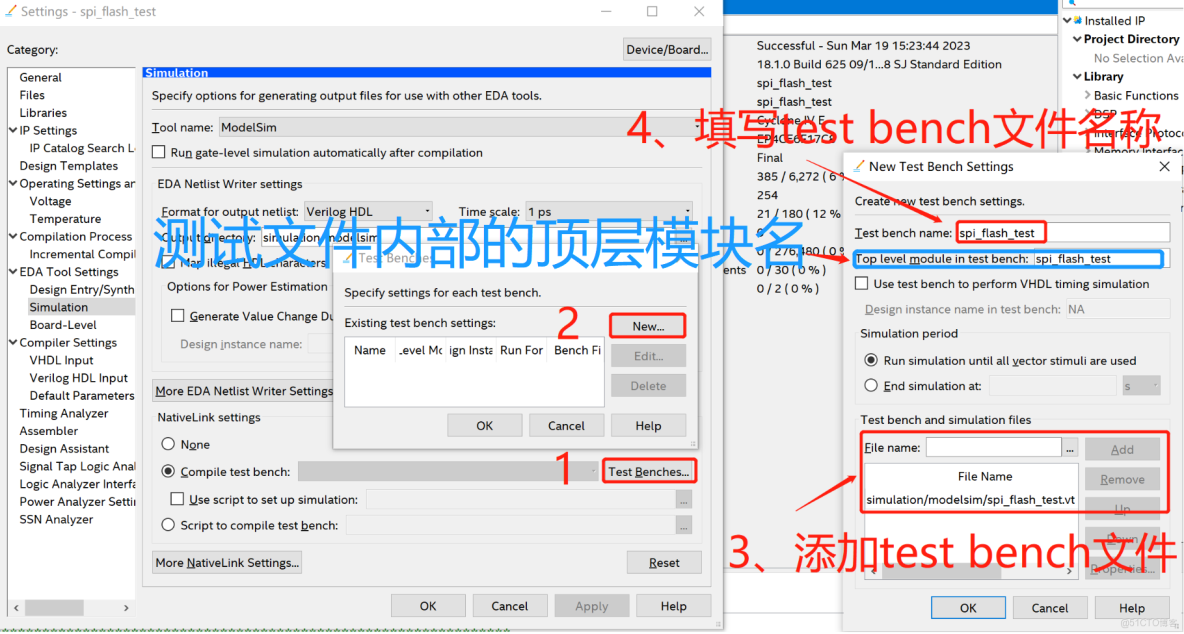

點擊Assigments —》Settings—》EDA Tool Settings-Simulation—》Simulation,確認仿真工具(Modelsim)、仿真語言(Verilog)與仿真時間單位(1ps或者1ns,默認1ps)

上圖選中的仿真時間單位/1ps(默認1ps的仿真時間精度)

添加test bench文件,其中top level module in test bench(測試文件內部的頂層模塊名,注意不是測試文件內部調用的其它模塊的名稱【特別針對只調用單個模塊的測試文件,容易錯填】)的文件名需要打開vt文件查看確認後填寫。

ps:.v測試文件的添加同.vt

番外:End simulation at,即是仿真停止時間(最好提前設置好,仿真時即可不用管,不設置會一直不停仿真直到你手動暫停仿真為止)。

6、啓動仿真

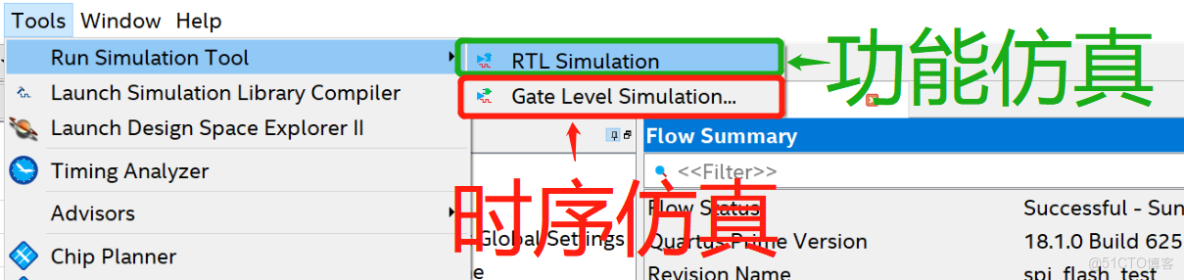

功能仿真:Tools—》Run Simulation Tool—》RTL Simulation

時序仿真:Tools—》Run Simulation—》Gate Level Simulation

自動彈出Modelsim頁面並進行仿真,自動展示仿真波形