- 前言

- Chapter 4: Real-time Processing Unit 實時處理單元

- 4.1 Introduction 介紹

- 4.2 Real-time Processing Unit Features RPU的特性

- 4.3 Cortex-R5F Processor Functional Description R5F處理器功能性介紹

- 4.3.1 RPU Pin Configuration

- 4.3.2 RPU CPU Configuration

- 4.4 Error Correction and Detection 錯誤糾正與識別

- 4.4.1 Interrupt Injection Mechanism

- 4.5 Level2 AXI Interfaces L2AXI接口

- 4.6 Memory Protection Unit 內存保護單元(MPU)

- 4.7 Events and Performance Monitor 事件與性能監視器

- 4.8 Power Management 功耗管理

- 4.9 Exception Vector Pointers 異常向量指針(EVP)

- 4.10 System Register Overview 系統寄存器一覽

- 4.11 Tightly Coupled Memory 緊密耦合內存(TCM)

- 4.11.1 Tightly Coupled Memory Address Map

- 本章小節

前言

上一章講了ug1085MPSOC技術參考手冊的第三章,講了有關MPSOC APU的相關內容,這次我們來講第四章,同樣也是MPSOC的核心器件之一的RPU,這部分內容較APU的話會簡單一點。這裏再次事先聲明,由於我對ARM架構完全不熟悉,所以我用了AI工具來理解這些內容,所以解釋可能有問題也歡迎指出。。

Chapter 4: Real-time Processing Unit 實時處理單元

4.1 Introduction 介紹

RPU也就是實時處理單元,聽名字就知道這個處理器是為了實時性的應用而生的,這一節稍微介紹了一下RPU實時性的來源,就是低延遲的中斷,這是通過中斷過程和重啓多指令加載的低延時實現的(我的理解是中斷響應低延時和加載中斷服務程序的低延時),此外專有外設端口以及TCM(緊密耦合內存)也提高了這種低延時性能。

4.2 Real-time Processing Unit Features RPU的特性

這節以列表的方式整理了一下RPU的特性,這裏也過一下,RPU具有以下的特性:

-

Integer unit implementing the Arm v7-R instruction set.

-

Single and double precision FPU with VFPv3 instructions.

-

Arm v7-R architecture memory protection unit (MPU).

-

64-bit master AXI3 interface for accessing memory and shared peripherals.(RPU訪問外部內存和共享外設的總線)

-

64-bit slave AXI3 interface for DMA access to the TCMs. (外部DMA方位RPU的TCM的總線)

-

Dynamic branch prediction with a global history buffer and a 4-entry return stack.

-

Separate 128KB TCM memory banks with ECC protection for each TCM.

-

32KB instruction and data L1 caches with ECC protection.

-

Independent Cortex-R5F processors or dual-redundant configuration.

-

32-bit master advanced eXtensible interface (AXI) peripheral interface on each processor for direct low-latency device memory type access to the interrupt controller.(訪問中斷控制器的低延時總線)

-

Debug APB interface to a CoreSight debug access port (DAP).

-

Low interrupt latency and non-maskable fast interrupts.

-

Performance monitoring unit.

-

Exception handling and memory protection.

-

ECC detection/correction on level-1 memories.

-

Lock-step (redundant CPU) configuration is available to mitigate random faults in CPU registers and gates.(鎖步運行模式以減少隨機錯誤)

-

Built-in self-test (BIST) to detect random faults in hardware (probably) caused by permanent failure.

-

Watchdog to detect both systematic and random failures causing program flow errors.

下面我們就跟隨文檔介紹下其中的一些特性。

4.3 Cortex-R5F Processor Functional Description R5F處理器功能性介紹

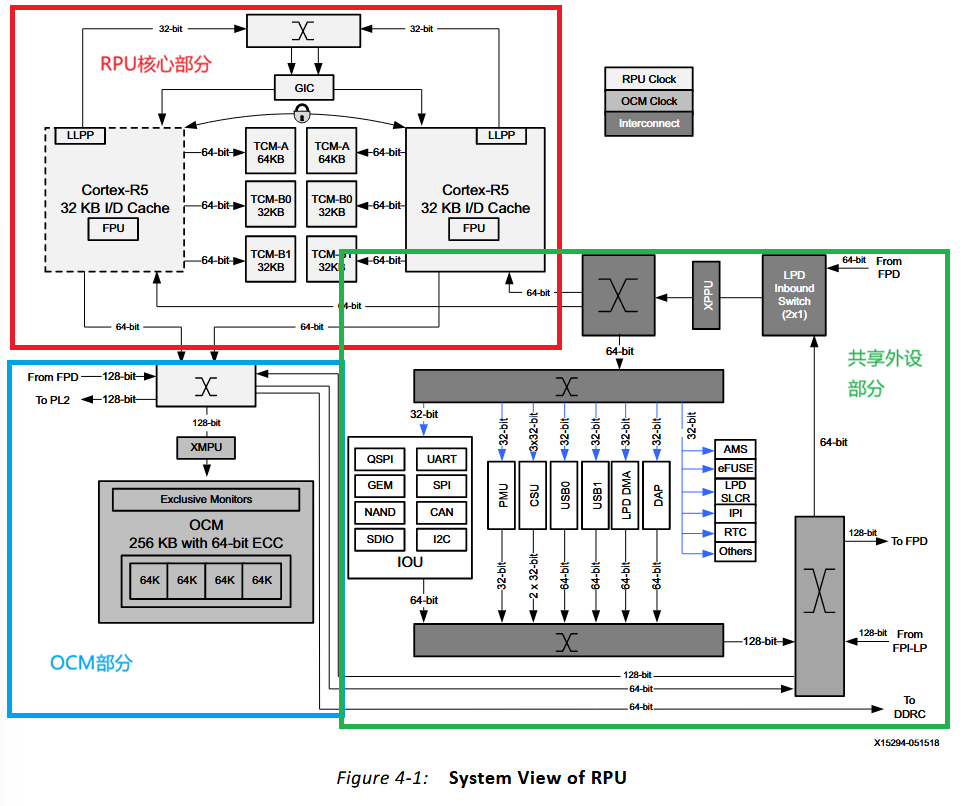

這節講了R5F處理器的一些功能特性,但是最主要的還是給出了R5F的系統架構圖,我們先來看看R5F的系統架構圖:

這張圖整體向我們展示了R5F處理器的連接結構,我在其中標出了三部分,我本來是想對照MPSOC互聯架構圖來確認一下各個部件,但是最後發現有很多地方沒辦法對應上,就只能作罷,不過我們還是分析一下。

最上面的RPU部分,就是R5F核的核心,可以看到兩核的R5F是直接與TCM相連的,TCM分為3塊,一塊64KB的TCMA,兩塊32KB的TCMB,並且都通過64位的AXI總線連接,設計出這麼三塊是有原因的,他們存儲的東西不同,主要是為了提高RPU的實時特性。還可以看到GIC(中斷控制器)與RPU也是緊密連接的,同樣也是為了中斷實時性的考慮。

另外兩部分OCM核共享外設我們放在一起講,首先是OCM部分有一個總線交換器或者説是路由器,這個路由器連接到RPU的64位AXI總線上,RPU就是通過該總線實現對外部設備的訪問,因此該路由器連接到OCM,FPD域路由器(右下角那個),再經過LPD域路由器和IOP Inbound(IO外設流入器,我根據AXI互聯總線圖猜的)實現連接各種各樣的共享外設。同時從LPD Inbound又連接了兩根64bit的AXI Slave總線用於方位RPU的TCM。這樣總體結構就算分析完了,我們在介紹下這節的其他東西。

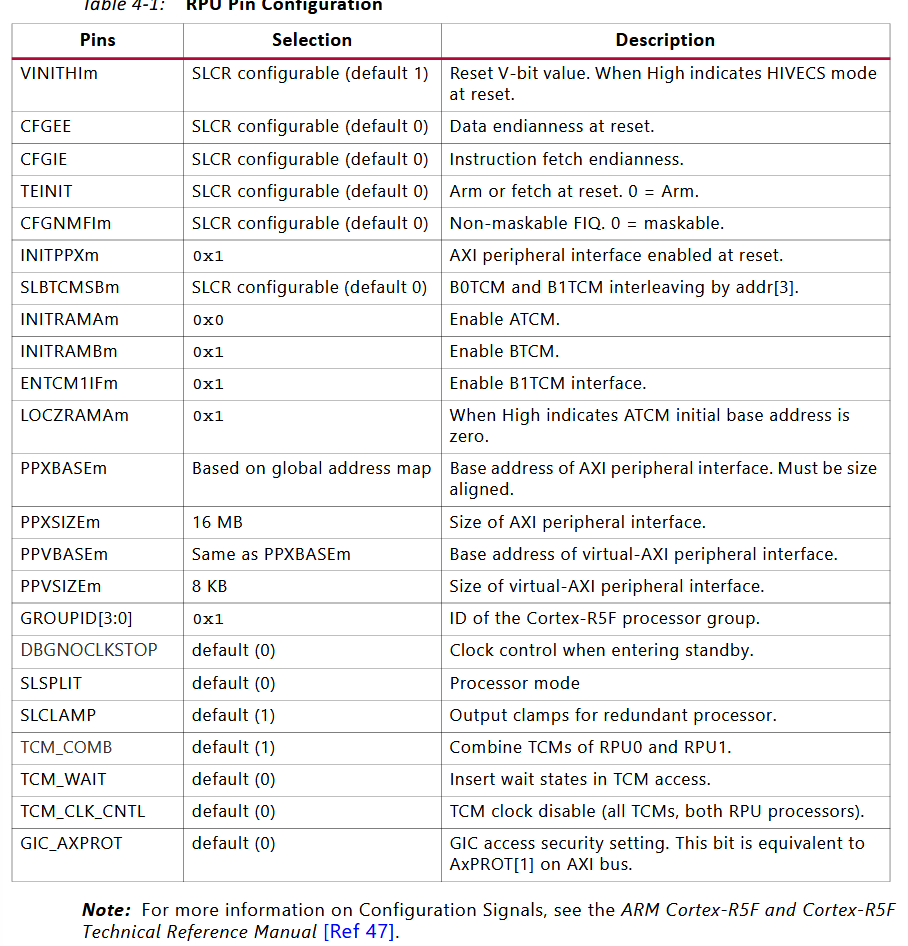

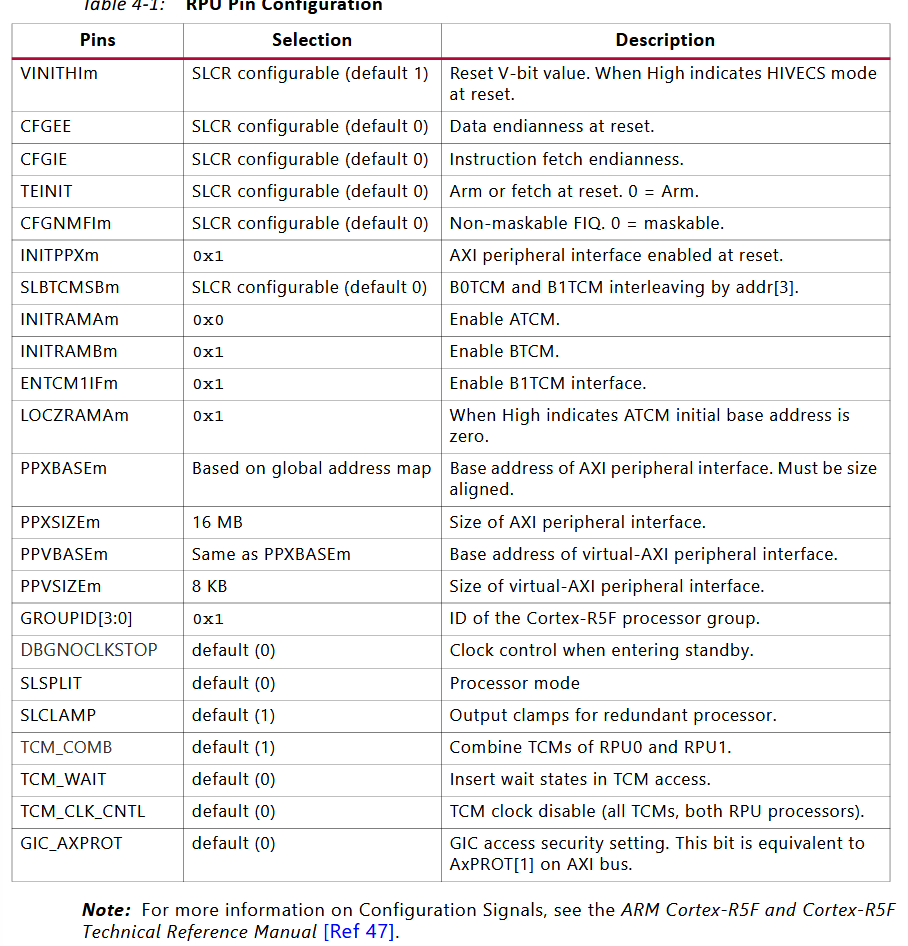

4.3.1 RPU Pin Configuration

這個小節列表描述了一下RPU的控制信號,感覺主要是硬件參考用,這裏也把表擺出來:

注意下面的提示,更多信息查看R5F的參考手冊,這裏不多講了。

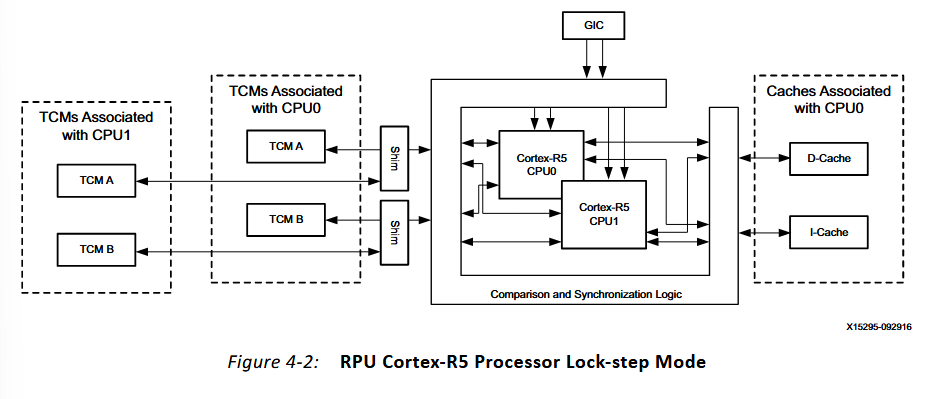

4.3.2 RPU CPU Configuration

這個小節要講R5F的一個比較重要的功能,Lock-Step鎖步模式,也稱為安全模式。像常規的我們分開使用R5F的兩個核心就是普通模式或者説性能模式,而Lock-Step鎖步模式直接解釋就是使兩個R5F核進行同樣的操作,驗證其輸出結果以確保結果的正確性或者安全性。鎖步模式有這些特性:

-

只有CPU0這一個處理器接口,也就是外部只能通過訪問CPU0的總線來訪問RPU,同樣RPU也只使用CPU0的總線來訪問外設。(這個是我理解的,原文只説only one set of CPU interfaces are used)

-

只使用CPU0的數據和指令緩存

-

中斷控制器只能將中斷分發到CPU0

-

兩個核心的TCMA核TCMB將會合並,形成128KB的TCMA和TCMB,合計256KB且地址連續

-

需要使用輸入信號SLCLAMP和SLSPLIT來控制處理器的組模式。

我們來看下鎖步模式的示意圖,可以和我總結的幾點特性對應一下:

4.4 Error Correction and Detection 錯誤糾正與識別

這節介紹了一下R5F支持的數據ECC機制。ECC我不太熟悉其應用原理,而且一般來説是處理器自動進行的,這裏的ECC應該是R5F能夠搭配TCM具有的額外ECC冗餘位來實現1bit糾錯和2bit檢測(我隱約記得數電課程好像講了這個東西的原理,但是我已經完全忘了哈哈)

4.4.1 Interrupt Injection Mechanism

中斷注入機制這節我有點沒看明白,主要是還沒有看到中斷的章節,不過我們這裏還是提一下,RPU支持使用自己的中斷控制器實現160個共享外設中斷,這些外設中斷由RPU_INTR_x寄存器標識並被RPU_INTR_MASK_x寄存器掩碼,這些寄存器每個32位一共有5個,組成了160個共享外設中斷,不過中斷具體是怎麼實現的這裏沒説,我們也以後再細講。

4.5 Level2 AXI Interfaces L2AXI接口

這節叫第二級AXI接口,我理解了下原文覺得他這裏想説的是第一級是RPU內部的接口,比如R5F核訪問TCM,中斷控制器以及I/D Cache這些接口叫一級接口,二級的像RPU訪問外設以及外部訪問RPU的TCM的叫二級接口。這節就講了這兩個概念,讓我有點奇怪他為什麼要設置這麼一節。

4.6 Memory Protection Unit 內存保護單元(MPU)

MPU單元有點類似我們講APU時候的MMU內存管理單元,但是我看了下MPU的功能似乎要簡單的多,他主要是用來管理對RPU的L1內存系統和外部內存的訪問,不包含像MMU一樣的地址轉譯功能。我這裏説一下MMU的工作原理。

MMU是通過將內存劃分為不同的區域,通過控制這些區域的訪問權限以實現對內存的包含,其最多可以劃分16個區域,每個區域可以有如下的設置:

-

區域起始地址

-

區域大小

-

子區域使能

-

區域屬性

-

區域訪問權限

-

區域使能

更詳細的介紹還是要參考R5F的技術參考手冊,這裏只帶過一下功能。

4.7 Events and Performance Monitor 事件與性能監視器

我沒看懂這節要講啥,這裏就翻譯一下:

處理器包括用於檢測可能發生的各種事件(例如高速緩存未命中)的邏輯。這些事件提供有關處理器行為的有用信息,供調試或分析代碼時使用。

事件在輸出事件總線上可見,並且可以使用性能監控單元中的寄存器進行計數。

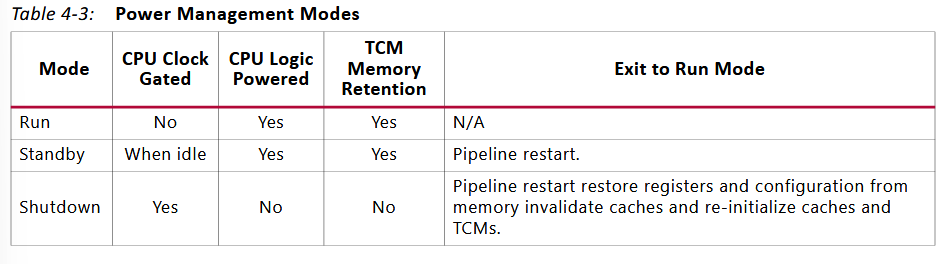

4.8 Power Management 功耗管理

功耗管理這部分RPU相比APU要簡單的多,就只有三狀態,運行,待機,關閉,一張表就解釋完了:

4.9 Exception Vector Pointers 異常向量指針(EVP)

異常向量指針EVP類似於中斷向量表IVT,裏面存儲的是異常服務程序的入口地址,這裏講EVP主要是由於EVP能夠根據R5F的SCTRL.V 位設置EVP的存放地址,SCTRL.V為0則EVP就放在0x0000_0000(LOVEC)的位置,為1就放在0xFFFF_0000(HIVEC)的位置上,我本來也不太明白為什麼要這麼設置,後面問了下通義千問也算有了個比較合理的解釋,我這裏説一下。

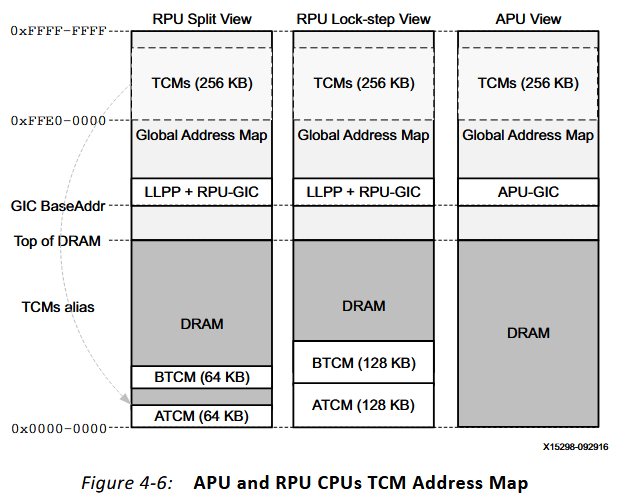

之所以要給EVP設置一個可切換的地址,是因為在上電時,啓動程序會在OCM上先執行,(因為SCU單元只會將FSBL程序加載到OCM上執行,具體的以後將boot過程細説)TCM此時是沒有數據的,為了RPU的正常工作,此時EVP是會被放在OCM的0xFFFF_0000處,而且在上電時默認EVP為HIVEC,而在執行FSBL時,RPU為了低延遲的響應中斷,EVP會被移動到LOVEC(這一移動應該是可選的,但是最好這麼做),這裏忘記提了,對於RPU來説TCM作為他內部的一塊RAM,實際上是被映射到從0x0000_0000開始的,然而對於APU或者説是全局地址,TCM則位於0xFFE0_0000的位置,這點我們後面會提到。

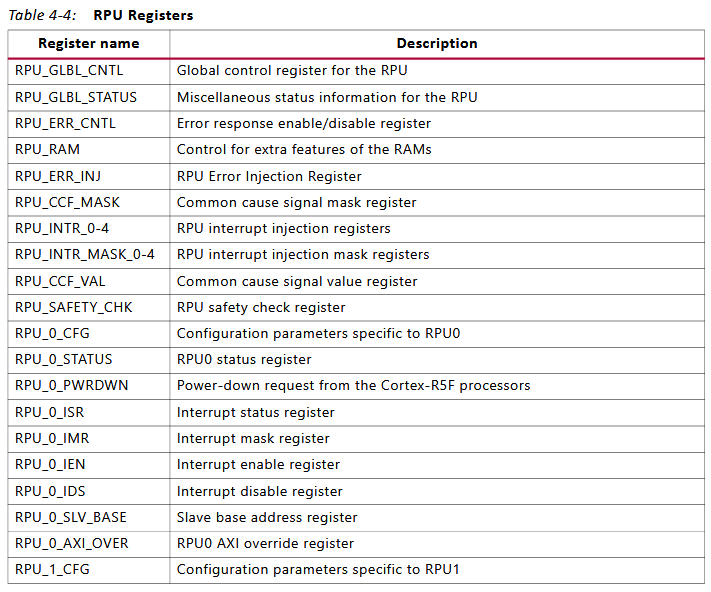

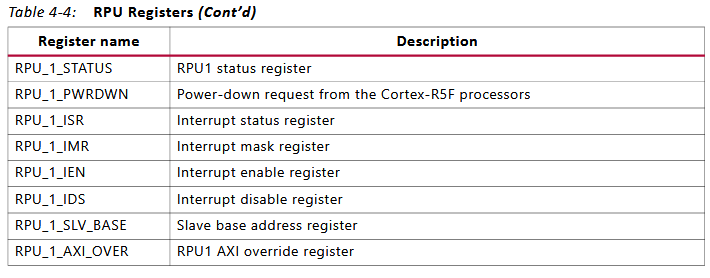

4.10 System Register Overview 系統寄存器一覽

這小節列表描述了一下RPU內部的一大堆寄存器,我也還是貼一下表,具體的看錶應該就有簡短解釋了:

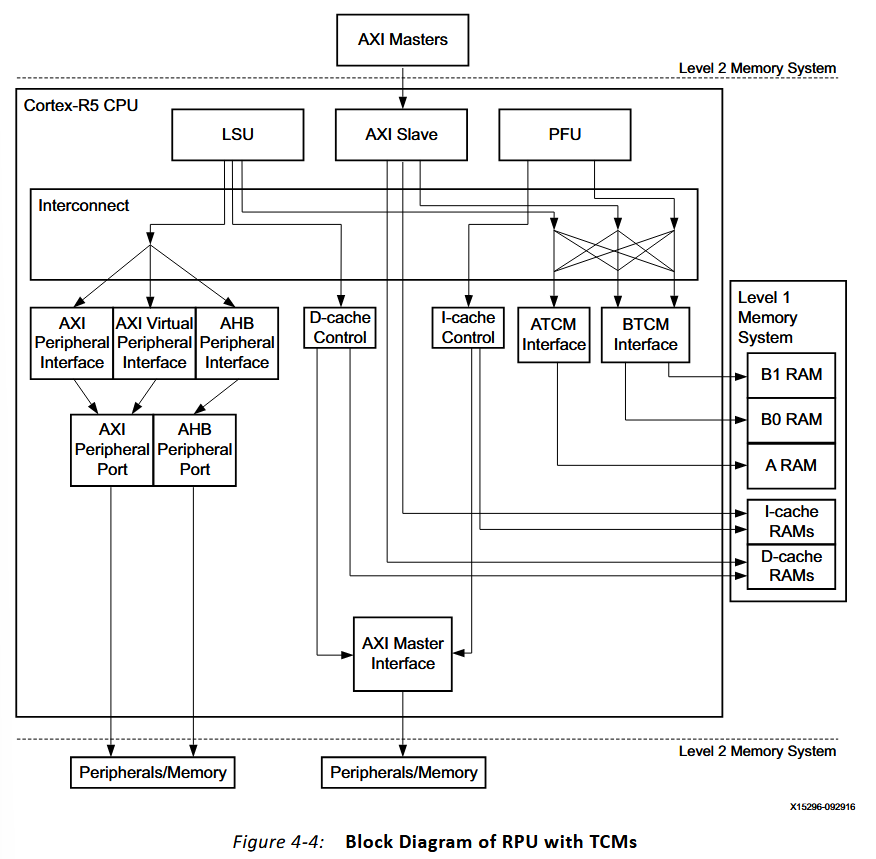

4.11 Tightly Coupled Memory 緊密耦合內存(TCM)

TCM緊密耦合內存 我們前面經常提到,這裏借用原文介紹一下:

緊耦合存儲器(TCM)是低延遲存儲器,可提供可預測的指令執行和可預測的數據加載/存儲時序。每個Cortex-R5F處理器在ATCM和BTCM端口上包含兩個64bit寬的64KB內存組,總共有128KB內存。將RAM分為兩個存儲體,並將它們放置在端口A和B上,允許加載-存儲、指令預取或AXI從端口同時訪問兩個存儲體。

BTCM存儲庫分為兩個32 KB的隊列,連接到Cortex-R5F處理器的BTCM-0和BTCM-1端口。有兩個TK接口,允許連接到緊耦合存儲器(ATCM和BTCM)的可配置存儲塊。

- ATCM通常保存必須高速訪問的中斷或異常代碼,而不會因緩存未命中而導致任何潛在延遲。

- BTCM通常保存用於密集處理的數據塊,例如音頻或視頻處理。

這裏就解釋了TCM為什麼要分塊的原因,還有一張圖來解釋他們的連接結構,但是這張圖裏的LSU和PFU單元我沒看懂是個啥,通篇也沒介紹,我也不多解釋了,具體的連接其實我我剛開始將RPU系統結構的時候比較類似,可以類比着看。

這裏後面還有一部分講鎖步模式和TCM的地址映射的,我看了下鎖步模式其實之前就講的差不多了這裏我們着重講一下TCM的地址映射。

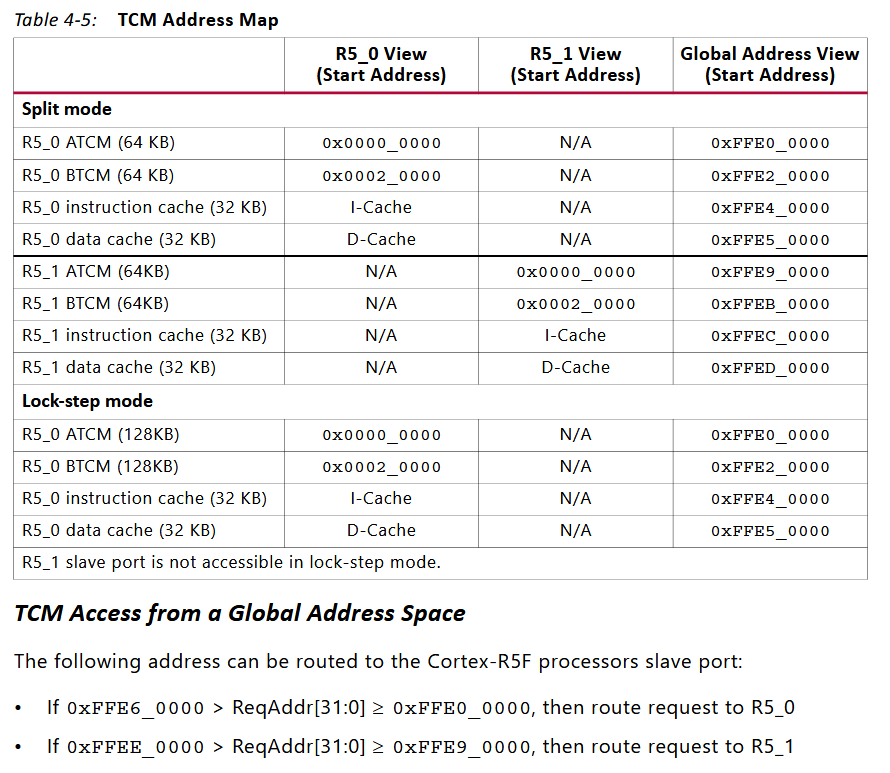

4.11.1 Tightly Coupled Memory Address Map

我們之前講過TCM由於RPU的使用以及EVP異常向量指針的存放的原因,需要對其進行地址映射,這一映射使得RPU能夠通過0x00地址直接訪問TCM,而外部可以通過全局地址訪問TCM,這一映射可以體現在下面的兩個表格中,一個是具體映射的地址,另一個是示意圖:

這裏我在第一個表中額外多截了幾句話,講的是R5_0的0xFFE6_00000xFFE0_0000和R5_1的0xFFEE_00000xFFE9_0000這些地址可以被連到R5F的從接口,也就是包括TCM和I/D Cache都是可以被外部訪問的。

最後這部分還有一點和GIC相關的內容,大致是説CCI可能會以R5_0的身份訪問內存,如果不把RPU加入可信賴的名單的話可能會由於安全設置導致錯誤,這裏就簡單翻譯一下了:

在某些情況下,CCI-400將使用與R5_0相同的主ID生成交易。如果該區域是一致的並受XMPU保護,則將生成錯誤,除非R5_0添加到XMPU的允許主ID列表中。如果R5_0對該區域的訪問與系統的安全或安全目標不兼容,則用户可以僅使用R5_1運行R5 F應用程序(不使用R5_0),或者跳過使用一致性並且不將R5_0添加到XMPU允許列表。

其實這節最後還有一點介紹使用匯編語言使能R5F處理器的鎖步模式的過程,但是都用上彙編了確實有點抽象,自從微機原理學完我都多久沒見過彙編了,這裏也就不在解釋了,有興趣可以去看第82頁。

本章小節

在寫完前一章的APU的內容後,寫這一章RPU的內容可以讓我感覺十分輕鬆了,大部分概念都不難且也並不複雜,總之我們下一章再見。