- 前言

- 專有名詞中英文對照表

- Chapter 6: Platform Management Unit 平台測量單元

- 6.3 Operation 操作

- 6.3.1 Power Down 斷電

- 6.3.2 Power Up 上電

- 6.3.3 APU Power Down APU斷電

- 6.3.3.1 Direct Power Down

- 6.3.3.2 Requested Power Down

- 6.3.4 APU Core Power Up APU核心上電

- 6.3.4 PMU Operation After a Wake-up

- 6.3.5 Wake-up Through MIO 使用MIO喚醒

- 6.3.6 Wake-up on USB 使用USB喚醒

- 6.3.7 Wake-up on Ethernet 使用以太網喚醒

- 6.3.8 Wake on Real-time Clock 使用實時時鐘喚醒

- 6.3.8 Wake through DAP 使用DAP喚醒

- 6.3.9 Direct Wake by the APU or Cortex-R5F

- 6.3.10 Wake through GIC Proxy 使用GIC代理喚醒

- 6.3.10 Deep-sleep Mode

- 6.3.11 Deep-sleep Mode Programming Model/Example

- 6.3.11.1 Power Down Procedure

- 6.3.11.2 Wake Procedure

- 6.3.12 Isolation Request 隔離請求

- 6.3.13 Reset Services 復位服務

- 6.3.14 Programming Model 編程模型

- 本章總結

- 6.3 Operation 操作

前言

上一篇筆記講了ug1085MPSOC技術參考手冊的第六章PMU的上半,也就是有關PMU內部結構的內容,這次我們來講第六章的下半,PMU的相關操作,主要是上電斷電和喚醒的PMU相關操作,由於我沒有實際進行操作過,在描述的時候可能會大量的貼原文檔的翻譯。同樣這裏再次事先聲明,由於我對PMU的理解還不夠,所以我用了AI工具來理解這些內容,所以解釋可能有問題也歡迎指出。。

專有名詞中英文對照表

| 英文 | 簡稱 | 中文翻譯 |

|---|---|---|

| platform measurement unit | (PMU) | 平台管理單元 |

| software test library | (STL) | 軟件測試庫 |

| configuration and security unit | (CSU) | 配置與安全單元 |

| Battery-backed RAM | (BBRAM) | 電池後備RAM |

| Real-time clock | (RTC) | 實時時鐘 |

| IO peripherals | (IOP) | IO外設 |

| Inter-Processor Interrupt | (IPI) | 處理器間中斷 |

| memory built-in self test | (MBIST) | 內存內置自測試 |

| Advanced Interrupt Bus | (AIB) | 先進中斷總線 |

| Triple Modular Redundancy | (TRM) | 三模冗餘 |

| power-on reset | (POR) | 上電覆位 |

| system reset | (SRST) | 系統復位 |

| built-in self-repair | (BISR) | 內建自修復 |

| programmable interval timers | (PITs) | 間隔可編程定時器 |

Chapter 6: Platform Management Unit 平台測量單元

6.3 Operation 操作

這一節主要是在描述PMU三種操作的流程,即PMU控制PS端各個模塊的上電(Power Up),斷電(Power Down)以及喚醒(Wake-up),還有一些和這些操作相關的特性。在第六章的上半提到過,PMU的核心功能之一就是控制PS各模塊的電源,這一節就是要講PMU是如何控制各模塊電源的(這裏其實主要介紹了APU和RPU的電源管理)。

在講子章節之前需要補一下其他的特性,在MPSOC中,被PMU進行電源管理的模塊主要可以分為兩類,電源主模塊和電源從模塊,其中電源主模塊可以對包括自身以及其他的電源從模塊進行上電斷電,例如APU和RPU,而電源從模塊只能被電源主模塊進行上斷電管理,例如USB,PL,GPU以及內存。這章節沒有介紹PMU管理其他模塊的電源估計是因為其只負責管理電源主模塊,電源從模塊似乎並不歸PMU管(但是PMU又可以管理LPD域)。

這裏還要解釋下用户的軟件與PMU進行交換的主要過程,用户編寫的軟件(這裏應該指的是在APU,RPU中執行的軟件,而不是PMU RAM中的軟件)通過與PMU_GLOBAL寄存器進行交互,也就是置位操作(例如置某個APU的斷電觸發寄存器為1),使得PMU處理器產生對應中斷,PMU處理器更加對應中斷並依據PMU ROM中的優先級進行中斷服務程序的執行,執行完後清除狀態標誌位。如果執行失敗,則PMU_GLOBAL.ERROR_STATUS寄存器會被斷言併產生錯誤事件,當然這些錯誤事件又回誘發PMU進行錯誤事件的處理操作(詳見第六章(上)PMU Error Handling and Propagation Logic的內容)。總而言之,用户程序和PMU的操作大部分是通過PMU_GLOBAL寄存器來進行的,PMU的處理器也同樣依賴PMU_GLOBAL寄存器進行中斷控制和操作。

6.3.1 Power Down 斷電

這小節簡要介紹了外部模塊如何通過PMU來斷電對應模塊的,具體做法是向REQ_PWRDWN_TRIG寄存器的對應位寫入1並且對應的REQ_PWRDWN_INT_MASK寄存器也為1,也就是不進行屏蔽,此時PMU處理器會被中斷然後檢查對應的中斷寄存器以確定是否有中斷(二次確認的原因應該是寄存器中斷是對應整個寄存器的變化,需要再次檢查以確定到底是哪個位),然後執行對應的中斷服務程序(ISR)。

6.3.2 Power Up 上電

這小節類似於上一小節,也是講外部通過PMU實施對某個模塊上電的過程,也還是通過對REQ_PWRUP_TRIG對應位寫1並且對應的REQ_PWRUP_INT_MASK寄存器也為1是進行中斷觸發,後面的內容不贅述了。

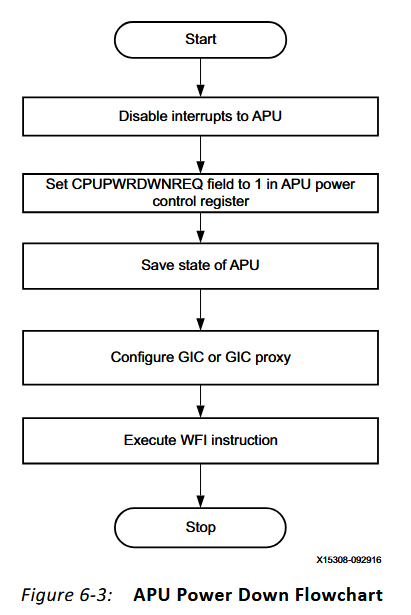

6.3.3 APU Power Down APU斷電

這小節講的是APU斷電的方法以及具體流程。APU斷電主要有兩者種方法,直接斷電和請求式斷電。

6.3.3.1 Direct Power Down

直接斷電和我們上面説到的寫寄存器式斷電的方式不太一樣,我這裏貼下源文檔並註釋一下以表明這個過程:

作為斷電準備,APU的準備過程必須有以下步驟:

- 禁用核心中斷。

- 通過將1寫入與該pu核心相對應的字段,在APU中的PWRCTL寄存器的CPUPWRDWNREQ字段中記錄關閉中央處理器的意圖。

- 保存APU核心的狀態

- 為喚醒源配置GIC或GIC代理(如果APU斷電後準備FPD斷電則配置GIC代理)。

- 執行等待中斷(WFI)指令

其實直接斷電的核心原理就是寫入CPUPWRDWNREQ為1以表示處理器準備斷電了,此時在讓處理器進入WFI的低功耗模式,則會直接讓處理器觸發發送到PMU GPI2的斷電請求,從而實現處理器的斷電,這裏還有一張流程圖,如下:

6.3.3.2 Requested Power Down

請求斷電模式就沒什麼好説的了,就如前面在6.3.1 Power Down裏面説的,向對應的斷電觸發寄存器寫1 就能夠正常實現請求式斷電。

6.3.4 APU Core Power Up APU核心上電

APU核心的上電主要由兩類器件控制,一類是其他CPU向PMU發送的上電請求,一類是與該核心相關聯的外設發出的中斷,具體的上電步驟如下:

- 為了為APU核心供電,請求設備必須設置REQ_PWRUP_TRIG全局寄存器中的特定位。

- 如果GIC的直接加電或喚醒已經對一個APU核心實施,則PMU將遵循PMU ROM代碼指定的步驟併為APU加電。直接加電是指由發往APU核心的中斷觸發的加電事件,而不是軟件通過寫入PMU_GLOBAL模塊中的請求寄存器來觸發事件

- 如果在通電完成後發生直接喚醒或GIC喚醒,則也會自動釋放對APU核心的復位。

- 如果加電請求是由另一個處理器發出的,則同一個處理器必須明確請求通過PMU重置請求寄存器釋放對APU核心的重置。

- 檢查是否將PMU_PWRUP_STATUS全局寄存器中的適當位位置設置為0,以指示上電請求由PMU提供服務

總結來説,對APU核心的喚醒也遵循最基礎的向全局寄存器寫入的操作,而且同樣有和APU直接斷電類似的直接上電操作,只是對於外設和其他寄存器而言,在上電後處理器核心的復位的釋放不同,對於外設的上電請求會直接釋放核心復位,而對於其他CPU的上電請求則會根據其他CPU的設置而釋放復位。

6.3.4 PMU Operation After a Wake-up

這節將PMU的wake-up操作,也就是將處理器從低功耗或者休眠模式中喚醒的操作,這節有點複雜,我自己也沒有完全看懂,這裏就説一下AI總結的內容。PMU總共有三種喚醒處理器的方式:

-

Fixed:直接喚醒處理器,例如處於斷電中的R5F處理器在接受外設或者定時器中斷後進行上電的請求,具體主要有兩步,第一,中斷被路由到PMU以觸發喚醒處理器的請求,第二,當處理器喚醒後,釋放其復位使其處理被掛起的中斷。

-

On-demand:在處理器進行休眠狀態前,規定在處理器被喚醒後需要同時打開的模塊,具體步驟如下:

- 軟件寫REQ_PWRUP_TRIG寄存器,請求喚醒後開啓某些電源域;同時在REQ_PWRUP_INT_DIS中屏蔽這些請求的中斷。這樣就能實現即時這些電源域已被要求上電,但在處理器被喚醒前這些電源域都不會被真正上電。

- 軟件發起正常睡眠請求。

- 系統被外部事件喚醒,PMU檢查REQ_PWRUP_STATUS,發現有被屏蔽但未執行的上電請求,然後一併執行上電。

- 如果還需要釋放某些模塊的復位,軟件在睡眠前也需寫REQ_SWRST_TRIG並且屏蔽其中斷。

- PMU 完成上電後,釋放對應模塊的復位,使其開始工作。

6.3.5 Wake-up Through MIO 使用MIO喚醒

介紹PMU結構時提到過,PMU可以使用6根MIO線作為輸入,實現外部喚醒(GPI1[15:10]對應MIO[31:26]),這樣就可以使用MIO基於三種方式實現喚醒,分別是外部事件,以太網PHY和CAN PHY

根據機制的不同,上述接口引發的任何中斷都會被髮送給PMU,以喚醒將該接口設置為其喚醒源的設備。

這裏還講了好幾種通過特殊方式喚醒設備的方式,內容比較多而且偏介紹性,我就只簡單翻譯一下了。

6.3.6 Wake-up on USB 使用USB喚醒

USB規範定義了鏈路層掛起模式,其中USB主機和設備都進入無活動階段以節省電力。將USB主機置於掛起模式的決定僅由軟件決定。一旦主機進入掛起模式,所有連接到該主機的設備都需要在3ms內進入掛起模式。USB設備無法自行進入掛起模式;但是,當支持鏈路電源管理(LPM)擴展時,USB設備可以請求USB主機進入掛起模式。當USB主機進入掛起模式時,所有USB設備都會跟隨。

USB主機可以通過計時器等中斷或通過具有特殊USB信號均衡的設備發出的遠程喚醒請求退出暫停模式(原文signal leveling我覺得是不是指的是信號電平)。USB設備也可以通過來自主機的中斷或遠程喚醒信號或額外通過主機重置信號來喚醒。

當USB處於掛起模式時,USB ULPI鏈路協議為實體物理層在D+/D-信號被定向到USB鏈路期間掉電提供了標準方法。在這種情況下,始終處於打開狀態的USB IP的子部分檢測喚醒信號並向PMU生成喚醒中斷,以繼續為USB塊和負責其設備驅動程序的處理器通電。

6.3.7 Wake-up on Ethernet 使用以太網喚醒

以太網喚醒可以通過兩種方式執行。

PHY喚醒:此喚醒過程可以使用從MIO引腳路由的GPI輸入信號來實現。

MAC喚醒:此喚醒過程廣泛稱為LAN喚醒。此過程是使用稱為magic packet的特殊網絡消息實現的。magic packet是一個廣播幀,其有效負載內的任何位置包含全部255個字節中的6個字節(FF FF FF FF FF FF FF FF FF),後面是目標計算機48位MAC地址的十六次重複,總共102個字節。檢測到magic packet將對正在運行設備驅動程序的處理器產生中斷,從而導致處理器直接喚醒。

6.3.8 Wake on Real-time Clock 使用實時時鐘喚醒

此功能允許系統使用內部實時時鐘(RTC)在預定時間喚醒。配置RTC以在到達特定時間和日期時生成中斷。(這個實時是指真實時間)

6.3.8 Wake through DAP 使用DAP喚醒

此功能通過調試器喚醒處於睡眠模式的系統。調試器可以通過DAP請求兩種可能的直接加電場景。一種選項可以喚醒FP域,其中包括MPSoC調試。另一個喚醒選項啓動雙Cortex-R5F子系統的通電。

6.3.9 Direct Wake by the APU or Cortex-R5F

當任何應用程序處理器或實時處理器斷電時,如果外圍設備試圖中斷(interrupt)斷電的處理器,則該中斷將被路由到PMU以觸發該特定處理器的通電。

6.3.10 Wake through GIC Proxy 使用GIC代理喚醒

如果應用程序處理器的斷電與整個FPD的斷電同時發生,則與該處理器關聯的LPD設備仍然可以通過首先觸發FPD的通電來觸發對該處理器的直接喚醒。這是通過在LPD中設置一個GIC代理塊來實現的,該塊可以選擇路由到PMU的外圍中斷作為直接喚醒以外的中斷(也就是上面的APU上電的關聯外設上電請求的方法)。收到來自GIC代理塊的中斷後:

- PMU為FPD供電。

- 釋放FPD和APU的復位。

- 取消屏蔽觸發該應用程序處理器的直接喚醒的中斷。

直接喚醒將生效,從而導致應用處理器上電。

6.3.10 Deep-sleep Mode

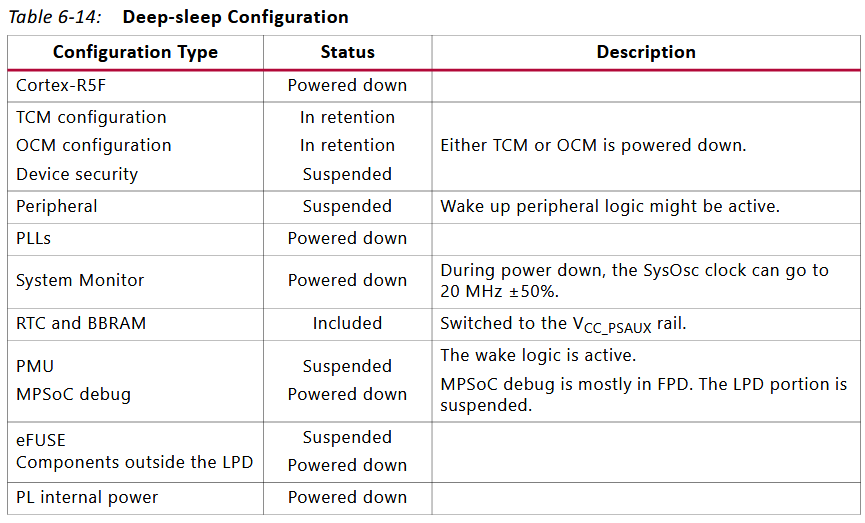

在講PMU結構部分時講到過PMU管理系統的電源模式,有低功耗和全功耗模式兩種,這裏由額外提到了深度睡眠模式。深度睡眠模式相比於低功耗模式還有更加節省功耗,他直接關閉了幾乎所有的外設,只保留幾個設備以供系統喚醒使用。這個模式下,系統只能由PMU的GPI(應該就是GPI的MIO)和RTC喚醒。這個模式相比直接把系統關了有一個顯著的好處,其不需要再進行boot process並且系統安全相關的狀態被保留了,從而顯著的減少了系統的啓動時間。在這個模式下只保留了維持boot狀態和安全狀態的最低功耗,連PMU都進入睡眠或者掛起了。這裏有一張介紹系統各部件在深度睡眠模式下的狀態:

這裏可以看到除了TCM,OCM被保留(但是也被斷電我不太理解),RTC和BBRAM(用來存儲安全信息)正常工作外別的部件都被斷電或者掛起了,其電源域也被切到了VCC_PSAUX這條電源軌上。

6.3.11 Deep-sleep Mode Programming Model/Example

這小節要講系統具體講深度睡眠模式的模型或例程,內容比較繁雜,在進入深度睡眠模式前需要進行一些的配置,例如R5F要進入鎖步模式,TCM和RTC要進行配置(這裏我也不知道對不對,原文比較奇怪),而進行睡眠模式後又需要將FPD,RPU,USB,PLLs,OCM和系統監視器斷電,TCM保留,RTC被設置且正常工作。下面有關例程的內容我就不解釋了,原文翻譯如下:

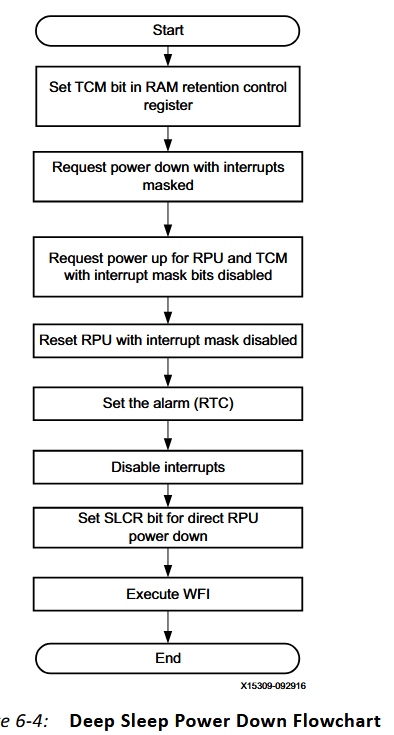

6.3.11.1 Power Down Procedure

斷電由Cortex-R5F啓動。當TCM處於保留狀態時,Cortex-R5F需要執行以下操作。

- 設置RAM_RET_CATRL寄存器中的TCM位。

- 在設置REQ_PWRDWN_TRIG寄存器的TCM位的同時設置REQ_PWRDWN_INT_MASK寄存器TCM位的中斷屏蔽

- 設置REQ_PWRUP_TRIG寄存器中的RPU和TCM位,同時禁用這些字段的中斷屏蔽位。

- 設置REQ_SWRST_TRIG中的RPU位,同時禁用其中斷屏蔽位。

- 設置鬧鐘。

- 禁用中斷。

- 設置SLCR位以請求直接RPU斷電並執行WFI指令。

這些操作會中斷PMU,從而關閉RPU。

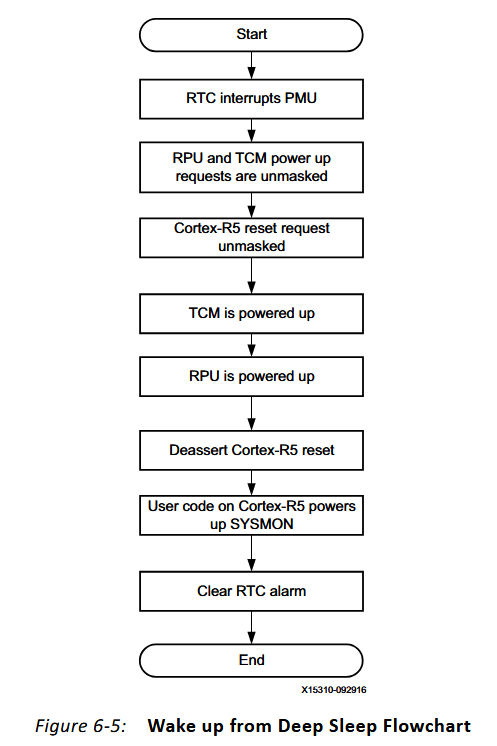

6.3.11.2 Wake Procedure

一旦RTC鬧鐘對PMU產生中斷,RTC喚醒的處理程序就會檢測是否為此目的加載了固件。如果沒有,處理程序會檢查on-demand程序是否在PMU中隊列。在斷電之前,Cortex-R5F請求RPU和TCM通電,同時屏蔽通電請求的中斷。它請求釋放Cortex-R5F復位,同時再次屏蔽該請求的中斷。從RTC醒來後,PMU繼續啓動RPU併發出Cortex-R5F復位。

.1. RPU和TCM加電請求作為TTC喚醒的一部分被解除屏蔽。

.2. Cortex-R5F復位請求作為TTC喚醒的一部分被解除屏蔽。

.3. 由於TCM加電中斷,TCM首先加電。

.4. 由於RPU加電中斷,RPU加電。

.5. 由於Cortex-R5F復位請求中斷,Cortex-R5F的復位釋放。

.6. Cortex-R5F上的代碼會將系統監視器從斷電狀態中釋放。

.7. Cortex-R5F上的代碼會清除RTC警報。由於RTC具有中斷狀態寄存器,因此將警報位設置為1會清除中斷。

6.3.12 Isolation Request 隔離請求

隔離指的是在某個電源域斷電前,將該電源域與其他域連接的信號強制設置為某個特定值的操作。這個操作的目的是為了防止斷電過程中產生的錯誤電平影響其他模塊的電路。這種錯誤是由於Crowbar Current(直通電流/穿通電流)產生的。具體的什麼是直通電流太偏模電了我也不太懂。具體操作來看原文:

PMU使能各個電源域的隔離。這可以通過在REQ_ISO_TRIG全局寄存器中設置適當的位來完成。低功耗、全功率和PL域之間由三個bit位進行隔離控制。有不同的隔離組合可用。通過寫入RST_ISO_TRIG寄存器和REQ_ISO_INT_MASK寄存器的bit0,全功率域可以與低功率域和PL域隔離;通過寫入這些寄存器的bit1,PS與PL隔離;通過寫入bit2,PS和PL被隔離,不包括PCAP接口;最後,要鎖定全功率域上的隔離,請寫入bit4。

6.3.13 Reset Services 復位服務

這小節主要講了REQ_SWRST_TRIG寄存器不同位對應的復位服務,前提是這些其這些服務對應的REQ_SWRST_INT_MASK沒有被寫0,也就是被屏蔽。表太長了這裏就不展示了,具體看第139頁的圖6-15。

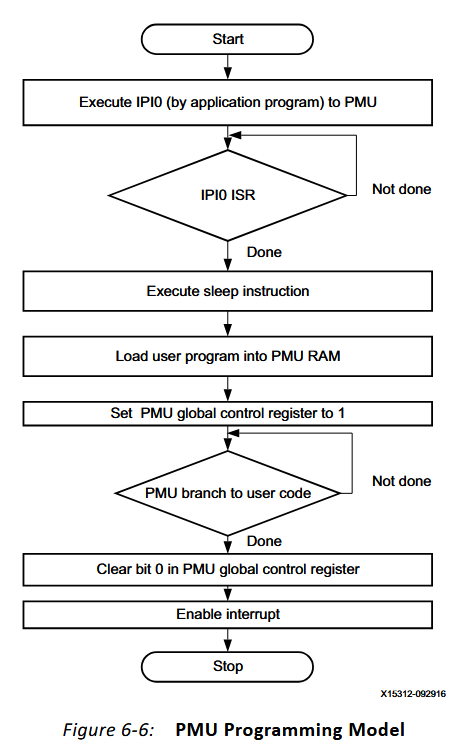

6.3.14 Programming Model 編程模型

我們之前提到過,PMU可以通過用户編程,在PMU RAM中執行程序來實現PMU的功能擴展,這些程序也被稱為PMU Firmware。這節的內容就是指導用户如何進行具體的編程,我這裏就就只翻譯一下了:

除了AMD提供的固件之外,PMU還可以執行實施高級系統監控和系統關鍵功能的用户程序。通常,PMU代碼加載可以在引導時通過CSU ROM代碼或通過第一階段引導加載程序(FSBL)進行。在此期間,PMU要麼處於已加載的維護模式,要麼處於睡眠模式。為了確保PMU處於睡眠模式,IPI0用於中斷PMU。為了響應IPI0中斷,該IPI的中斷服務例程禁用中斷並執行睡眠指令,隨後轉移到加載到RAM中的用户代碼。這保證了處理器保持在睡眠模式,並且不會被中斷執行任何服務,直到另一個主機通過使用PMU全局控制寄存器中的喚醒位顯式喚醒它。主處理器將用户程序複製到PMU RAM中後,利用PMU全局控制寄存器中的處理器喚醒功能來指示PMU處理器執行新加載的維護代碼。

此處列出了加載用户級程序並開始執行其所需的步驟。

- 另一個處理器上的應用程序(APU或RPU)對PMU執行IPI0。

- IPI0中斷服務程序。

- 禁用所有中斷。

- 執行睡眠指令。睡眠指令之後的指令必須是RAM中用户代碼地址的分支。

- 應用程序將PMU用户程序加載到RAM中。

- 應用程序將1寫入PMU全局控制寄存器的位[0]以喚醒處理器。

- PMU在睡眠指令之後開始執行指令,並返回代碼中的main()函數。

- PMU分支到用户代碼。

- 用户代碼將清除PMU全局控制寄存器中的位[0]並使能中斷。

上級程序可以檢查PMU全局控制寄存器以確定硬件加載和執行的狀態。

本章總結

PMU的內容實在是太多太多了,50頁的內容就算是精簡的講也非常多,當然內容多收穫也多。我們下篇隨筆再見。********