- 前言

- Chapter 2: Signals, Interfaces, and Pins 信號,接口和引腳

- 2.1 Introduction

- 2.2 Dedicated Device Pins

- 2.2.1 Power Pins

- 2.2.2 Clock, Reset, and Configuration Pins

- 2.2.3 JTAG Interfaces

- 2.2.4 MIO Pins

- 2.2.5 DDR Memory Controller I/O

- 2.2.6 PS GTR Serial Channel Device Pins

- 2.3 PS-PL Signals and Interfaces

- 2.3.1 PS-PL Voltage Level Shifters

- 2.3.2 Processor Communications

- 2.3.3 System Error Signals

- 2.3.4 MIO-EMIO Signals and Interfaces

- 2.3.5 Miscellaneous Signals and Interfaces

- 2.3.6 Dedicated Stream Interfaces

- 2.3.7 DisplayPort Media Interfaces

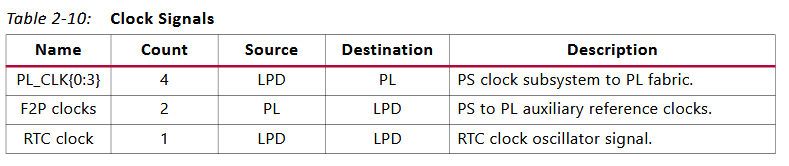

- 2.3.8 Clock Signals

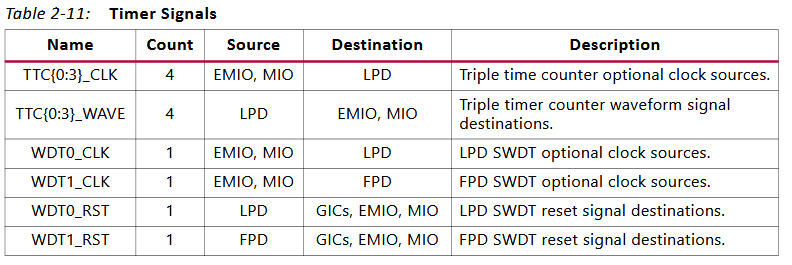

- 2.3.9 Timer Signals

- 2.3.10 System Debug Signals and Interfaces

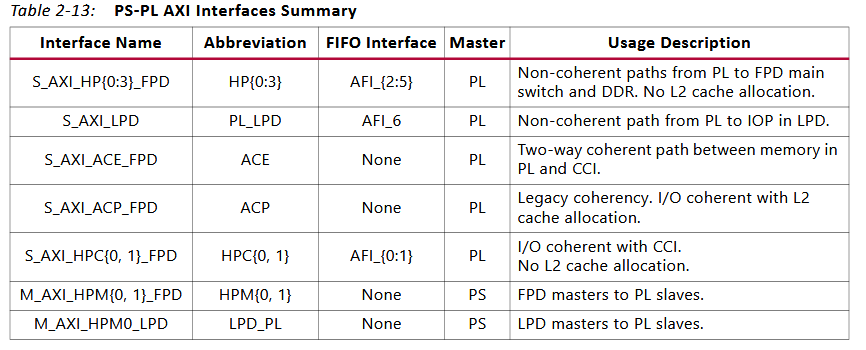

- 2.4 PS-PL AXI Interfaces

- 本章小結

前言

上一章講了ug1085MPSOC技術參考手冊的第一章,也就是MPSOC整體概述的一章,這次我們來講第二章,也就是關於信號與引腳以及接口的一章。

Chapter 2: Signals, Interfaces, and Pins 信號,接口和引腳

2.1 Introduction

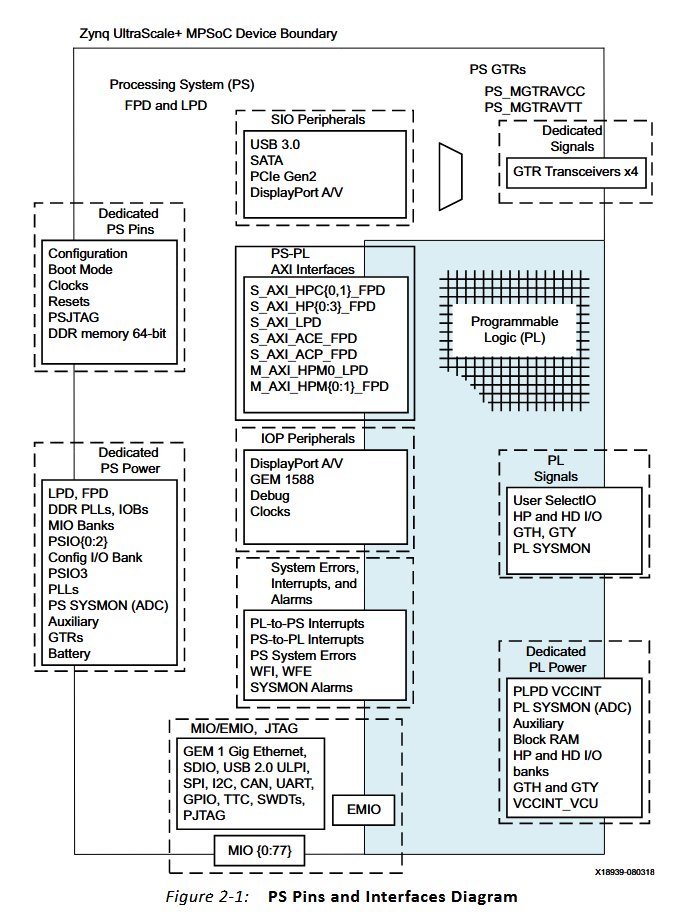

這一章主要介紹兩個方面,一是MPSOC的專用引腳,這些引腳的功能是確定的,不像MIO引腳功能較多,可以分配給不同的外設控制器。這些引腳主要是電源,時鐘等引腳。第二個方面就是PL端與PS端相連的信號,這些信號就比較多了,我們待會一個個介紹。最後還介紹了以下PS和PL端的AXI互聯接口。下面這張圖給出了PS和PL端信號和接口的總覽,還有一些電源域的內容:

2.2 Dedicated Device Pins

這一節就是介紹設備專用引腳的,專用引腳主要有6類,這些引腳的功能和用途是固定的,我們來挨個介紹。

2.2.1 Power Pins

MPSOC內部是一個非常複雜的系統,不同的部分需要不同的供電指標,這些引腳就是MPSOC的供電引腳,要注意這些引腳是在PCB上與供電端之間連接的,其對應的供電電壓以及其他參數都可能不同,而且應該還有特定的上電順序,更為具體的內容在Zynq UltraScale+ MPSoC Data Sheet: DC and AC Switching Characteristics (DS925) 中會寫到,這裏就不再貼表格了。

2.2.2 Clock, Reset, and Configuration Pins

這類引腳是有關時鐘,復位以及配置MPSOC的,比較典型的有PS端參考時鐘,PLPS端復位信號,PLPS端初始化完成信號以及boot模式設置信號,這些信號都是實際接到PCB上的,這裏還要在強調一遍。信號比較多這裏也不在詳述了。

2.2.3 JTAG Interfaces

JTAG接口是用來連接上位機調試MPSOC的,這小節額外提到了MPSOC有兩個JTAG接口,一個PSJTAG一個PJTAG,但是我沒看懂什麼是PJTAG,描述為The PJTAG interface port provides exclusive access to the Arm DAP controller。

2.2.4 MIO Pins

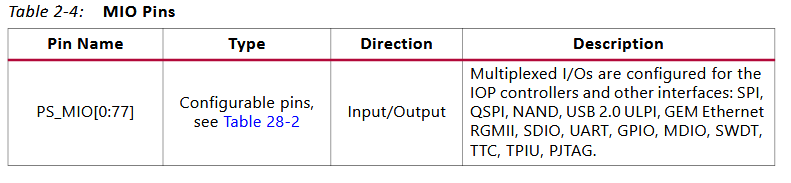

MIO就是多用途IO,這些IO的功能是通過訪問IOU_SLCR寄存器集合來實現的,MPSOC總共有78個MIO,這些MIO被分為26個一組共三組,與其相連的外設如下圖所示:

2.2.5 DDR Memory Controller I/O

PS端的DDR控制器連接的IO也是固定的,不過這裏並沒有講,説內容在第17章。

2.2.6 PS GTR Serial Channel Device Pins

PS端的GTR也有固定使用的幾個引腳,也就是説只有這些引腳才能用GTR實現要求的協議,例如PCIE和以太網,不夠這部分我也不太熟,這裏也説詳細內容看第29章,也不介紹了。

2.3 PS-PL Signals and Interfaces

PS端和PL端有一大堆信號來實現互相連接,例如PS端傳給PL的時鐘,PS與PL互傳的中斷等等,這一節就是介紹這些信號。這些互聯信號排除AXI互聯接口外還有10類,下面一一介紹。

2.3.1 PS-PL Voltage Level Shifters

我們在看PS端和PL端進行互聯時,可能會想當然的以為是不是直接走線過去就能直接連接了,但是這部分內容卻説明PS與PL的連接沒有這麼簡單,來看下面的原文:

PS使用電壓水平轉換器與PL通信。PS和PL之間的所有信號(輸入和輸出)和接口都穿過電壓邊界並通過電壓水平轉換器路由。一些電壓電平轉換器使能由PL電源狀態控制,包括PL、EMIO JTAG、PCAP接口和其他模塊的信號。PL被視為單獨的電源域(PLPD)。

也就是説,PL端與PS端的連接首先要通過電壓電平轉換器,之後才能與PS進行相連,相當於轉換器是所有互聯信號的基礎。不過這裏提到AXI互聯是一個單獨的模塊,需要像PMU發送PS-PL電源隔離失效請求才能夠互聯,不過這裏並沒有展開講。

2.3.2 Processor Communications

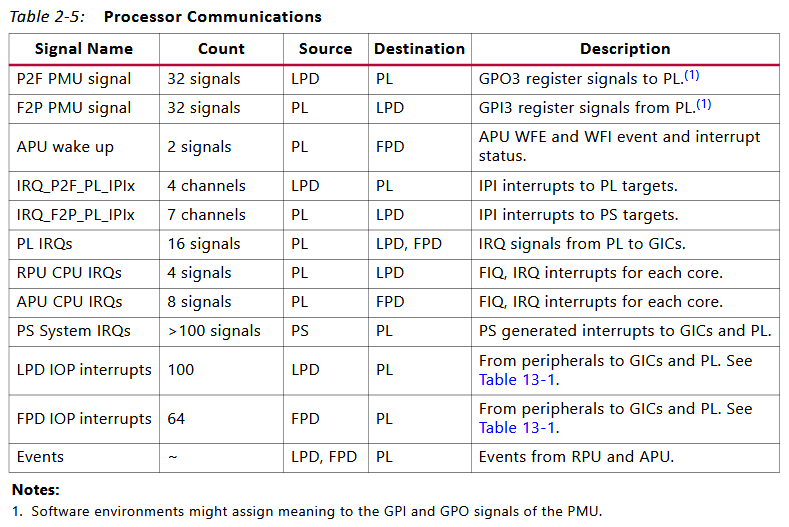

這一小節描述了PL與PS端PMU,處理器以及GIC中斷控制器通信的信號,列表如下:

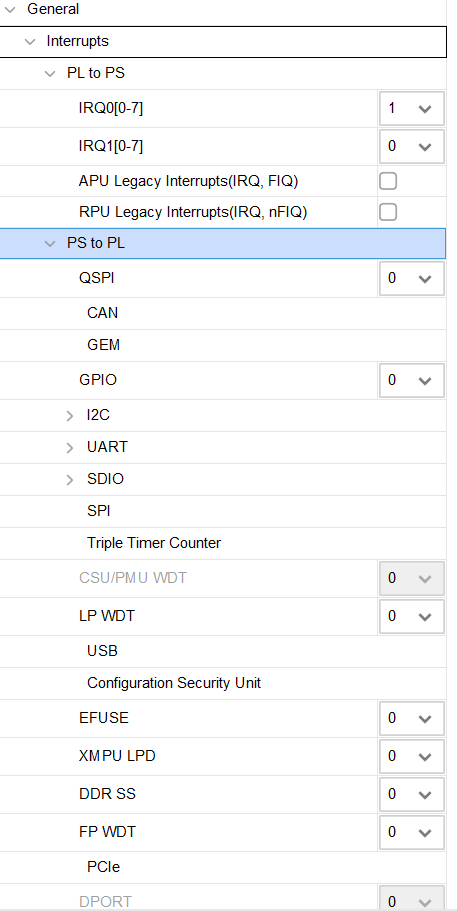

這裏大致可以分為兩類信號,一類PL與PMU交流的信號,我沒有找到這類信號的實際意義。第二類是中斷類信號,PL和CPU互相中斷的信號,有PL和PS進行IPI中斷(處理器間中斷)的信號,還有就是LPD和FPD外設連接GIC或者PL的中斷信號。我還查看了VIVADO中的中斷設置,可以來對照一下:

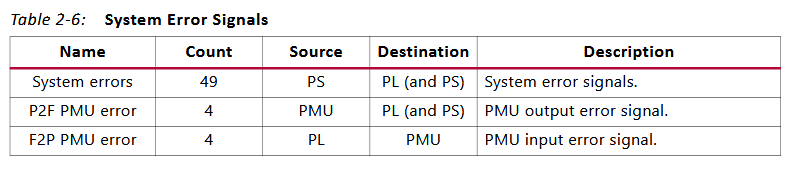

2.3.3 System Error Signals

這裏文檔沒有詳細解釋什麼是系統錯誤信號,只列了一個表:

我也不太理解這些信號的作用,這裏就跳過了。

2.3.4 MIO-EMIO Signals and Interfaces

我們之前提到過,PS端的外設不僅僅可以連接到MIO上,還可以通過EMIO連接到PL端的IO上,這裏就顯示了外設是否運行連接到EMIO以及其性能是否改變,其結果如下圖所示:

這小節有個標識很顯著的建議,來看下原文:

建議:IOP接口I/O信號的路由必須配置為一個組。也就是説,接口內的信號不得分裂並路由到不同的MIO管腳組。例如,如果SPI0時鐘被路由到MIO管腳40,則SPI 0接口的其他信號必須被路由到MIO管腳41至45。同樣,IOP接口內的信號不得在MIO和EMIO之間分割。然而,IOP接口內未使用的信號不一定需要路由。每個未使用的MIO引腳都可以配置為一個GPIO。

我理解一下這段話,也就是説,對於複用MIO有一個前提,就是複用的MIO必須都處於一個group中,如我們之前所説,78個MIO被以26個一組分為3組,這些組就是複用的限制,另外還有限制是不能既複用MIO又複用EMIO。

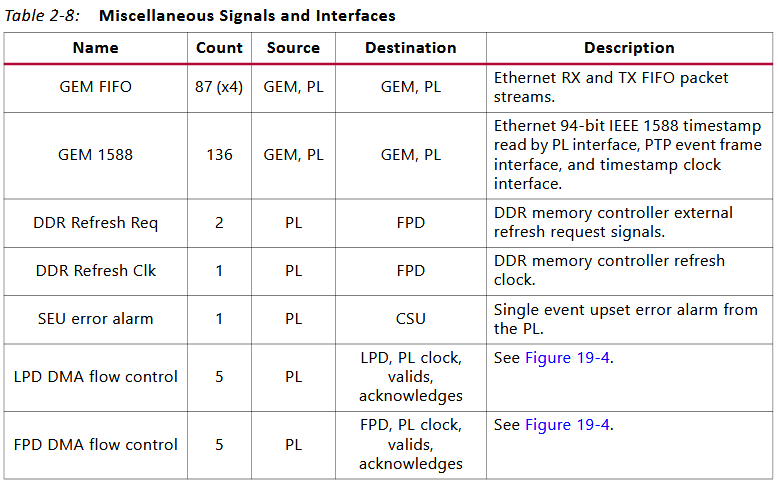

2.3.5 Miscellaneous Signals and Interfaces

這節直譯叫做雜項信號,顧名思義我也沒太看懂這些信號是幹嘛的,不過可以確認的是處理兩個和GEM相關的信號,其餘信號是PL端用於額外控制PS端外設的,具體的內容如下圖:

2.3.6 Dedicated Stream Interfaces

這部分似乎是在説PS端的GEM(Gbit 以太網控制器)能夠直接路由到PL進行包處理以及視頻廣播,不過我沒有用過這個功能,這裏也説詳細內容見第34章,這裏不在説了。

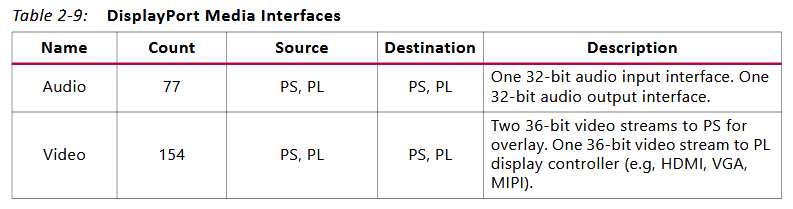

2.3.7 DisplayPort Media Interfaces

這個部分講DP口,就是平時在顯示器上常見的DP口,似乎PS端的DP控制器支持雙向傳輸,即可以由PS傳到PL,又可以由PL傳到PS,但是詳細內容我也不懂,這裏就列了下DP口的傳輸信號,如下圖所示:

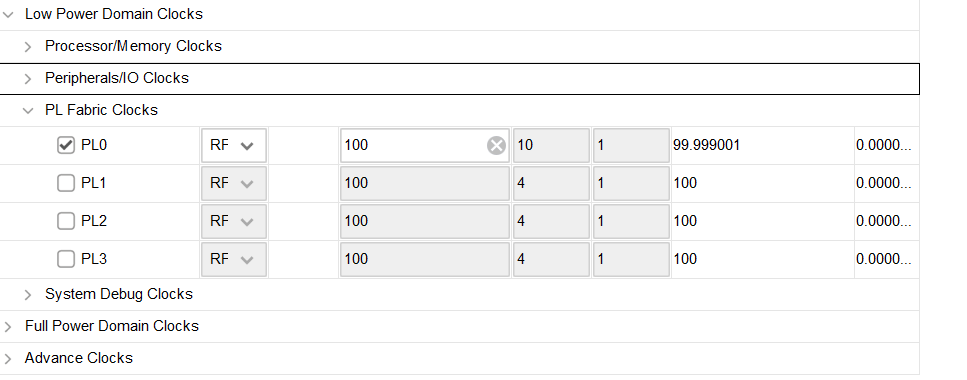

2.3.8 Clock Signals

我們在使用VIVADO設置MPSOC的BLOCK時,能夠看到在PS-PL互聯選項中有提供給PL時鐘的選項,這裏的時鐘信號就代表了那四個被傳輸給PL的時鐘信號,除此以外PL也可以給PS傳輸一些時鐘信號,我這裏找了下VIVADO中的設置界面,可以對照一下:

2.3.9 Timer Signals

MPSOC有4個三路定時器和兩個看門狗,一個負責LPD域一個負責FPD域的看門。定時器可以被用在PL端,以實現比較簡單的波形計數,而看門狗則實現對PL端邏輯的運行監控,也就是PL端要不停喂狗來防止看門狗對PL產生復位信號。但是我這裏也有點疑問,三路定時器的計數值PL端是否能夠設置定時器的計數值,我看了一下定時器章節但是沒看見相關內容,我估計應該是不能。定時器信號如下表:

2.3.10 System Debug Signals and Interfaces

這小節應該是在講系統的degug信號,但這裏完全沒有做解釋,我也不多説了。

2.4 PS-PL AXI Interfaces

這節講了下PS與PL進行連接的AXI信號接口,AXI接口對於連接PL和PS是非常關鍵的,這一連接不僅涉及數據傳輸,還涉及統一地址映射,也是很重要的內容,這裏也只是簡要提了一下,更為具體的內容等到以後看到第35章的時候再詳細講,現在就只帶過一下。PS與PL的AXI互聯總線如下圖所示:

綜合的來説這些總線總的就分為兩組,一組PS端做主器件控制PL,一組PL做主器件控制PS,當然這其中還分為PL連接FPD和LPD,以及直接連接CCI和APU緩存的區別,不過我們以後再講。

本章小結

本章主要講了一大堆的信號線,這些信號線很多還是比較關鍵的,特別對於PCB製作和PL與PS互聯,但是內容也比較偏介紹性,我們下次來看第三章。