- 前言

- 專有名詞中英文對照表

- Chapter 6: Platform Management Unit 平台測量單元

- 6.1 Introduction 介紹

- 6.1.1 Power Modes電源模式

- 6.1.1.1 Battery Powered Mode

- 6.1.1.2 Low-Power Operation Mode

- 6.1.1.3 Full-Power Operation Mode

- 6.1.2 PMU System-level View PMU系統級總覽

- 6.1.1 Power Modes電源模式

- 6.2 Functional Description 功能性描述

- 6.2.1 PMU Processor PMU處理器

- 6.2.2 PMU Processor Interfaces PMU處理器接口

- 6.2.3 PMU Clocking PMU時鐘

- 6.2.4 PMU Reset PMU復位

- 6.2.5 PMU RAM

- 6.2.6 PMU ROM

- 6.2.6 MBIST Functionality 內存內建自測功能

- 6.2.7 Scan Clear Functionality 掃描清除功能

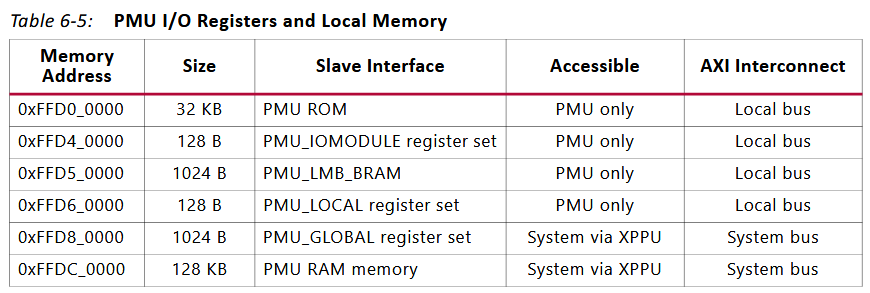

- 6.2.8 PMU I/O Registers PMUI/O寄存器

- 6.2.8 PMU Global Registers PMU全局寄存器

- 6.2.8 PMU GPIs and GPOs

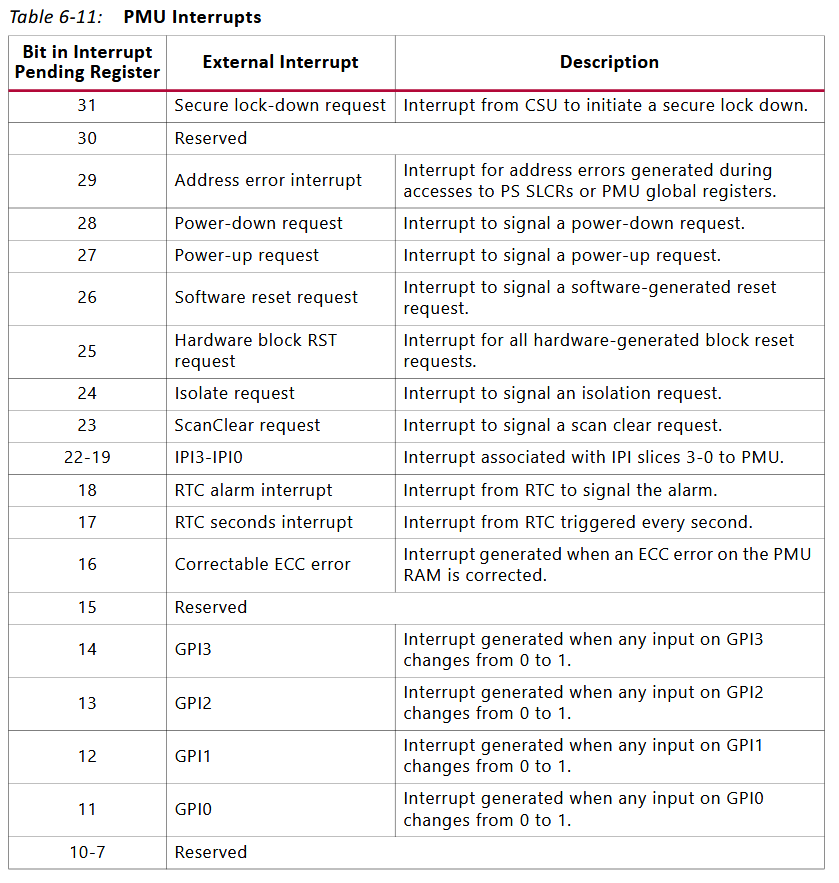

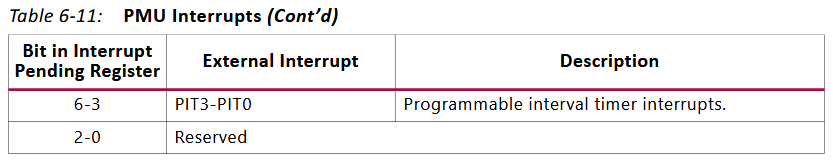

- 6.2.9 PMU Interrupts

- 6.2.10 PMU Error Handling and Propagation Logic PMU錯誤處理與傳播邏輯

- 6.1 Introduction 介紹

- 小節

前言

上一章講了ug1085MPSOC技術參考手冊的第四章,講了有關MPSOC RPU的相關內容,這次我們來講第六章,可以説是MPSOC中最複雜核心器件的PMU(第五章GPU我就跳過了主要我還沒打算用),這部分內容由於非常多而且非常複雜,在描述的時候我可能會大量的貼原文檔的翻譯。同樣這裏再次事先聲明,由於我對PMU的理解還不夠,所以我用了AI工具來理解這些內容,所以解釋可能有問題也歡迎指出。。

專有名詞中英文對照表

| 英文 | 簡稱 | 中文翻譯 |

|---|---|---|

| platform measurement unit | (PMU) | 平台管理單元 |

| software test library | (STL) | 軟件測試庫 |

| configuration and security unit | (CSU) | 配置與安全單元 |

| Battery-backed RAM | (BBRAM) | 電池後備RAM |

| Real-time clock | (RTC) | 實時時鐘 |

| IO peripherals | (IOP) | IO外設 |

| Inter-Processor Interrupt | (IPI) | 處理器間中斷 |

| memory built-in self test | (MBIST) | 內存內置自測試 |

| Advanced Interrupt Bus | (AIB) | 先進中斷總線 |

| Triple Modular Redundancy | (TRM) | 三模冗餘 |

| power-on reset | (POR) | 上電覆位 |

| system reset | (SRST) | 系統復位 |

| built-in self-repair | (BISR) | 內建自修復 |

| programmable interval timers | (PITs) | 間隔可編程定時器 |

Chapter 6: Platform Management Unit 平台測量單元

6.1 Introduction 介紹

PMU即platform measurement unit平台測量單元(我之前一直以為是平台管理單元,不夠我感覺都不足以描述其功能)是MPSOC系統中一個非常重要的部件,我們之前講的APU,RPU這些部件在系統中負責一些應用層面的任務,例如數值運算,內存控制,外設控制,而PMU單元則不太一樣,雖然PMU的本質仍然是類似於APU,RPU一樣的處理器模塊,但是其負責MPSOC系統中絕大部分的底層管理工作,如BOOT,電源管理,復位管理,系統測試,系統錯誤管理等等。這一章節主要就要介紹PMU的主要構成以及功能,我這裏翻譯如下:

PMU執行以下的任務。

- 根據啓動優先級初始化系統

- 電源管理

- 軟件測試庫(STL)的執行(可選)

- 系統錯誤處理

這裏還提到CSU模塊會監測系統温度傳感器,不過後續講到CSU時再詳説。

6.1.1 Power Modes電源模式

由於PMU涉及電源管理的內容,這一小節主要就介紹了一下MPSOC的電源模式與電源域。電池模式主要有電池供電模式,低功耗工作模式以及全功耗工作模式,下面就稍微介紹一下,因為源文檔也只是大致提了一下。

6.1.1.1 Battery Powered Mode

電池供電模式就是當主供電斷開時,為了保留一些安全性和實時時鐘的設置而對其進行供電的模式,在這個模式下只有兩個模塊會被電池電源域供電:

- Battery-backed RAM (BBRAM)電池後備RAM,用來存儲一些安全配置的關鍵信息

- RTC以及其晶振,這個應該是用來做根據實際時間喚醒或者關機任務的

6.1.1.2 Low-Power Operation Mode

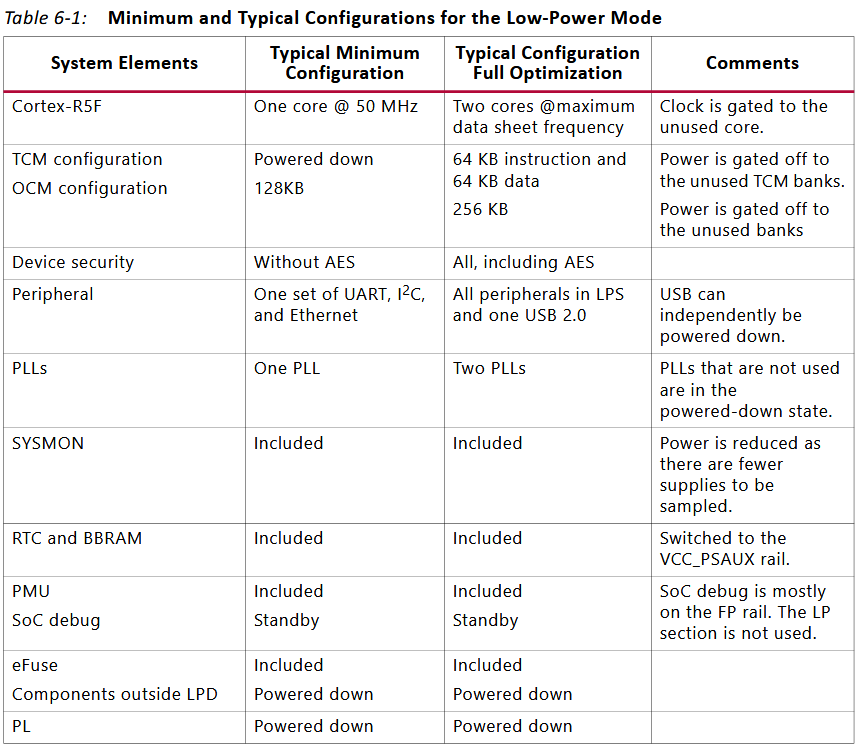

低功耗模式下除了SATA和DP口外的外設都會工作,(這裏的原文説的是在低功耗電源軌上的PS模塊都會工作,包括PMU,RPU,CSU,IOP)同時列出了一個表格來展示在低功耗模式下其可配置的最少和最多的模塊:

注意低功耗模式下APU和PL都是不能使用的。

6.1.1.3 Full-Power Operation Mode

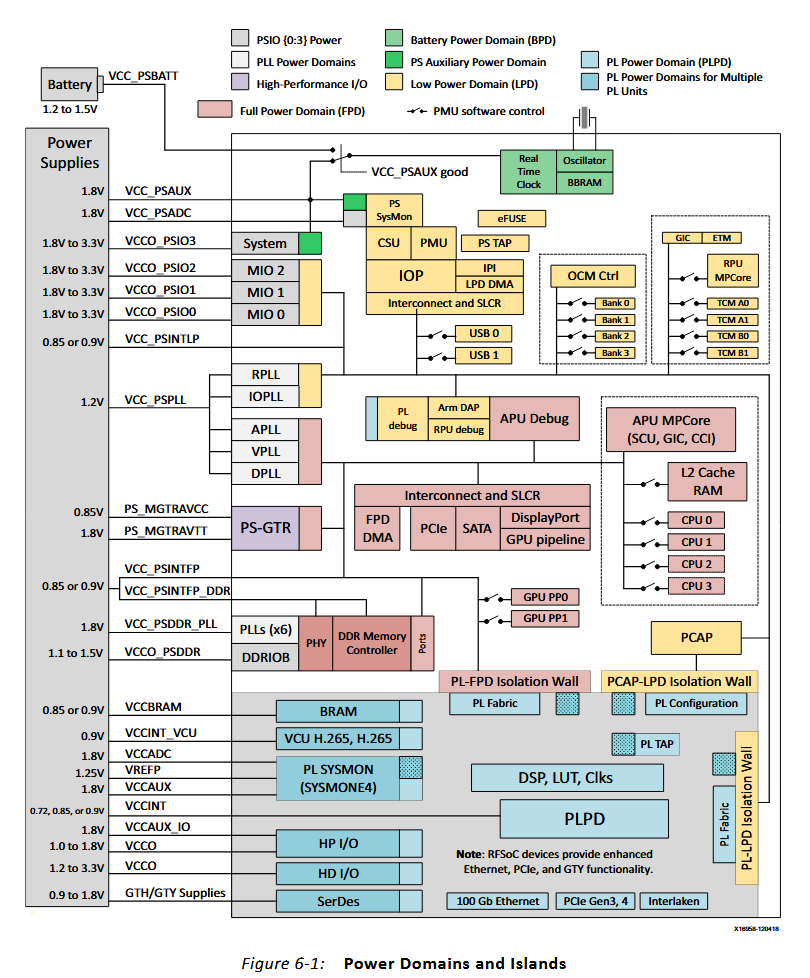

全功耗模式就是所有電源域都供電的電源模式,這節內容主要是一張電源域的總覽圖:

圖中比較明顯的就是黃紅藍的三片區域對應着LPD,FPD和PLPD三個電源域,最上方還有一小部分綠色代表電池電源域,我覺得還有一個比較重要的地方是VCC_PSINTLP,VCC_PSINTFP以及VCCINT這三根電源線,分別連接了LPD,FPD和PLPD的主要部件上,其餘很多的電源線是專門給一些特殊部件供電的,這三根則是負責每個電源域的核心供電。

6.1.2 PMU System-level View PMU系統級總覽

這一節主要是給下一節介紹PMU的具體功能做鋪墊,大體介紹了一下PMU中的部件,我這裏以貼翻譯為主:

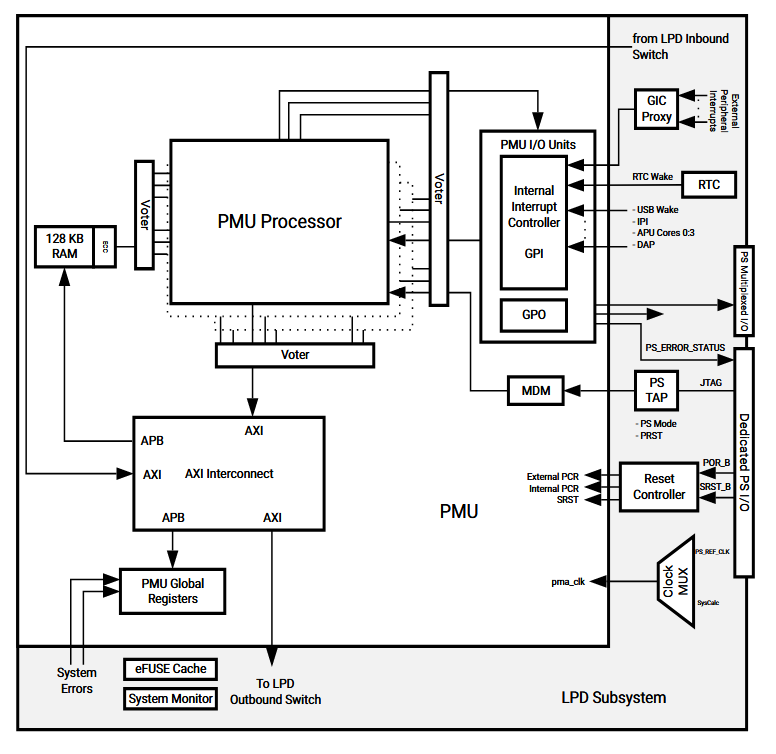

PMU塊位於低功耗域中。圖6-2顯示了PMU的方框圖。它包括以下子組件:

- 專用的、故障容忍的三冗餘處理器。

- 用於保存PMU代碼的PMU ROM,其中包括PMU啓動序列、處理上電,斷電請求或中斷的例程。

- 128KB用於存儲代碼和數據ECC RAM。

- 僅由PMU訪問的PMU本地寄存器。

- PMU全局寄存器,可由PMU處理器以及系統內的其他總線主設備訪問。其中包括所有電源、隔離和重置請求寄存器,還包括錯誤捕獲寄存器和系統電源狀態寄存器。

- 32位AXI從機接口,允許PMU外部的主機訪問PMU RAM和全局寄存器。

- PMU中斷控制器管理PMU的23箇中斷。其中四個中斷來自處理器間互連(IPI)。

- GPI和GPO寄存器,用於PMU與PMU、MIO、PL和PS內的其他資源進行信號交流。

- 六個輸出和六個輸入。(對於MIO)

- 從PMU到PL的32個GPO輸出和從PL到PMU的32個GPI輸入。

- 47個輸入PMU的系統錯誤標識線。

- CSU錯誤代碼。

- 32個存儲器內建自測試(MBIST)狀態信號和32個MBIST完成信號。

- 三個直接復位控制信號。

- 四個AIB狀態信號和四個AIB控制信號。

- 11個邏輯清除狀態信號(後面會講到是進行系統清零時使用的)。

- DDR retention控制。

- PL對CSU的三個可編程設置。

最後這部分講GPI和GPO部件描述可能比較奇怪,總的來説GPO和GPI相當於PMU的IO口,是連接到其他器件上的接口,這些接口大部分都有固定用途,例如連接到別的處理器去接收其服務請求,上電請求等等功能,我們後面會講這部分。最後還有一張PMU的整體結構框圖:

實際上PMU的核心部件都放在這張圖上了,我稍微解析一下:首先PMU的核心是三重冗餘處理器,圖中處理器那裏有兩個虛框就代表着三重處理器。而三重處理器連接外部都需要通過Voter表決權來實現,這也是三重冗餘的實現核心。其次來看左半部分,有128KB RAM,AXI互聯模塊,PMU全局寄存,這部分是PMU處理器對外部器件和PMU RAM訪問的核心,也是外部訪問PMU RAM和PMU全局寄存器的核心。最後則是右半部分,包括PMU IO單元,裏面有GPI和GPO以及中斷控制器,從外部來的中斷,電源請求以及PMU對外部的系統級控制信號都是走的這部分。還要一部分專用PS IO會走別的線進入PMU就不説了,主要我沒看到是用在什麼地方的。

6.2 Functional Description 功能性描述

這一節就要緊接着上一節對PMU的介紹來詳細描述PMU的各部件功能了,這裏首先描述了PMU的核心功能:

- 本節概述了PMU內的功能

- 在POR後和CSU復位釋放之前執行事件序列。包括以下功能。

- 使用系統監視器檢查電源水平,以確保CSU和LP域的其餘部分正常運行。

- 初始化PLL的默認配置及其潛在旁路。

- 觸發並排序必要的掃描和MBIST。

- 此階段的捕獲和信號錯誤。錯誤ID可以通過TAG讀取。

- 釋放CSU復位。

- 在應用程序和實時處理器的睡眠狀態期間充當其代表,並在其喚醒請求後啓動其通電和重新啓動。

- 始終保持系統電源狀態。

- 處理不同塊的通電、斷電、重置、內存內置自修復(MBISR)、MBIST和掃描歸零所需的一系列低等級事件。

- 在睡眠模式期間管理系統並基於各種觸發機制喚醒系統。

- PS級錯誤捕獲和傳播邏輯。

6.2.1 PMU Processor PMU處理器

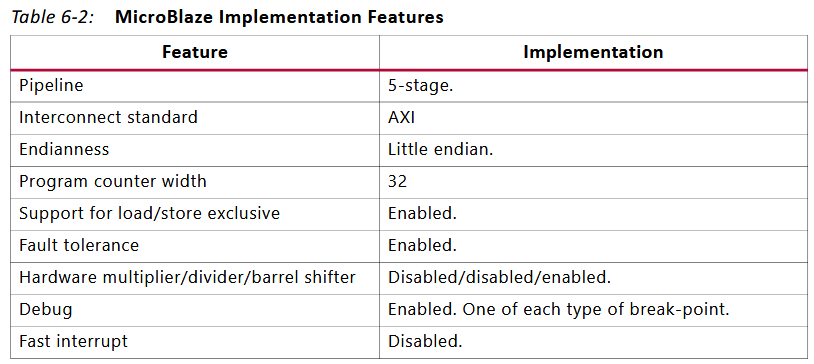

我們之前提到過PMU的三重冗餘處理器,這裏只是稍微詳細説了一下,比較重要的有兩點,首先PMU的處理器是沒有Cache的,只能直接訪問PMU RAM。其次,儘管PMU RAM可以被外部器件訪問,但是該訪問必須在PMU的處理器處於休眠狀態時進行,否則訪問可能得不到迴應或者導致系統錯誤。這裏同時給出了PMU處理器的特性表,不過意義不怎麼大:

6.2.2 PMU Processor Interfaces PMU處理器接口

由於PMU本身就可算作一個單獨處理器模塊,那麼就必須有供給該處理器使用的數據接口,用來滿足其數據和指令的讀寫以及與外部器件的交流。這一節大致總結了PMU處理器的接口,可以對應PMU框圖中除了處理器外的部分,我這裏翻譯如下:

PMU提供輸入/輸出信號,這些信號按功能分組到以下接口中。

- 32-位AXI主接口,連接到低功耗域(LPD)互連,允許PMU訪問其他PS資源,包括SL CR寄存器和IPI塊

- 32-位AXI從機接口,允許外部處理器訪問PMU全局寄存器和PMU RAM。

- PMU時鐘和重置信號

- 電源控制接口連接到PS內的所有電源島

- L2, OCM, and TCM RAMs

- APU_Cores [3:0].

- Dual-core Cortex-R5F® real-time processor.

- USB0 and USB1.

- GPU pixel-processor (PP) PP0 and PP1.

- Full-power and PL domain crossing bridges FPD和PL的互聯橋

來自GPIO, RTC, APU GIC, RPU GIC,和USBs的喚醒接口

- 中斷接口

- 設備復位控制接口

- 內存BIST(內建自測)和BISR(內建自修復)控制接口

- 其他雜項接口,包括電源監視器接口

- 錯誤捕獲和傳播接口

這裏着重説了GPI1和GPO1寄存器中連接MIO的幾個引腳,GPI和GPO是PMU的輸入輸出寄存器組,後面還會着重講這部分,這裏就不説了。

6.2.3 PMU Clocking PMU時鐘

這一小節講了PMU的時鐘是來源於位於PS SYSMON中的內部環形晶振(IRO),工作在180MHz,而且該時鐘在VCC-PSAUX電源達到規定電壓後就會開始工作。

6.2.4 PMU Reset PMU復位

這節講了PMU的兩種復位方式,一種是上電覆位POR,這種復位方式會復位PMU中的所有部件,在POR後PMU會執行SCAN和BIST來清除LPD和FPD。另一種系統復位SRST則只會復位PMU的處理器,互聯模塊以及小部分的本地和全局寄存器,會保留系統的供電狀態。

6.2.5 PMU RAM

PMU RAM是為了擴展PMU功能而設計的,可以用來存放用户代碼和數據的128KB帶有ECC的RAM,由於PMU ROM是被固化在PMU中的,不能夠進行調整,想要PMU實現更復雜的功能就需要使用PMU RAM。而使用PMU RAM也有一定限制,就是PMU RAM只能字訪問,使用4個字節進行讀寫,還有的限制就是外部訪問PMU RAM時需要使PMU處理器處於休眠狀態,本節還描述了PMU RAM的訪問優先級,如下:

- PMU處理器數據讀寫

- PMU處理器指令獲取

- 外部訪問

6.2.6 PMU ROM

PMU ROM是存放有關PMU最基礎數據以及代碼的部件,不能進行更改,其中的代碼是整個MPSOC系統啓動的關鍵,我這裏把原文翻譯來了解其作用:

PMU包括一個ROM,其中保存了PMU的引導代碼、其中斷向量以及PMU可以根據請求執行的服務例程。PMU ROM負責PMU內的各種功能。以下是由ROM代碼執行的任務列表。

- 引導前任務

- 清除PMU RAM

- 啓用系統監視器並檢查LPD供電。

- 使用初始設置配置PLL。

- 觸發和排序必要的掃描和BIST來清空PS(應該指PS的內存和觸發器)。

- 釋放CSU復位。

- 啓動後任務

- PS內的上電和掉電域。

- 啓用和控制內置自我修復(BISR)。

- 根據請求或作主電源設備上電時使復位部分模塊。

- 根據請求執行固件代碼。(指的就是用户編寫的代碼PMU firmware)

6.2.6 MBIST Functionality 內存內建自測功能

內存內建自測功能是用來測試MPSOC的PS端各個部件的內存是否正常工作的一種測試技術,實際上説是測試MBIST還有清空內存的功能,這些測試單元由PMU進行控制,主要的測試或清空的內存有這幾個:

- APU和RPU核心

- CAN,USB和GEM控制器

- GPU,PCIe,SIOU

- PS-PL的互聯橋RAM

這四個部分都有對應的MBIST控制和狀態寄存器:

- MBIST_RST rw

- MBIST_PG_EN rw

- MBIST_SETPU rw

- MBIST_DONE ro

- MBIST_GOOD ro

6.2.7 Scan Clear Functionality 掃描清除功能

掃描清除功能這部分內容我有點沒太看懂,這裏就結合AI分析來説一下。總的來説,SCAN Clear這個功能是用來和MBIST一起實現歸零化任務的,也就是使得整個MPSOC中的數據都歸零,內存的歸零是使用MBIST實現的,而觸發器中實際上也含有數據,這些數據的清零就是SCAN Clear實現的。MPSOC系統中只有PMU和CSU能夠控制掃描清除引擎,而其中只有PMU能監測掃描過程,CSU則只能啓動,且在每個功耗域都有各自的掃描引擎存在。此外,這裏還有一部分有關實施LP域清除掃描的復位指南,比較複雜,這裏不再描述了,具體在第116頁。

6.2.8 PMU I/O Registers PMUI/O寄存器

這一節以及下面的幾節實際上都在講PMU的輸入輸出功能,這小節算是個總覽,主要是給出了PMU中所有寄存器的地址映射以及大小,還要訪問權限,全在下面這張圖中了:

PMU_IOMODULE寄存器組裏有很多關鍵部件,如中斷控制器控制寄存器,GPI{0:3}, GPO{0-3}, 以及PIT0-PIT3。而PMU_GLOBAL寄存器賦予了PMU進行中斷控制和觸發PMU服務的功能。

6.2.8 PMU Global Registers PMU全局寄存器

PMU全局寄存包含了一大堆PMU控制外界部件的寄存器,由於數量實在太多不可能一個一個解析,我大致看了下有這麼幾個種類:電源控制類(上電請求,使能,失能,屏蔽,狀態),錯誤控制類(錯誤狀態,使能,失能,屏蔽),電源分離類(使能,失能,屏蔽,狀態),復位控制類,以及一些其他雜七雜八的寄存器,詳細的可以查看這一章最後的Register Overview的部分。

6.2.8 PMU GPIs and GPOs

我們前面説過GPI和GPO是PMU用來與外界部件進行數據溝通的寄存器,GPI和GPO都各有4組。我感覺這裏把GPO,GPI和全局寄存器分開的原因主要是GPO和GPI針對的是MPSOC中別的模塊的請求或者控制,例如APU,RPU的上電,復位,又或者直接連接到MIO,都是針對SOC上的別的模塊的;而全局寄存器則主要保存一些全局的錯誤中斷狀態,又或者控制和監控各個電源域,大部分不是針對單個模塊的,所以把他們分開成了兩組。GPO和GPI的部件也非常的多,各4個總共8個寄存器都有不同的功能,這裏我也稍微歸納一下:GPI0和GPO0為PMU處理器專用的,具體用來幹什麼我沒看到。GPI1用來監控PS中各部件的甦醒請求,還有6個腳連接到MIO用來捕獲外部甦醒事件。GPO1這用來配置PMU的PIT以及標示PMU處理器的一些狀態。GPI2主要用來監控電源控制請求,例如APU和RPU的斷電請求和熱復位請求,還有一些和DEBUG相關的寄存器。GPO2大部分的位都被保留了,只有五個被使用的位我也沒太理解是幹嘛的,這裏就不談了。最後的GPI3和GPO3都是連接到PL的,也不説了。

6.2.9 PMU Interrupts

PMU在PMU ROM中固化了中斷向量表以及中斷優先級,而PMU處理器共有23箇中斷源(應該是一個32位的中斷狀態寄存器,有9位被保留了),這些中斷的優先級和對應的服務程序被PMU ROM所默認設置,但是也可以通過PMU Firmware來更改,從而更改優先級和向量的指向(例如指向PMU RAM),由於比較重要,我這裏還是把表貼一下:

6.2.10 PMU Error Handling and Propagation Logic PMU錯誤處理與傳播邏輯

這一節內容有關PMU處理系統運行中的錯誤,我也沒有完全看懂,所以這一節也只是大致説一下。PMU負責捕獲,報告並處理系統中的所有錯誤,為了實現對這些錯誤的捕獲,控制以及處理,PMU中有兩組寄存器來負責管理這些錯誤,一組後綴是ERROR_XXXX_1另一組是ERROR_XXXX_2,例如ERROR_STATUS_1,ERROR_STATUS_2,或者ERROR_POR_MASK_1,ERROR_POR_MASK_2,都是PMU全局寄存器的一部分。一旦這些錯誤發生就會產生中斷(但是我沒看到中斷表裏面有寫),通過配置這些全局寄存器並讀取對應寄存器的值就能夠實現對錯誤的發現和控制,而且還要注意的是一旦錯誤產生必須顯式的去給對應的error status寄存器寫1才能清除該錯誤狀態,否則即使是系統復位和內部POR都不能清除錯誤狀態。這裏還有一部分內容我不太好歸納了就偷懶貼下翻譯:

對於錯誤處理邏輯處理的每個錯誤,您可以決定在錯誤發生時應採取什麼操作。可能的情況是以下選擇之一或組合

- 在設備上斷言PS_ERROR_OUT信號。

- 生成對SAL處理器的中斷(PMU_Int)。

- 生成系統重置(SRST)。

- 生成通電重置(POR)

每個ERROR_STATUS寄存器都有四個掩碼寄存器(ERROR_STATUS_1 and ERROR_STATUS_2)。這些屏蔽寄存器可用於啓用POR, SRST, PMU中斷(如果安裝了Firmware),或發送PS_ERROR_OUT信號。要設置屏蔽,請將1寫入ERROR_INT_EN寄存器(ERROR_INT_EN_1 or ERROR_INT_EN_2)的適當位。要清除屏蔽,請將1寫入ERROR_INT_DIS寄存器((ERROR_INT_DIS_1 or ERROR_INT_DIS_2))的適當位。當選擇在發生特定錯誤時中斷PMU的選項時,應該有用户Firmware來處理錯誤。否則,將發生無實體錯誤。信號狀態可以根據需要解除屏蔽。表6-12列出了PS_ERROR_OUT器件引腳信號的所有可能的錯誤源以及ERROR_SIG_MASK_n掩碼寄存器的相應復位狀態。所有其他錯誤掩碼寄存器均設置為1(已屏蔽)。

圖我就不貼了因為實在太長了,詳情請看第123頁。

小節

PMU的內容實在太多了,這一次只是講完了PMU的構成以及剛剛部件的作用,具體的PMU到達該如何運行和使用還沒有講,我看下篇幅感覺還是留在下次講了,我們系一篇隨筆再見。